Fターム[5F038CA02]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 素子配置 (1,574)

Fターム[5F038CA02]に分類される特許

161 - 180 / 1,574

半導体装置とその製造方法、及び半導体装置の設計プログラム

【課題】半導体装置において、所望の数のトランジスタをハンドリングすること。

【解決手段】半導体装置は、半導体基板内に形成された第1導電型の第1から第4の拡散層と、半導体基板内に形成された第2導電型の第5から第8の拡散層と、第1と第2の拡散層の間及び第5と第6の拡散層の間の上方に形成された第1の電極と、第3と第4の拡散層の間及び第7と第8の拡散層の間の上方に形成された第2の電極と、第6の拡散層と第7の拡散層との間の上方に形成された絶縁膜及び第3の電極を備える。第3の電極は、第1電位に接続されている。

(もっと読む)

半導体装置

【課題】無線通信によりデータの交信を行う半導体装置において、装置を大型化することなく、アンテナの感度を向上させ、チップをノイズから保護することを課題とする。

【解決手段】コイル状のアンテナと当該コイル状のアンテナに電気的に接続された半導体集積回路とを有する。コイル状のアンテナと重なるように半導体集積回路を配置する。このように、半導体装置内のコイル状のアンテナと半導体集積回路の配置を工夫することで、装置を大型化することなく、アンテナの感度を向上させて、半導体集積回路が動作するために十分な電力を得ることができる。

(もっと読む)

半導体装置

【課題】特性をさらに向上する半導体装置を提供する。

【解決手段】高電圧側電界効果トランジスタ20aの高電圧側ドレイン電極11aと、高電圧側ドレイン電極11aの一側方に間隔をおいて形成される高電圧側ゲート電極12aと、高電圧側ゲート電極12aの一側方に間隔をおいて形成され、高電圧側電界効果トランジスタ20aのソース電極であり、低電圧側電界効果トランジスタ21aのドレイン電極であるソース兼ドレイン電極13aと、ソース兼ドレイン電極13aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ゲート電極14aと、低電圧側ゲート電極14aの一側方に間隔をおいて形成される低電圧側電界効果トランジスタ21aの低電圧側ソース電極15aとを有する。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

測定結果管理システム、管理サーバ、及び半導体集積回路装置

【課題】実際に稼動している半導体集積回路装置の実動作に影響を与える要因を解析し、更にその要因を低減することが可能な半導体集積回路装置を提供する。

【解決手段】測定対象である半導体集積回路131と、この半導体集積回路のジッタ又はノイズジッタ、ノイズ等の実動作に影響を与える物理量を測定する測定回路(半導体集積回路装置)130とを同一チップ上に構成する。測定回路の測定結果を解析し、測定対象の半導体集積回路を調整する回路にフィードバックさせる。

(もっと読む)

未知の半導体装置の機能の非破壊的な決定

【課題】外部放射線に対して応答する接合を分析することを通して機能を推測することによる、集積回路の非破壊的なリバースエンジニアリングのためのシステム及び技術を提供する。

【解決手段】少なくとも1つの電源と電気的に導通している複数の半導体接合を含む半導体装置の機能を決定するための以下を含む方法。

・半導体装置の表面を照射すること;

・照射に応答する複数の半導体接合のうち少なくとも幾つかのレイアウトを決定すること;

・決定されたレイアウト内で、複数の半導体接合の少なくとも幾つかのグルーピングを同定し、各ブルーピングはそれぞれの機能セルを表すこと;

・複数の外部アクセス可能な接点のうち少なくとも1つへの刺激を変化させること;及び

・前記変化した刺激に応答して複数の相互接続された機能セルの1つ以上の接続を推測すること。

(もっと読む)

有機抵抗による基準電圧発生回路、それを備えたA/D変換回路

【課題】アナログオプション回路を備えた半導体集積回路(A/D変換)を構成する抵抗を、簡便かつ大面積を専有されることなく作成する製造方法、及びその製造方法により作成されるAD変換回路を提供する。

【解決手段】高電源の電圧と低電源の電圧との間に直列に接続された複数個の抵抗からなるストリング抵抗を備えた基準電圧発生部と、入力アナログ電圧値と前記抵抗間の接続点の分圧電圧値とを比較する電圧比較部とを含むA/D変換回路において、

前記抵抗が有機材料で形成されていることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置を小型化することを課題の一とする。また、記憶素子を有する半導体装置の駆動回路の面積を縮小することを課題の一とする。

【解決手段】入力端子と出力端子の位置が固定された複数のセルを第1の方向に配置し、各セルの入力端子および出力端子とそれぞれ電気的に接続される配線を複数のセル上に積層させ、且つ、その配線の延在方向をセルが並べられた第1の方向と同方向とすることで、駆動回路の小型化を図った半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲート電極を備えるトレンチゲート構成のパワーMISFETにおいて、MISFETの性能向上を図りながら、ゲート絶縁膜の静電破壊を防止することができる技術を提供する。

【解決手段】ダミーゲート電極9aを備えるトレンチゲート構成のパワーMISFETと保護ダイオードとを同一の半導体基板1上に形成する。そして、保護ダイオードをソース電極24とゲート配線25の間に設ける。このような半導体装置の製造方法において、ダミーゲート電極9a用のポリシリコン膜と保護ダイオード用のポリシリコン膜を同時に形成する。また、パワーMISFETのソース領域と保護ダイオードのn+型半導体領域15を同一工程で形成する。

(もっと読む)

制御電圧生成回路、定電流源回路及びそれらを有する遅延回路、論理回路

【課題】回路規模を増大させることなくトランジスタの閾値電圧に応じた制御電圧を精度良く生成することが可能な制御電圧生成回路を提供すること。

【解決手段】本発明にかかる制御電圧生成回路は、高電位側電源と低電位側電源との間に直列に接続された同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのドレイン電圧を参照電圧Vp1として生成する参照電圧生成部11と、高電位側電源と低電位側電源との間に直列に接続され参照電圧生成部11と同一導電型の複数のMOSトランジスタを有し、何れかのMOSトランジスタのゲートに参照電圧が供給され、何れかのMOSトランジスタのドレイン電圧を制御電圧(バイアス電圧)として出力する電圧変換部12と、を備える。

(もっと読む)

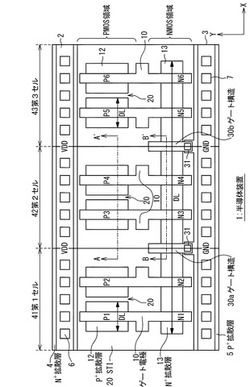

半導体集積回路

【課題】動作特性を劣化させることなくセル面積の縮小化を図ったマクロセル構造の半導体集積回路を得る。

【解決手段】Pウェル領域1の中央部にNウェル領域2が形成される。Nウェル領域2の平面視上方及び下方にN活性領域4a及び4bが形成される。Pウェル領域1内においてN活性領域4aの平面視上方及び下方にPウェルコンタクト領域5a及び5bが横方向に延びて形成される。Nウェル領域2内において中央にP活性領域3が形成され、P活性領域3の左横に縦方向に延びてNウェルコンタクト領域6が形成される。P活性領域3の中心部を横断するVDD用メタル配線層14の一部であるウェルコンタクト部14cは、Nウェルコンタクト領域6上にも形成され、ウェルコンタクト部14cとNウェルコンタクト領域6とは複数のコンタクトホール21を介して電気的に接続される。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

保護装置

【課題】 差動信号ラインに、第1入力端子と第2入力端子を有し、ダイオードにより構成される1パッケージの保護装置を接続する場合、第1入力端子と第2入力端子間のアイソレーションを十分確保し、また、第1入力端子に接続するダイオードと第2入力端子に接続するダイオードの部品ばらつきを抑制する必要がある。また、差動信号ラインに用いる保護装置の場合、部品容量とESD破壊耐量を所望の範囲に収めるようにする必要がある。

【解決手段】 p半導体基板上にp型半導体層を積層し、その表面にpn接合を形成し、互いに離間する第1n+型不純物領域、第2n+型不純物領域、第3n+型不純物領域を設け、第1入力端子に接続する第1n+型不純物領域と、第2入力端子に接続する第3n+型不純物領域との間に、接地端子に接続する第2n+型不純物領域を配置して、横型の双方向pn接合ダイオードによる保護装置を提供する。

(もっと読む)

テストエレメントグループおよび半導体装置

【課題】保護ダイオードの有無に拘らず、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】テストエレメントグループ10において、電界効果型トランジスタからなるn個の素子DUT1〜DUTnが規則的に配置されている。ドレイン線DLおよびソース線SLがそれぞれ、全ての素子DUT1〜DUTnに対して共通化されており、その一方で、ウェル線WLが素子DUT1〜DUTnごとに1つずつ設けられている。選択対象の素子(選択素子DUTx)の素子特性を測定する際には、基板バイアス効果を利用して、非選択対象の素子(非選択素子DUTy)に流れるオフリーク電流を小さくする。

(もっと読む)

半導体装置の検査方法、半導体装置および半導体基板

【課題】半導体装置の小型化を図りつつ、正確な故障箇所の位置の特定を可能とする。

【解決手段】半導体基板10の他面に溝部を形成する工程と、部品20と溝部の位置関係を示すレイアウトデータを取得する工程と、部品20に電圧を印加することにより、部品20の故障箇所50を発光させるとともに、故障箇所50からの発光を溝部の内部へ伝播させる工程と、故障箇所50からの発光により生じる第1の発光部の位置、および故障箇所50からの発光が溝部の内部を伝播することによって生じる第2の発光部の位置を他面側から検出する工程と、第1の発光部の位置および第2の発光部の位置から、溝部の位置を推定する工程と、推定した溝部の位置に対する第1の発光部の相対位置と、レイアウトデータにおける溝部の位置とを用いて、故障箇所を特定する工程と、を備える。

(もっと読む)

半導体装置及びそのレイアウト方法

【課題】再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、パッケージング工程の前後での素子の特性変動を低減させる。

【解決手段】素子が形成された半導体基板に対して、再配線層形成工程、メタルポスト形成工程及び樹脂封止工程を経てウェハレベルで樹脂封止される半導体装置について、上方から見てメタルポスト21の周縁と重なる位置に素子33,35,37を配置しないようにする。また、製造時におけるメタルポスト21に起因して生じる応力の影響を受ける、メタルポスト21の周縁から所定の範囲に素子の配置禁止領域21aを設け、配置禁止領域21aに素子33,35,37を配置しないようにする。

(もっと読む)

電力増幅器

【課題】 電力増幅器に発生するホットキャリアの影響を抑制する。

【解決手段】 一つの実施形態の電力増幅器には、半導体層に形成され、少なくとも1つ以上から構成され、電力増幅動作する第1のグロースリングゲート構造体と、半導体層に形成され、第1のグロースリングゲート構造体を取り囲むように隣接配置され、第1の構造体が電力増幅動作するときに、逆バイアスが印加されて空乏化領域が形成され、第1の構造体を周囲からアイソレートする複数の第2のグロースリングゲート構造体とが設けられる。

(もっと読む)

異物検出用パターン及び半導体装置

【課題】異物の種類によらずに高効率で異物の存在を検査しうる異物検出用パターン、並びにこのような異物検出用パターンを有する半導体装置を提供する。

【解決手段】基板上に形成された複数の角部を除いたL字型パターンを有し、複数の角部を除いたL字型パターンは、除いた前記角部の位置が直線上に並ぶように離間して配置されている。

(もっと読む)

半導体装置

【課題】高い比精度が要求される複数のトランジスタの特性ばらつきを低減する。

【解決手段】本発明の半導体装置は、半導体基板上に配置されたトランジスタTr1と、半導体基板上で見たキャリアのドリフト方向がトランジスタTr1のキャリアのドリフト方向と同じ方向となる向きに配置されたトランジスタTr2と、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51b同士を接続する拡散層51cと、トランジスタTr1,Tr2のキャリア供給側の拡散層51a,51bまたはその拡散層同士を接続する拡散層51cの表面に接続され、拡散層51a,51bに給電するためのコンタクトプラグ61と、を備える。

(もっと読む)

半導体装置

【課題】トレンチゲート型パワーMOSFETのゲート電極の微細化に伴って、トレンチ底部の曲率が大きくなり、その部分に電界が集中し、ゲート酸化膜(絶縁膜)の劣化が起きる。このゲート絶縁膜の劣化は、Nチャネル型パワーMOSFETの場合、ゲート側バイアスが負である場合に起こりやすく、Pチャネル型パワーMOSFETの場合、ゲート側バイアスが正である場合に起こりやすい。

【解決手段】本願発明は、絶縁ゲート型パワー系トランジスタ等をチップ内に具備する半導体装置であって、ゲート保護素子は双方向ツェナーダイオードを具備し、前記双方向ツェナーダイオードは、そのゲート側がマイナスバイアスされたときの耐圧と、そのゲート側がプラスバイアスされたときの耐圧とは相互に異なるように、複数の濃度の異なるP型不純物領域(またはP型不純物領域)を有する。

(もっと読む)

161 - 180 / 1,574

[ Back to top ]