Fターム[5F038CA02]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 素子配置 (1,574)

Fターム[5F038CA02]に分類される特許

81 - 100 / 1,574

ブートストラップ回路、インバータ回路、走査回路、表示装置、及び、電子機器

【課題】ブートストラップゲインの上昇を可能にしたブートストラップ回路、当該ブートストラップ回路を用いたインバータ回路、当該インバータ回路を用いた走査回路、当該走査回路を用いた表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】トランジスタと、当該トランジスタの一方のゲート電極とソース/ドレイン領域との間に接続された容量とを有し、当該一方のソース/ドレイン領域の電位の変動に応じてゲート電極の電位が変動するブートストラップ動作を行うブートストラップ回路において、トランジスタについて、ゲート電極の中心を通る線に関してソース領域とドレイン領域とを非対称な構造にする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ESD耐量を向上させたLDMOSFETを備える半導体装置を提供する。

【解決手段】半導体層200よりも高濃度のP型の押込拡散領域440は、半導体層200の表層から底面まで設けられている。押込拡散領域440よりも低濃度のP型の第1ウェル領域300は、半導体層200に、平面視で一部が押込拡散領域440と重なるように設けられている。N型のドレインオフセット領域540は、半導体層200に、平面視で第1ウェル領域300と接するように設けられている。ドレインオフセット領域540よりも高濃度のN+型のドレイン領域520は、ドレインオフセット領域540内に設けられている。ドレインオフセット領域540よりも高濃度のN型の第2ウェル領域560は、半導体層200のうち、ドレインオフセット領域540の下に位置して、平面視でドレイン領域520と重なる領域に設けられている。

(もっと読む)

半導体装置

【課題】半導体基板に半導体素子と内部回路とが設けられた半導体装置において、半導体素子及び内部回路の各温度を検出するセンサを効率的に配置してレイアウトの自由度を高めることができ、且つ半導体素子及び内部回路の各温度をより正確に検出し得る構成を提供することを目的とする。

【解決手段】半導体基板5の一方面側に、スイッチング素子20と、このスイッチング素子20の配置領域から距離を隔てて内部回路30が配置されている。また、スイッチング素子20に隣接して、周囲に第1絶縁膜27が形成された第1温度検出素子24が設けられている。さらに、内部回路30よりもスイッチング素子20に近い側に、周囲に第2絶縁膜28が形成された第2温度検出素子25が設けられている。そして、第2絶縁膜28の厚さが第1絶縁膜27の厚さよりも大きくなるように構成されている。

(もっと読む)

半導体集積回路

【課題】フリップフロップにおけるアクティブ領域のレイアウトの凹凸を低減する。

【解決手段】半導体チップには、クロック領域CR1、ラッチ領域LR1およびバッファ領域BR1が設けられ、クロック領域CR1にはアクティブ領域AK5、AK6が形成され、ラッチ領域LR1にはアクティブ領域AK1、AK2が形成され、バッファ領域BR1にはアクティブ領域AK3、AK4が形成され、アクティブ領域AK1〜AK6の幅をそれぞれにおいて均一の幅として分割されている。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】放熱性と耐久性に優れた半導体装置およびその製造方法を提供する。

【解決手段】導電ベースプレートと、導電ベースプレート上に接合される半導体チップと、半導体チップと導電ベースプレートとの接合面の中央部に配置された第1接着剤と、半導体チップと導電ベースプレートとの接合面の周辺部に配置された第2接着剤とを備え、第1接着剤は第2接着剤よりも相対的に熱伝導率が高く、第2接着剤は第1接着剤より相対的に接合力が高い半導体装置。

(もっと読む)

半導体装置

【課題】パッドの下方に半導体素子を設けることができ、信頼性の高い半導体装置を提供する。

【解決手段】素子形成領域10Aと該素子形成領域10Aの周囲に設けられた素子分離領域20とを有する半導体層10と、前記素子形成領域10A内に形成された素子30と、前記半導体層10の上方に設けられた層間絶縁層60と、前記層間絶縁層60の上方に設けられ、平面形状が短辺と長辺とを有する長方形である電極パッド62であって、前記素子30と平面視で少なくとも一部が重複する前記電極パッド62と、を含み、前記半導体層10において、前記電極パッド62の前記短辺の鉛直下方から外側に位置する所定の範囲は、素子禁止領域12である。

(もっと読む)

ガードバンドセル及びガードバンド

【課題】電源供給が遮断されるIO領域が存在する場合でも、ランダムロジック領域内でのラッチアップの発生を防止するガードバンドセル及びガードバンドを提供すること。

【解決手段】本発明の一態様に係るガードバンドセル11は、NウェルNW1を有する。また、本発明の一態様に係るガードバンドセル11は、NウェルNW1の上に形成された、Nウェル層と同じ導電型であるN型ガードバンド拡散層NGB1を有する。N型ガードバンド拡散層NGB1は、十分な低抵抗の配線により、ランダムロジック領域2の電源電位と接続される。

(もっと読む)

温度測定装置、温度校正装置及び温度校正方法

【課題】熱処理機構を用いて基板を所定の温度に熱処理する熱処理装置において、前記熱処理機構の温度を簡易な方法で適切に校正する。

【解決手段】温度校正装置の温度検査治具10は、熱処理板上に載置される被処理ウェハ70と、被処理ウェハ70上に設けられた複数のホイートストンブリッジ回路71とを有している。ホイートストンブリッジ回路71は、温度変化に応じて抵抗値が変化する4つの測温抵抗体72と、接触子41が接触する4つのコンタクトパッド73と有している。温度校正装置の制御部では、ホイートストンブリッジ回路71が平衡状態となるように、すなわちホイートストンブリッジ回路71のオフセット電圧がゼロになるように、熱処理板の温度を調節する。

(もっと読む)

電力増幅器

【課題】MMICとMMIC外部回路とを接続するボンディングワイヤの影響を比較的簡単な構成で低減し、かつ省スペース化された電力増幅器を提供する。

【解決手段】MMIC基板と、MMIC基板上に配置された高周波プローブパッドと、MMIC基板上に高周波プローブパッドに隣接して配置され、MMIC外部回路とのボンディングワイヤ接続用のメタルプレートとを備える。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、レイアウトの面積効率の低下を抑制可能となる、マルチハイトセルのレイアウト構造を提供する。

【解決手段】標準論理セル10は、電源配線または接地配線となるメタル配線12を共有するようにY方向に隣接して配置された第1および第2回路領域A1,A2を備えている。X方向において、第1回路領域A1の両端部の位置x1a,x1bと第2回路領域A2の両端部の位置x2a,x2bとは、少なくともいずれか一方が異なっている。すなわち、標準論理セル10の外形形状CFは、第1および第2回路領域A1,A2の外形形状が矩形であるにもかかわらず、非矩形となっている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGによる検査結果を容易に確認できるようにしつつ、TEGの占有面積を小さくする。

【解決手段】TEG群300は、第1テスト用パッド310、第2テスト用パッド312、及び複数のTEG(例えば第1TEG320、第2TEG340、及び第3TEG360)を有している。複数のTEGは、電気回路上、第1テスト用パッド310と第2テスト用パッド312の間に位置し、互いに直列又は並列に配置されており、かつ平面視で互いに重なっていない。本実施形態において、TEG群300を構成するTEGは、OBRICH(Optical Beam Induced Resistance Change)用のTEGである。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

半導体装置

【課題】複数のスパイラルを直列に接続してインダクタを形成する場合において、スパイラルを大面積化することなく、スパイラルの巻線を長くする。

【解決手段】インダクタ10は、第1スパイラル100及び第2スパイラル200を有している。第1スパイラル100は、インダクタ10の巻軸と平行な第1の方向から見た場合、中心から外側に向かって巻かれている。第2スパイラル200は、第1の方向から見た場合、外側から中心に向かって、第1スパイラル100と同一の向きに巻かれている。第1スパイラル100及び第2スパイラル200は、外側の端部同士、または中心側の端部同士が、外側接続部材300又は中心側接続部材400を介して接続されている。第2スパイラル200は、第1スパイラル100を、巻軸を回転中心として右回りに90°回転させてから、巻軸に直交する平面に含まれる水平線を基準に鏡映させ、かつ縦横比を変更した形状である。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタを備え、バイアホールを必須とせず、小さなチップサイズにおいても大きなキャパシタ容量を実現することができ、MIMキャパシタの内部電極と外部電極の電位の設定自由度が高い半導体装置を提供する。

【解決手段】半導体装置2は、半導体チップ10と、半導体チップ10の表面10Tに形成された電子回路と、半導体チップ10の少なくとも1つの側面10L、10Rに形成され、半導体チップ10側から内部電極21と絶縁膜22と外部電極23との積層構造を有するMIMキャパシタ20とを備えている。半導体装置2は、半導体チップ10の表面10T上から側面10L、10Rに形成されたMIMキャパシタ20上に平面的に延びて、MIMキャパシタ20の内部電極21に接触した表面電極30を備えている。

(もっと読む)

半導体集積回路装置

【課題】セル高さが低減した場合であっても、容量セルの容量値を十分に確保可能なレイアウト構成を提供する。

【解決手段】第1の電源電圧を供給する電源配線11が第1の方向に延びており、電源配線11と平行に、第2の電源電圧を供給する電源配線12および第3の電源電圧を供給する電源配線13が延びている。容量素子16は、ソースおよびドレインに第1の電源電圧が与えられ、ゲートに第2または第3の電源電圧が与えられるトランジスタによって構成されている。容量素子16は電源配線11の下に、電源配線12側の領域から電源配線13側の領域にわたって形成されている。

(もっと読む)

データ保持装置及びこれを用いた論理演算回路

【課題】マスクパターンの疎密に起因する強誘電体素子の特性ばらつきを適切に低減することが可能なデータ保持装置及び、これを用いた論理演算回路の提供。

【解決手段】データ保持装置において、不揮発性記憶部に含まれる複数の強誘電体素子X(素子幅m)は、各々よりも素子幅の小さいダミー素子Y(素子幅n、ただしn<m)によって包囲されている。これによってマスクパターンの疎密に起因するエッチングのローディング効果を抑制する事が可能となる。

(もっと読む)

半導体装置

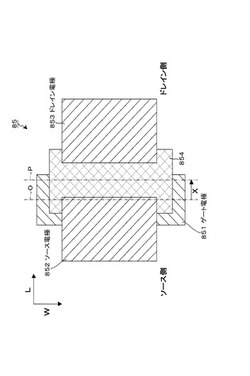

【課題】安定したボディ固定動作と共に、高集積化、低寄生容量化や配線容量の低減化を図ることができる、SOI基板上に形成される半導体装置を得る。

【解決手段】ソース領域1,ドレイン領域2及びゲート電極3で形成されるMOSトランジスタにおいて、ゲート一端領域及びゲート他端領域に部分分離領域11a及び11bが形成され、部分分離領域11aに隣接してタップ領域21aが形成され、部分分離領域11bに隣接してタップ領域21bが形成される。部分分離領域11a,11b、タップ領域21a,21b及び活性領域1,2の周辺領域は全て完全分離領域10が形成される。

(もっと読む)

半導体ウェハ、半導体装置、及び半導体装置の製造方法

【課題】ヒューズメモリを利用したトリミングを行う半導体ウェハにおける各半導体チップの回路面積を小さくする。

【解決手段】半導体ウェハ10におけるシリコン基板上は、複数個のチップ領域TARとこの領域TARを囲むスクライブ領域SARとに区画されている。チップ領域TARには、トリミング対象回路11と、ヒューズ素子Fm(m=1〜2M)と、ヒューズ素子Fm(m=1〜2M)が断線状態であるか否かを検出する検出回路としての役割を果たす定電流源IPm(m=1〜2M)及びインバータINm(m=1〜2M)とが形成されている。スクライブ領域SARには、制御信号に応じてON/OFFが切り換わり、ONとなることによりヒューズ素子Fm(m=1〜2M)を断線させる電流を発生するNチャネル電界効果トランジスタTSm(m=1〜2M)がある。

(もっと読む)

半導体装置及び出力回路

【課題】半導体装置の出力回路における試験時間を短縮する。

【解決手段】出力端子9に複数並列に接続されるpMOS2−1〜2−4、nMOS3−1〜3−4において、各ゲート電極11〜26の一端に、選択されるドライブ能力に応じた制御信号が伝搬される制御信号線P1〜P4,N1〜N4を接続し、他端に試験配線OP1〜OP4,ON1〜ON4を接続する。これにより、試験配線OP1〜OP4,ON1〜ON4の信号から、ドライブ能力の切り換えが可能なように回路パターンが形成されているか検査でき、各ドライブ能力に対応する電流負荷を全てテスタで設定して試験するより、試験時間を短縮できる。

(もっと読む)

81 - 100 / 1,574

[ Back to top ]