Fターム[5F038CA02]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 素子配置 (1,574)

Fターム[5F038CA02]に分類される特許

41 - 60 / 1,574

半導体装置

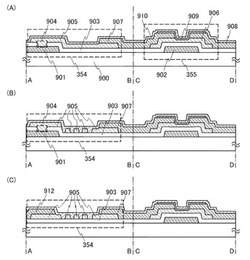

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

半導体装置及び分圧回路

【課題】複数の抵抗の変化率差を抑制すること。

【解決手段】分圧回路11は、直列接続された2つの抵抗R1,R2を有している。第1の抵抗R1は、入力電圧Vinを供給する配線21と出力ノードN1との間に接続されている。第2の抵抗R2は、基準電圧Vsを供給する配線22と出力ノードN1との間に接続されている。第1の抵抗R1は、P型の半導体基板に形成されたN型のウェル領域(基板領域)31と、このウェル領域31に形成されたP型の拡散領域33を含む。第2の抵抗R2は、P型の半導体基板に形成されたN型のウェル領域32と、このウェル領域32に形成されたP型の拡散領域34を含む。第1のウェル領域31には、入力電圧Vinが供給される。第2のウェル領域32は、第1の拡散領域33に設定された分圧ノードNdと接続されている。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

ニューロンCMOS回路及びニューロンCMOS回路を備える電子回路

【課題】フローティングゲート−基板間容量の影響を抑制し、高度な閾値の制御を実現するニューロンCMOS回路を提供する。また、そのようなニューロンCMOS回路を備える電子回路を提供する。

【解決手段】本発明の一実施形態によると、基板に形成され、CMOS回路を構成し、共通するフローティングゲート及び複数の入力ゲートを有するPMOSFET及びNMOSFETを有し、前記共通するフローティングゲートと前記基板との間の容量は、前記複数の入力ゲートのうちの一つの入力ゲート電極と前記共通するフローティングゲートとの間の容量と概略等しいことを特徴とするニューロンCMOS回路が提供される。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

保護ダイオード及びこれを備えた半導体装置

【課題】PN接合容量が小さい保護ダイオード及びこれを備えた半導体装置を提供する。

【解決手段】

第1領域と当該第1領域を囲う第2領域と当該第2領域を囲う第3領域とを備える半導体基板と、当該第2領域と当該第3領域との間に設けられた第1絶縁層と、当該第3領域に設けられた第1導電型半導体と、当該第2領域に設けられた第2導電型半導体と、当該第1領域に設けられた容量緩和層と、を備えている保護ダイオード。当該保護ダイオードと、これに接続された第1のパッドと、当該容量緩和層を有しない構造の保護ダイオードと、これに接続された第2のパッドと、を備えている半導体装置。

(もっと読む)

R−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法

【課題】抵抗Rと抵抗2Rとの抵抗比を1:2に近付けることにより、D/A変換精度の悪化を抑制することを可能にするR−2Rラダー抵抗回路、そのR−2Rラダー抵抗回路を備えるD/A変換器及びR−2Rラダー抵抗回路の製造方法を提供すること

【解決手段】本発明にかかるR−2Rラダー抵抗回路10は、1ビットに対応する抵抗値Rの第1抵抗及び抵抗値2Rの第2抵抗を備える。第1抵抗及び第2抵抗は、1列に並んでいる複数の単位抵抗により構成される。R−2Rラダー抵抗回路10は、前記複数の単位抵抗が並設されて構成されており、第1抵抗に含まれる単位抵抗131がR−2Rラダー抵抗回路10の一端に配置され、単位抵抗131と第1抵抗に含まれる単位抵抗132との間に第2抵抗に含まれる単位抵抗121〜124が配置されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

半導体集積回路

【課題】SOI型の半導体集積回路において電源遮断時の低消費電力及び電源供給時の動作性能向上に資することができる電源遮断制御を可能にする。

【解決手段】本発明に係る半導体集積回路は、第1電源スイッチと、前記第1電源スイッチに直列接続される論理回路を有する。前記論理回路は、順序回路(FF1,FF2)及び組み合わせ回路(LOG1,LOG2)を含み、前記第1電源スイッチと前記組み合わせ回路との間に第2電源スイッチが接続される。第1モードにおいて前記第1電源スイッチをオフ状態に制御し、前記順序回路及び前記組み合わせ回路を非通電状態にし、第2モードにおいて前記第1電源スイッチをオン状態に維持し且つ前記第2電源スイッチをオフ状態に制御し、前記順序回路を通電状態、前記組み合わせ回路を非通電状態にする電源スイッチ制御回路を有する。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

半導体装置

【課題】複数の回路ブロックの特性を正確に一致させる。

【解決手段】例えば、端子31A,31Bと、これら端子間に設けられた回路110A,110Bを備える。回路110Aは端子31Aに接続され、端子31Aから端子31Bへ向かって配置されたセル120A,130A,140Aを含む。回路110Bは端子31Bに接続され、端子31Bから端子31Aへ向かって配置されたセル120B,130B,140Bを含む。セル120A,120Bのレイアウトは、形状、サイズ及び向きがトランジスタレベルで同一である。セル130A,130B及びセル140A,140Bのレイアウトは、形状及びサイズが同一であり、トランジスタの向きが180°相違している。これにより各セルを対称配置しつつ、センシティブなセル120A,120Bにおいては電流方向の違いによる特性差が生じない。

(もっと読む)

41 - 60 / 1,574

[ Back to top ]