Fターム[5F038CD13]の内容

Fターム[5F038CD13]の下位に属するFターム

容量付加安定化 (354)

Fターム[5F038CD13]に分類される特許

61 - 80 / 506

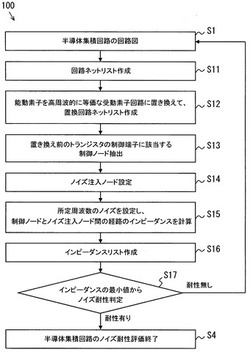

半導体集積回路のノイズ耐性評価方法およびノイズ耐性評価装置

【課題】大規模な半導体集積回路であってもノイズ耐性評価が短時間で可能なノイズ耐性評価方法を提供する。

【解決手段】回路ネットリストを作成する第1のステップS11と、能動素子を受動素子回路に置き換えて置換回路ネットリストを作成する第2のステップS12と、トランジスタの制御端子に該当する制御ノードを抽出する第3のステップS13と、ノイズ注入ノードを設定する第4のステップS14と、所定周波数のノイズを設定し、互いに異なる制御ノードとノイズ注入ノード間の経路のインピーダンスを計算する第5のステップS15と、制御ノード、ノイズ注入ノードおよび経路の各組み合わせにおけるインピーダンスのリストを作成する第6のステップS16と、インピーダンスの最小値から半導体集積回路のノイズ耐性を判定する第7のステップS17とを有してなるノイズ耐性評価方法100とする。

(もっと読む)

コプレーナ線路のエアブリッジ構造

【課題】コプレーナ線路の信号線路とエアブリッジとの交差容量の影響を抑制しつつ、複数のエアブリッジを容易に使用できるようにする。

【解決手段】エアブリッジ構造100のうち、下層配線層8に、接地線路2A,2Bのうち信号線路1を挟んで互いに対向する位置を切り欠いて形成した空孔領域12A,12Bをそれぞれ設けるとともに、上層配線層7に、空孔領域12Aの上部位置に下層配線層8の接地線路2Aと電気的に接続された上層接地電極13Aと、空孔領域12Bの上部位置に下層配線層8の接地線路2Bと電気的に接続された上層接地電極13Bとを設け、エアブリッジ3で、上層接地電極13A,13Bを介して接地線路2A,2B間を電気的に接続する。

(もっと読む)

半導体装置

【課題】超高周波帯におけるシリコン基板による損失を低減すると共に、貫通配線のインダクタンス成分の影響を小さくした半導体装置を実現できるようにする。

【解決手段】半導体装置は、回路素子105が形成された半導体基板100と、半導体基板100の主面の上に形成された第1の誘電体層121と、第1の誘電体層121の上に形成された第2の誘電体層131と、第1の誘電体層121を貫通し、回路素子105と接続された第1の貫通配線122と、第2の誘電体層131を貫通し、第1の貫通配線122と接続された第2の貫通配線132とを備えている。第2の貫通配線132は、第1の貫通配線132よりもインダクタンスが小さい。

(もっと読む)

周波数特性の調整方法、半導体装置の製造方法及び半導体装置

【課題】寄生容量が回避できないSi半導体基板上に集積回路と一緒に製造するオンチップアンテナにおいて、その周波数特性をウエハプロセス製造工程後に自在に所望値へ制御する。

【解決手段】Si半導体基板に対して第1のプロセスで形成される集積回路部及びアンテナ部を備える半導体装置において、該アンテナ部の周波数特性を調整する方法であって、アンテナ部と集積回路部との間に非連続的な複数の導線パターンを前記第1のプロセスにおいて形成し、第1のプロセスの終了後に、複数の導線パターンの一部又は全部を選択して、選択した前記導線パターンが直列的となるようにボンディングワイヤを懸架する。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出する精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に形成された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンに接続され、導電パターンの回路定数により決定される発振周波数で発振する発振回路と、発振回路の発振周波数が事前に設定された範囲に含まれるか否かを判定し、発振周波数が事前に設定された範囲に含まれない場合に、導電パターンに改変が加えられたことを検出する検出回路とを有することを特徴とする半導体集積回路装置が提供される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】入出力端子と半導体スイッチとの間を接続する配線同士が交差する箇所が発生しても、端子間のアイソレーション特性を向上させつつ、サイズ及びコストを抑制可能な半導体装置を提供する。

【解決手段】半導体スイッチ回路(20)は、複数の入力端子(31,32)のうち任意の入力端子を配線層(51)又は再配線層(251)を介して複数の出力端子(41〜44)のうち任意の出力端子と接続させるように構成される。複数の入力端子及び複数の出力端子のうち、ある端子と半導体スイッチ回路との間を接続する配線と、他の端子と半導体スイッチ回路との間を接続する配線とが交差している箇所において、交差する配線のうち、一方の配線を配線層とし、他方の配線を再配線層とする。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

可変インダクタ及びこれを用いた半導体装置

【課題】インダクタの近傍に形成されたループ状導体の開放端を、スイッチによって開放又は短絡させて、インダクタンスが可変とされ安定なインダクタンスを生成できる可変インダクタ及びこれを用いた半導体装置を提供する。

【解決手段】半導体装置は、それぞれ、半導体基板上に形成されたインダクタ10と、スイッチ16が接続された開放端を有し、インダクタ10の近傍に形成されたループ状導体20とを有する第1のセットおよび第2のセットを有する。2つのセットはそれぞれ、スイッチ16による開放端の開放又は短絡によって、インダクタンスが可変とされ、ループ状導体20がインダクタ10に接続された信号回路13の入力および半導体基板と共通の接地レベルに接続されると共に、第1のセットのループ状導体20と第2のセットのループ状導体20との間に相互磁気誘導が発生し得る位置に、第1のセットと第2のセットとが設けられている。

(もっと読む)

モータ制御用半導体装置

【課題】モータ制御用半導体装置に対するコンタクト用ピンからの影響を低減する

【解決手段】ホール素子102からの出力のオフセット電圧を取り除くオフセットキャンセル回路104に含まれるオシレータ回路12と、オフセットキャンセル回路104からの出力信号を受けて、当該出力信号と基準信号とを比較して比較信号を生成して出力するコンパレータ回路106と、モータを駆動するための駆動信号を生成して出力する出力回路110と、モータの制御に関係しないテスト回路112と、を有し、オシレータ回路12の回路パターン上、コンパレータ回路106の回路パターン上、及び、テスト回路112の回路パターン上のいずれか1つに重なるようにパルス幅変調信号の入出力パッドP1を形成する。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

保護回路および半導体装置

【課題】小面積で、ESD強度を向上させた保護回路を提供する。

【解決手段】接地電位線から電源電圧線への方向が電流の順方向となる第1のダイオードと、接地電位線から信号線への方向が電流の順方向となる第2のダイオードと、接地電位線から電源電圧線への方向が電流の順方向となる第3のダイオードと、信号線から電源電圧線への方向が電流の順方向となる第4のダイオードと、を有する。第1および第2のダイオードは、接地電位線に接続された第1の拡散層を共有し、第3および第4のダイオードは、電源電圧線に接続された、第1の拡散層とは異種の導電性の第2の拡散層を共有している構成である。

(もっと読む)

スイッチ回路装置

【課題】従来技術によるスイッチ回路装置では、ドライバ回路がアンテナ端子とポートとの間に振幅の大きい高周波信号を入力した際に、ドライバ回路内部でリーク電流が発生し、スイッチ回路装置の消費電力が増大する、という問題がある。

【解決手段】ドライバ回路の出力部に、リーク電流抑制回路部を設ける。本発明のスイッチ回路装置によれば、リーク電流抑制回路部が高周波信号の侵入を抑制するので、ドライバ回路は出力状態を保持することが出来て、リーク電流の問題が解決される。

(もっと読む)

半導体集積回路

【課題】電源遮断時に、電源遮断対象ブロックへの電源配線を有効に活用することのできる半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1の電源パッドと、第2の電源パッドと、第1の電源パッドに接続された第1の電源配線と、第2の電源パッドに接続された第2の電源配線と、を備え、第1のスイッチを介して第1の電源配線に接続される電源遮断対象ブロックと、第2の電源配線に接続される常時電源供給対象ブロックと、第1の電源配線と第2の電源配線との間に接続された第2のスイッチと、を備える。

(もっと読む)

MEMS装置

【課題】基板とMEMS素子との間の寄生容量、および基板の反りを抑えたMEMS装置を提供する。

【解決手段】

実施の形態のMEMS装置は、表面に開口する凹部と凹部内に、絶縁物、エアギャップ、または絶縁物およびエアギャップが形成された基板と、基板上の絶縁層と、絶縁層上に形成された信号線を有するMEMS素子とを有し、上記基板の表面に平行な方向の信号線の位置と上記平行な方向の凹部の位置に重なりがある。

(もっと読む)

半導体装置

【課題】外部ループバックテストが容易な半導体装置を提供する。

【解決手段】主面に形成された格子状のダイシングライン14、15と、ダイシングライン14、15で囲まれた矩形状格子に形成され、信号出力パッド24有する送信回路22と、信号入力パッド25を有する受信回路23と、送信回路22および受信回路23に入出力されるデータを処理する内部回路21とを有する複数の集積回路12と、ダイシングライン14、15上に形成され、信号出力パッド24と信号入力パッド25間を電気的に接続する信号配線26とを具備する。

(もっと読む)

半導体装置

【課題】コモンノイズを低減する。

【解決手段】半導体装置10は、直列に接続された半導体スイッチング素子11,12と、正極端子13と、負極端子14と、出力端子15とを具備する半導体モジュール16と、半導体モジュール16に絶縁されたボディ17とを備える。ボディ17と各端子13,14との間の各浮遊容量C1,C3に対して、出力端子15とボディ17との間で、出力端子15の浮遊容量C2と浮遊容量C1とが直列接続または出力端子15の浮遊容量C2と浮遊容量C3とが直列接続になるようにして、各端子13,14,15が配置されている。

(もっと読む)

半導体集積回路装置

【課題】制御信号の系統を整理して、不定信号伝播防止回路等の検討漏れの危険性を回避し、さらに、自動化ツールへの搭載へ向けた検討を容易にし、また、チップ内部での電源遮断制御を容易化することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、各独立した電源領域AreaA〜AreaIごとに電源遮断の優先順を設け、優先順の高い回路がONしている場合にはそれより優先順の低い電源領域はOFFにできないという規則を設けて、設計方法の容易化を図る。また、各独立した電源領域AreaA〜AreaI内において、さらに別の電源を印加できる領域を設け、その領域に中継バッファ(リピータ)やクロックバッファ、情報退避用の情報保持ラッチを集積する。レイアウト上は、電源線の電流を分散させる目的でセルがロウ方向に並ぶ方向と垂直な方向にまとめてレイアウトすればよい。

(もっと読む)

半導体集積回路

【課題】セル内のメタル配線幅を、設計上許容すべき最大駆動容量Cmax未満の配線幅に設定して、セル内の容量を削減し、セル相互間距離が非常に近い回路などにおいて伝播遅延を所定時間以下に設計することができるようにする。

【解決手段】配線幅以外は全て同一のレイアウトパターンを備えた2種類のスタンダードセル101、151が用意される。一方のスタンダードセル101は、セル内部のメタル配線108、110の配線幅Ws1、Wd1は太く、他方のスタンダードセル151では、セル内部のメタル配線158、160の配線幅Ws2、Wd2は、前記一方のスタンダードセル101の配線幅Ws1、Wd1よりも細く設定される(Ws2<Ws1、Wd2<Wd1)。配線幅の細いセルライブラリ151は、駆動負荷の小さい回路に限定して適用される。

(もっと読む)

半導体装置の配線構造及びそれを備えた半導体装置

【課題】信号配線が電源配線と長距離に亘って並走することを回避して、信号配線の寄生容量を低減してノイズの影響を低減する半導体装置の配線構造及びそれを備えた半導体装置を提供すること。

【解決手段】第1方向X1に延びる複数の第1配線1Vから構成される第1配線層110と、第1配線層110の上に配設され、第1方向X1に交差する第2方向X2に延びる複数の第2配線2Vから構成される第2配線層120とを備え、第1配線層110および第2配線層120は、第1方向X1および第2方向X2により規定される平面内に設定された配線領域R内に配設され、第1配線1Vは、配線領域Rの第1方向X1における一端から他端までの全長よりも短い長さでそれぞれ形成され、第2配線2Vは、配線領域Rの第2方向X2における一端から他端までの全長よりも短い長さでそれぞれ形成されている半導体装置100の配線構造。

(もっと読む)

半導体装置、電源スイッチの制御方法及びその設計方法

【課題】従来の半導体装置では、電源制御領域への突入電流の発生を抑制するためにチップ面積が増大する問題があった。

【解決手段】本発明にかかる半導体装置は、オン抵抗が大きな第1のスイッチトランジスタSWLと、オン抵抗が小さな第2のスイッチトランジスタSWSと、を有し、第1、第2のスイッチトランジスタSWL、SWSは、異なる領域に電流を供給し、第1のスイッチトランジスタSWSは、制御信号CONTを直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLは、前記制御信号を直列的に伝搬するように直列に接続され、第2のスイッチトランジスタSWLのうち初段に配置される第2のスイッチトランジスタSWLは、第1のスイッチトランジスタSWSのうち最も後ろに配置される第1のスイッチトランジスタSWSが出力する制御信号CONTが入力される。

(もっと読む)

61 - 80 / 506

[ Back to top ]