Fターム[5F038CD13]の内容

Fターム[5F038CD13]の下位に属するFターム

容量付加安定化 (354)

Fターム[5F038CD13]に分類される特許

101 - 120 / 506

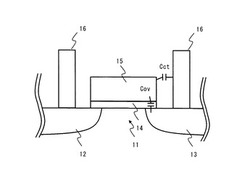

MOSトランジスタのシミュレーションパラメータの抽出方法

【課題】ゲートとドレインとの重なり部分の容量であるゲートオーバーラップ容量を精度よく抽出する。

【解決手段】本発明の一態様に係るシミュレーションパラメータの抽出方法は、コンタクトプラグ数のみが異なる複数のレイアウトパターンのそれぞれについて、所定のバイアス電圧下におけるゲート−ドレイン間の容量を測定して真のゲートオーバーラップ容量を含む測定値を求め、コンタクトプラグとゲートとの間の寄生容量を求めるためのモデルパラメータを変化させてシミュレーションを行って得られるコンタクトプラグとゲートとの間のコンタクト寄生容量を測定値から減算することによりゲートオーバーラップ容量演算値を求め、当該ゲートオーバーラップ容量演算値がコンタクトプラグの数によらず略一定となるモデルパラメータにおける当該ゲートオーバーラップ容量演算値を真のゲートオーバーラップ容量として抽出する。

(もっと読む)

半導体装置

【課題】ラッチアップを利用したESD保護のための半導体装置において、ラッチアップ発生電圧を任意の値に設定すること。

【解決手段】半導体装置300は、P型基板301と、P型基板301の表面に形成されたN型ウェル領域302と、N型ウェル領域302の表面上のP+型拡散領域303及びN+型拡散領域304と、P型基板301とN型ウェル領域302との境界上に配置された酸化膜305と、酸化膜305の一部の上に配置されたポリSi306と、P型基板301の表面上のP+型拡散領域307及びN+型拡散領域308とを備える。フローティング電極309は、ポリSi306及びN型ウェル領域302とそれぞれ容量結合するように配置されている。ポリSi306は接地されている。

(もっと読む)

半導体集積回路、半導体装置及び電子機器

【課題】内部動作に起因する半導体基板の電位的変動を抑制することが容易な半導体集積回路を提供する。

【解決手段】半導体集積回路(1)の内部において、外部電源端子(Pvcc)と半導体基板(Psub)との間および外部グランド端子(Pvss)と半導体基板との間の何れか一方又は双方に可変インピーダンス回路(VZ)を配置し、可変インピーダンス回路に対するインピーダンスの設定に従って、半導体集積回路に形成されたトランジスタの動作に応じて半導体基板に生起される電源電圧側の変動成分とグランド電圧側の変動成分とをバランスさせるようにその変動成分の大きさや波形を決定する。半導体集積回路の電源及びグランド側の変動に起因して半導体基板に与えられる変動成分が抑えられることにより、半導体基板を通して外部でコモンモード電流経路が形成されることを抑制することが可能になる。

(もっと読む)

半導体システム

【課題】複数のエリアを有する半導体システムにおいて不使用エリアにおける消費電力を削減する。

【解決手段】内部電源発生回路70b〜70dを其々有する複数のコアチップCC0〜CC7と、コアチップCC0〜CC7を制御するインターフェースチップIFと、を備えた半導体システムであって、前記インターフェースチップIFはコアチップCC0〜CC7の不使用チップ情報DEFを保持する不使用チップ情報保持回路33を備える。コアチップCC0〜CC7は其々対応する不使用チップ情報DEFを不使用チップ情報保持回路33から受け、該不使用チップ情報DEFが不使用状態を示すときには内部電源発生回路70b〜70dを非活性とし、使用状態を示すときには内部電源発生回路70b〜70dを活性とする。これにより、不使用チップにおける無駄な電力消費が削減される。

(もっと読む)

半導体装置の設計方法

【課題】クロストークノイズによるディレイ変動量を正確に測定する。

【解決手段】複数のインバータを奇数段直列に接続したリングオシレータROと、リングオシレータROの一部の配線(被害側配線)VICに沿って設けられる第1配線(加害側配線)AGGと、前記第1配線AGGに供給する第1パルスを発生するパルス発生回路PGENと、前記第1配線AGGと前記パルス発生回路PGENの間に接続された第1バッファ(加害ゲート)AGと、前記パルス発生回路PGENと前記第1バッファAGとの間に接続される第2配線を具備し、前記第1配線AGGと前記リングオシレータROの一部の配線VICとの間の距離は、前記第2配線と前記リングオシレータROの一部の配線VICとの間の距離より短くする。

(もっと読む)

半導体装置及びその製造方法

【課題】設計基準を遵守しつつ容量値を向上しうる容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】複数の電極パターンをそれぞれ有し、積み重ねるように配置された複数の配線層と、複数の配線層の間にそれぞれ設けられ、隣接する配線層の複数の電極パターンのそれぞれを電気的に接続する複数のビア部と、複数の配線層及び複数のビア部の間隙に形成された絶縁膜とを有する容量素子を有し、ビア部は、電極パターンの中心に対して、電極パターンの延在方向と交差する方向にずらして配置されており、電極パターンは、ビア部が接続された部分において線幅が太くなっており、隣接する電極パターンとの間の間隔が狭まっている。

(もっと読む)

半導体装置及びその信号伝送方法

【課題】隣接信号の間に発生するクロストークノイズ(Crosstalk Noise)による信号の品質低下を防止するための半導体装置及びその信号伝送方法を提供する。

【解決手段】複数の同種信号を伝送するための複数の伝送ラインを具備する半導体装置100において、第1信号IN1を伝送する伝送区間全体の間に第1信号IN1の位相を同一に維持して伝送するための第1伝送ライン150と、第1伝送ライン150に隣接して配置されて第2信号IN2を伝送する伝送区間全体のうちで一部区間の間に第2信号IN2の位相を反転させて伝送するための第2伝送ライン160a、160bが具備される。

(もっと読む)

可変スパイラルインダクタおよび半導体集積回路装置

【課題】インダクタンス値を変えることができ、インダクタ素子が占める基板上でのスペースを小さくしつつ、インダクタ素子を簡便な構成により実現可能とした可変スパイラルインダクタを提供する。

【解決手段】接地導体7を設けた半絶縁性の基板2と、この基板2に形成され、平面スパイラル状のパターンを有し、一端から入力された高周波信号を他端へ通過させるスパイラル導体5と、このスパイラル導体5に対し基板面に直交する方向で間隔を介して設けられたマイクロストリップライン導体6と、このマイクロストリップライン導体6の電位を接地電位又は開放電位にするための駆動バイアスを印加される電極4と、を備え、この電極4へ印加される駆動バイアスのオンオフ駆動により、マイクロストリップライン導体6の状態を高周波信号に対して等価的に接地状態又は短絡状態にし、高周波信号に対して値の異なるインダクタンスを生成する。

(もっと読む)

トランス素子とその製造方法

【課題】マイクロトランス素子を小型化することと、マイクロトランス素子の特性を確保することとを両立する。

【解決手段】 トランス素子は、第1導電型の半導体層を備えた半導体基板と、第1導電型の半導体層の表面側に設けられた第2導電型の半導体層からなる半導体層コイルと、半導体層コイルと並列に接続されており、半導体層コイルのコイル配線間の第1導電型の半導体層に形成されたトレンチと、トレンチ内面に設けられたトレンチ絶縁膜と、そのトレンチ絶縁膜によって被覆されている導電層有するトレンチコイルと、第1導電型の半導体層の表面側に設けられ、半導体層コイルおよびトレンチコイルを被覆するコイル絶縁層と、コイル絶縁層の表面に設けられており、半導体層コイルおよびトレンチコイルと対向している金属層コイルとを備えている。並列接続された半導体層コイルとトレンチコイルによって、第1コイルの抵抗が低減し、トランス素子の小型化と特性確保を両立できる。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

半導体装置

【課題】トランジスタの距離に依存したばらつきに対して、電流源の出力電流誤差を均一にする事ができる、レイアウト構成の半導体装置の提供。

【解決手段】第1の電流源を構成するトランジスタAと、第1の電流源の電流を基準とした第2の電流源を構成する複数のMOSトランジスタBを備えたカレントミラー回路のレイアウトとして、MOSトランジスタAの周囲に、MOSトランジスタBを均等に配置し、入力電流端子及び出力電流端子から、MOSトランジスタA、複数のトランジスタBの同一の端子への配線に関して、それらの特性(寄生抵抗容量)を該配線間で均等化させるレイアウトを有する。

(もっと読む)

集積回路装置及び電子機器

【課題】アナログ処理の特性の向上を図れる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、信号が入力されるパッドPANTと、パッドPANTを介して入力される信号についてのアナログ処理を行うアナログ回路と、アナログ回路の信号入力ノードとパッドPANTとの間に設けられるキャパシターCAを含む。パッドPANTとキャパシターCAの一端とが、最上層金属層ALEで形成されるパッド配線LNPにより接続される。

(もっと読む)

半導体集積回路及び発振回路

【課題】振動子が外付けされて発振回路を実現する半導体集積回路において、振動子が外付けされるパッドと内部回路間の配線による浮遊容量の影響を小さくする。

【解決手段】半導体集積回路は、半導体基板と、第1のパッドP1に第1の抵抗及R1及び第1のコンデンサCACを介して接続の入力端子、及び、第2のパッドP2に第2の抵抗R2及び第3の抵抗RDを介して接続の出力端子を有するインバータ32と、インバータ入力端子と第2の抵抗R2及び第3の抵抗RDの接続点との間に接続され、インバータと共に発振ブロックを構成する帰還素子33と、第1の抵抗R1及び第1のコンデンサの接続点と基板電位との間に接続され、第1のパッドと発振ブロックとの間に配置された第2のコンデンサCGと、第2の抵抗R2及び第3の抵抗RDの接続点と基板電位との間に接続され、第2のパッドP2と発振ブロック間に配置された第3のコンデンサCDとを具備する。

(もっと読む)

半導体装置

【課題】半導体装置の伝送線路の信号伝達効率を高くする

【解決手段】本発明は、多層配線400内に形成され、信号線342下にあり、トランジスタ領域上に形成された第1導体パターン312を有する、半導体装置に関する。第1導体パターン312はグラウンドまたは電源に接続し、トランジスタ領域と重なる。また、信号線342は第1導体パターン312と重なっている。第1導体パターン312は複数のトランジスタ形成領域と重なっていてもよい。第1導体パターン312の下にトランジスタ形成領域を複数有していていもよい。

(もっと読む)

回路のジッタを計算する方法、論理装置及びシステム並びに回路のクロックツリーを合成する方法、論理装置及びシステム

【課題】チップレベルの設計に関する問題に対処し、クロストークカップリングが存在する場合でも正確な経路遅延を計算すること。

【解決手段】一実施例でのクロックツリーにてジッタを計算する方法は、クロックツリーを複数のステージに分割し、クロックツリーに関連する回路の少なくとも一部分のモデルに従って、1以上のステージのジッタを算出する。モデルは回路のジッタのソース各々の表現を含む。本方法は、クロックツリー中の経路又は経路対に関するジッタを計算するため、クロックツリー中の経路又は経路対の各ステージのジッタを互いに統計的に合成するステップを含む。一実施例では、ジッタを効率的に計算し且つクロックスキューゼロを達成するため、モデルは回路の対称的なクロックツリーを合成し、そのツリーでは区六浮くツリーのルートからクロックツリーのシンクに至る全てのパス中の関連するステージは、近似的に電気的に互いに等価な性質を示す。

(もっと読む)

半導体集積回路

【課題】電源オフ時の高圧電源線に対するESD電荷に対して、十分な放電能力を持ちつつ、電源印加時に高圧電源変動・ノイズが発生しても誤動作しない静電保護回路の提供。

【解決手段】シャント素子4のゲートと高圧電源端子との間に接続された調整用容量を持つ。同時に低圧電源電圧とGND間にフィルタ回路と、フィルタ回路によって生成された定電圧を入力とし、シャント回路1のゲート電位を制御するMOSトランジスタM1と電源オフ時にM1の機能を止めるNチャネルMOSトランジスタM2とを有する誤動作防止回路3とを備えた誤動作防止機能付きシャント回路1。このとき誤動作防止回路部をチップの中心部側に、シャント回路部をチップの外縁部側に向けて、チップ上の端部に配置し、シャント回路部の抵抗素子をシャント素子よりも端部に近くに、かつ、誤動作防止回路部とシャント素子との間に配置する。

(もっと読む)

T−コイル回路網設計を生成する方法およびT−コイル回路網

T−コイル回路網を備える回路設計を生成する方法の1つの実施形態は、インダクタのインダクタンスおよびT−コイル回路網の寄生ブリッジ容量を決定するステップ(305−340)を含み得る。寄生ブリッジ容量は、T−コイル回路網の出力に結合された負荷の寄生容量に依存する負荷容量基準と比較され得る(345,355)。T−コイル回路網の出力に結合された回路設計の静電放電(ESD)保護の量、または、T−コイル回路網のインダクタのパラメータが、寄生ブリッジ容量と負荷容量基準との比較に従って、選択的に調整され得る(350,360)。インダクタのインダクタンスと、静電放電保護の量と、インダクタの巻線の幅とを特定可能な回路設計が出力され得る(365)。  (もっと読む)

(もっと読む)

インダクターおよび集積回路装置

【課題】 インダクター配線のインピーダンスの低減と、インダクター配線と基板等との間に形成される寄生容量の低減とを共に実現する。

【解決手段】 多層配線を利用して基板上に構成されるインダクターは、第n層の導体層ME(n)により形成される第1インダクター配線100と、第1インダクター配線100と電気的に接続される、第(n+α)層(αは、1以上の整数)の導体層ME(n+1)により形成される第2インダクター配線200と、を有し、第1インダクター配線100にはスリットが設けられておらず、第2インダクター配線200には、第2インダクター配線の延在方向に沿う少なくとも一つのスリットSL1が設けられている。

(もっと読む)

マイクロトランス素子、信号伝達回路、及び半導体装置

【課題】本発明は、マイクロトランス素子、信号伝達回路、及び半導体装置に係り、微細化を妨げることなくコイル断面積を大きく確保することにある。

【解決手段】半導体基板20上に層間絶縁膜30を挟んで下層コイル32及び上層コイル34が積層されたマイクロトランス素子10において、下層コイル32を、層間絶縁膜30を挟んで積層された第1の金属配線40及び第2の金属配線42と、それら第1の金属配線40及び第2の金属配線42を層間絶縁膜30を貫通して相互に連結したビアコンタクト44と、からなるものとすると共に、上層コイル34を、層間絶縁膜30を挟んで積層された第3の金属配線50及び第4の金属配線52と、それら第3の金属配線50及び第4の金属配線52を層間絶縁膜30を貫通して相互に連結したビアコンタクト44と、からなるものとする。

(もっと読む)

スイッチングシステム及びスイッチング方法

本発明は無線周波数システム及び方法に関する。無線周波数(RF)システムは、バルク基板領域及び埋設酸化物領域を備えるシリコンオンインシュレータ(SOI)上に実装された、少なくとも1つ又は複数のRF信号をスイッチングするための複数のトランジスタスイッチング素子を備えるRFスイッチを具備する。少なくとも1つのフィルタが、基板及び/又はRFシステムに存在する他の高周波信号若しくは制御信号からRF信号を絶縁するように構成される。トランジスタスイッチ素子の線形性を改善するために、フィルタと協働するように構成された結合キャパシタも提供される。 (もっと読む)

101 - 120 / 506

[ Back to top ]