Fターム[5F038DT12]の内容

Fターム[5F038DT12]に分類される特許

121 - 140 / 1,067

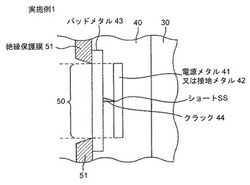

半導体集積回路

【課題】例えばクラック発生などに起因する大量生産段階での低歩留りという問題を防止できる半導体集積回路を提供する。

【解決手段】パッドメタルの下に回路を有する半導体集積回路において、パッド開口部分のパッドメタルの少なくとも下全面に、互いに同一の電位を有する配線メタルを形成し、当該配線メタルの電位を上記パッドメタルと異なる電位に設定した。また、上記配線メタル、及び上記配線メタル以外の電位を有する別の配線メタルは、上記パッドメタルよりも下層に形成される。さらに、上記半導体集積回路の複数のパッドにおいて、バッド開口部分のパッドメタルの少なくとも下全面に形成された複数の配線メタルは互いに同一の電位に設定される。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

信号監視回路及び半導体装置

【課題】半導体装置のサイズを小さくできる信号監視回路を提供する。

【解決手段】半導体装置の電源端子と接地端子との間に直列に設けられた、電流源と、所定信号の状態に応じてオンオフする第一スイッチと、所定信号が監視対象の信号に設定されるとオンする第二スイッチと、を備え、所定信号の状態を前記半導体装置の消費電流によって監視する構成とした信号監視回路。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子単体の駆動力にはバラツキがあっても、搭載回路の駆動力のウェーハ間のバラツキを抑制することのできる半導体装置の製造方法を提供する。

【解決手段】実施形態の製造方法は、複数の半導体素子が並列に配置された回路を有する半導体装置の製造方法であって、上層配線形成工程用に、複数の半導体素子の並列接続数がそれぞれ異なる複数のマスクを製作しておき(工程S01)、半導体基板上に半導体素子を形成し(工程S02)、上層配線を形成する工程の前に、半導体基板上に形成された半導体素子のオン電流の測定を行い(工程S03)、その測定の結果にもとづいて、上層配線形成工程用の複数のマスクから1枚のマスクを選択し(工程S04)、選択したマスクを用いて上層配線を形成する(工程S05)。

(もっと読む)

半導体装置及びその制御方法

【課題】内部電圧生成回路を活性化させる際又は非活性化させる際における内部電圧の急激な変動を防止する。

【解決手段】外部電圧VDDから生成した内部電圧VPPを内部電源配線110aに供給する内部電圧生成回路110と、内部電圧生成回路110の動作を制御する制御回路300と、前記第1の電圧のレベルを検出する電圧検出回路330とを備える。例えば、制御回路300は、内部電圧生成回路110を活性化させる場合、内部電圧VPPの供給能力を第1の速度で段階的に上昇させ、内部電圧生成回路110を非活性化させる場合、内部電圧VPPの供給能力を第1との速度と異なる第2の速度で段階的に下降させる。これにより、内部電圧生成回路110を活性化/非活性化させる際の内部電圧VPPの大幅な変動をそれぞれ最適に防止することが可能となる。

(もっと読む)

絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法

【課題】実際のデバイスの絶縁破壊寿命に適合する精度の良いシミュレーションを行って、正確な絶縁膜の絶縁破壊寿命を求めることで、実測データとの対比で欠陥種、欠陥の大きさ等を正確に解析できる絶縁破壊寿命シミュレーション方法及びシリコンウェーハ表面の品質評価方法を提供することを目的とする。

【解決手段】前記シミュレーションする構造における、前記シリコンウェーハと前記絶縁膜の界面及び前記絶縁膜と前記金属電極の界面に、及び/又は、前記絶縁膜中に予め欠陥を組み込み、該欠陥を組み込んだ構造において、前記絶縁膜中に欠陥を乱数にて発生させて前記絶縁膜の絶縁破壊寿命を求める絶縁破壊寿命シミュレーション方法。

(もっと読む)

半導体装置

【課題】過渡状態における温度検知の遅れ時間を短縮可能な半導体装置を提供すること。

【解決手段】本半導体装置は、半導体基板と、前記半導体基板上に形成された、前記半導体基板の温度を検知する温度検知素子と、前記温度検知素子を被覆する絶縁膜と、前記絶縁膜を介して前記温度検知素子の少なくとも一部を被覆する金属部と、を有する。

(もっと読む)

測定結果管理システム、管理サーバ、及び半導体集積回路装置

【課題】実際に稼動している半導体集積回路装置の実動作に影響を与える要因を解析し、更にその要因を低減することが可能な半導体集積回路装置を提供する。

【解決手段】測定対象である半導体集積回路131と、この半導体集積回路のジッタ又はノイズジッタ、ノイズ等の実動作に影響を与える物理量を測定する測定回路(半導体集積回路装置)130とを同一チップ上に構成する。測定回路の測定結果を解析し、測定対象の半導体集積回路を調整する回路にフィードバックさせる。

(もっと読む)

半導体装置

【課題】電源電圧ドロップを精度よく検出することが可能な半導体装置を提供する。

【解決手段】半導体装置は電源電圧供給部104、105からの電源電圧で動作する動作部と、動作部の動作に伴う電源電圧の変動を検出し、その検出の結果を出力する検出部とを含む。このため、半導体装置の内部で、電源電圧ドロップを検出し、その検出結果を外部に通知することが可能になる。よって、観測ポイントとしてバイパスコンデンサ上のポイントを用いる必要がなくなり、電源電圧ドロップを精度よく検出することが可能となる。

(もっと読む)

半導体装置

【課題】電流検出精度が低下することを抑制することができる半導体装置を提供する。

【解決手段】メインTr2のゲート電極およびセンスTrのゲート電極をゲート電圧を印加する共通のゲート端子と接続する。そして、センスTr3にはゲート端子からそのままゲート電位が印加されると共に、メインTr2にはセンスTr3に印加されるゲート電位が第1、第2抵抗31、32によって抵抗分割された電位が印加され、メインTr2のゲート−ソース間電圧と、センスTr3のゲート−ソース間電圧とが等しくなるようにする。

(もっと読む)

半導体装置

【課題】交流リークが電圧検出回路に流れるのを防ぐことができる半導体装置を提供する。

【解決手段】半導体装置は、アンテナ回路102と、共振周波数調整回路126と、電圧検出回路と、第1の容量素子と、を有する。共振周波数調整回路126は、一方の端子がアンテナ回路102の第1の端子と電気的に接続された第2の容量素子と、第1の端子が第2の容量素子の他方の端子と電気的に接続され、第2の端子がアンテナ回路102の第2の端子と電気的に接続され、ゲートが第1の容量素子及び電圧検出回路と電気的に接続されたトランジスタと、を有する。

(もっと読む)

半導体装置

【課題】主電流Imとこれに対して比例関係にある検知電流Isとの出力用にIGBT素子44,45を備えたIGBTチップ10において、IsからIGBT素子のラッチアップを監視する。製造上のばらつきに対してIs/Imが設計値に調整可能にするとともに、調整抵抗のスペース節約や作業工数低減を図る。

【解決手段】Isを出力する原電極16とセンスパッド17と間の抵抗値を調整する調整抵抗部60は、短絡金属層67と共に作り込まれる。短絡金属層67は、調整抵抗部60の各抵抗64に対する並列接続部分により該各抵抗64の両端子を短絡している。各抵抗64は、レーザのトリミング加工により並列接続部分が切除されると、両端短絡状態を解除されて、調整抵抗部60の抵抗要素として機能する。調整抵抗部60の抵抗値は、抵抗要素となった抵抗64の接続関係及び抵抗値に応じた値になる。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、各前記回路ブロック毎に電源電圧を供給し、前記電源電圧を電圧調整回路により切り替える電圧供給回路を有し、前記電圧調整回路を切り替える電圧制御信号を記憶する電源電圧制御メモリを有する電圧設定回路を有し、前記半導体装置の回路の複数箇所に回路の電圧を検出する電圧検出スイッチを有し、前記電圧検出スイッチを指定することで電圧を検出する回路の位置を切り替え、且つ、前記電源電圧制御メモリにアドレスを指定して値を書き込む制御を行う回路スイッチ制御回路を有する半導体装置を用いる。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

半導体集積回路

【課題】 内部回路の内部ノードが初期状態に設定されたことを精度よく検出し、内部回路が動作を開始するまでの復帰時間を短縮する。

【解決手段】 第1電源スイッチは、内部電源電圧を受けて動作する内部回路の動作を開始させるための第1電源オン信号の活性化中に、外部電源線を内部電源電圧が供給される内部電源線に接続する。第2電源スイッチは、第2電源オン信号の活性化中に、外部電源線を内部電源線に接続する。検知部は、第1電源スイッチのオンにより上昇する内部電源電圧を受けて動作する回路を含む。検知部は、内部電源電圧が第1電圧を超えることにより、内部回路の内部ノードが初期状態に設定されたことを検出したときに第2電源オン信号を活性化する。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出する精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に形成された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンに接続され、導電パターンの回路定数により決定される発振周波数で発振する発振回路と、発振回路の発振周波数が事前に設定された範囲に含まれるか否かを判定し、発振周波数が事前に設定された範囲に含まれない場合に、導電パターンに改変が加えられたことを検出する検出回路とを有することを特徴とする半導体集積回路装置が提供される。

(もっと読む)

テストエレメントグループおよび半導体装置

【課題】保護ダイオードの有無に拘らず、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】テストエレメントグループ10において、電界効果型トランジスタからなるn個の素子DUT1〜DUTnが規則的に配置されている。ドレイン線DLおよびソース線SLがそれぞれ、全ての素子DUT1〜DUTnに対して共通化されており、その一方で、ウェル線WLが素子DUT1〜DUTnごとに1つずつ設けられている。選択対象の素子(選択素子DUTx)の素子特性を測定する際には、基板バイアス効果を利用して、非選択対象の素子(非選択素子DUTy)に流れるオフリーク電流を小さくする。

(もっと読む)

素子評価用半導体集積回路

【課題】 インバータ等の論理ゲートからなる大規模なゲートチェーンを有し、そのゲートチェーンにおいて不良の原因となっている論理ゲートを特定することが容易な素子評価用半導体集積回路を提供する。

【解決手段】 多段接続された複数の論理ゲートからなるゲートチェーンと、モニタ信号線MONと、ゲートチェーンにおける各論理ゲートの出力ノードとモニタ信号線MONとの間に各々介挿され、当該モニタユニットMUaを指示する制御信号が与えられることにより、モニタ信号線MONに当該出力ノードの電圧に依存した信号を発生させる複数のモニタユニットMUaと、ゲートチェーンにおける複数の論理ゲートの出力ノードを順次モニタ対象とし、モニタ対象とする論理ゲートの出力ノードに接続されたモニタユニットを指示する制御信号を発生するモニタユニット選択手段を有する。

(もっと読む)

電源状態判定回路を有する集積回路

【課題】電源オープン検出回路の動作マージンを大きくする。

【解決手段】電源端子とグランド端子と入力端子と内部回路とが形成された集積回路において,入力端子と電源端子との間に設けられ,入力端子から前記電源端子への方向の一方向性回路と,電源端子が外部電源と接続しているか否かを検出して電源オープン検出信号を出力する電源状態判定回路とを有する。一方向性回路は,電源端子の電圧がゲートに印加される第1のトランジスタと,第1のトランジスタに直列に接続された第2のトランジスタとを有し,入力端子には外部電源の電圧が入力される。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン以外の半導体で形成される半導体素子で使用可能なTEGを有する半導体装置およびその製造方法を提供する。

【解決手段】SBD部2aと、SBD部2aの電気特性を測定するためのTEG部3aと、を備えた半導体装置1aであって、SBD部2aは、n型のSiCドリフト層8と、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第1のショットキー電極13と、を有し、TEG部3aは、SiCドリフト層8の表面9を含む箇所に形成されたp型のイオン注入層18aと、SiCドリフト層8上に、SiCドリフト層8の表面9と接触して形成された第2のショットキー電極21aと、第2のショットキー電極21aと電気的に接続され、SiCドリフト層8とは接触しないようにイオン注入層18a上に形成された電極パッド22と、を有する

(もっと読む)

121 - 140 / 1,067

[ Back to top ]