Fターム[5F038DT12]の内容

Fターム[5F038DT12]に分類される特許

61 - 80 / 1,067

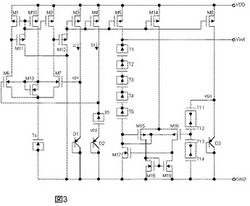

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

半導体装置

【課題】ラッチ型メモリが搭載されたCPUを動作させるに際して、処理内容に応じて常時記憶方式と終了時記憶方式のいずれかを選択し、ラッチ型メモリが搭載されたCPUの消費電力を低減する。

【解決手段】ラッチ型メモリが搭載されたCPUを動作させるに際して、電源のオンオフの繰り返し動作が多い場合には常時記憶方式とし、電源のオンオフの繰り返し動作が少ない場合には終了時記憶方式とする。常時記憶方式と終了時記憶方式のどちらを選択するかは、消費電力に応じて決定したしきい値をもとにして決定する。

(もっと読む)

TEG構造、及び層間剥離箇所探索方法

【課題】配線層とビア層との剥離箇所を簡単に特定できる技術を提供する。

【解決手段】第1層配線層のパターンの導体部は、所定の方向Xに沿って、複数本、点線状に設けられた導体部と、前記方向Xに交差する所定の方向Yに沿って、複数本、点線状に設けられた導体部とを具備し、第2層配線層のパターンの導体部は、所定の方向Xに沿って、複数本、点線状に設けられた導体部と、前記方向Xに交差する所定の方向Yに沿って、複数本、点線状に設けられた導体部とを具備し、前記方向X(方向Y)に沿って設けられた第1層配線層と第2層配線層とは、平面視において、互いに、食い違うように、かつ、全体で、一つの連続した線が描かれるように設けられてなり、第1層配線層と第2層配線層とは、両方向ともに平面視において共通する或る位置において、電気的に接続し一つのラインに沿った一つの導通ラインが構成されている。

(もっと読む)

半導体集積回路装置のテスト方法およびテストボード

【課題】半導体集積回路装置の入力端子数よりも少ない端子数のテスタを用いて半導体集積回路装置のテストを行うテスト方法を提供すること。

【解決手段】半導体集積回路装置のテスト方法は、半導体集積回路装置の複数の入力端子とテスタからのテスト信号を受信するテスタ端子とを、多対1に電気的に接続するテストボードを介して、該テスタから該半導体集積回路装置に所定のテストパタン信号を送信する工程と、前記半導体集積回路装置の出力端子から出力された出力信号と、前記所定のテストパタン信号に対応する期待値とを比較して、前記半導体集積回路装置の良否を判定する工程と、を含む。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

半導体集積回路

【課題】不良回路ブロックを特定する時間を短くでき、また、各回路ブロックの信頼性加速試験での特性劣化を精度良く測定できる半導体集積回路を提供することを目的とする。

【解決手段】複数の回路ブロックB1、B2、・・・Bnと、複数の回路ブロックに対応し、回路ブロックと電源端子2との接続を制御する複数のスイッチ回路Sa1、Sa2、・・・Sanと、複数のスイッチ回路に対応し、スイッチ回路へ回路ブロック選択信号を出力する複数のフリップフロップ回路DFF1、DFF2、・・・DFFnとを備え、複数のフリップフロップ回路は、シフトレジスタ回路を構成し、外部信号の入力に基づいて、2以上のスイッチ回路を選択して回路ブロック選択信号を出力し、当該回路ブロック選択信号を入力された2以上のスイッチ回路は、当該2以上のスイッチ回路それぞれに対応する回路ブロックと電源端子とを接続する半導体集積回路100。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置

【課題】半導体基板に半導体素子と内部回路とが設けられた半導体装置において、半導体素子及び内部回路の各温度を検出するセンサを効率的に配置してレイアウトの自由度を高めることができ、且つ半導体素子及び内部回路の各温度をより正確に検出し得る構成を提供することを目的とする。

【解決手段】半導体基板5の一方面側に、スイッチング素子20と、このスイッチング素子20の配置領域から距離を隔てて内部回路30が配置されている。また、スイッチング素子20に隣接して、周囲に第1絶縁膜27が形成された第1温度検出素子24が設けられている。さらに、内部回路30よりもスイッチング素子20に近い側に、周囲に第2絶縁膜28が形成された第2温度検出素子25が設けられている。そして、第2絶縁膜28の厚さが第1絶縁膜27の厚さよりも大きくなるように構成されている。

(もっと読む)

半導体チップのクラックのチェックテスト構造を有する半導体装置

【課題】半導体チップ積層後に、チップごとにクラックの有無検出可能な半導体装置の提供。

【解決手段】積層半導体装置において、半導体チップ21〜24は、基板10とこの表裏面の対向する位置に形成した対のテスト端子と配線61を備える。これらは、一対の(表側)第1のテスト端子621h、(裏側)第1のテスト端子621t及び複数対の(表側)第2のテスト端子622〜625h、(裏側)第2のテスト端子622〜625tで、貫通電極TSVT1が(表側)第1のテスト端子と(裏側)第1のテスト端子を接続し、貫通電極TSVT2〜5が対の(表側)第2のテスト端子と(裏側)第2のテスト端子同士を接続し、配線は、一端が第1のテスト端子と、他端が第2のテスト端子の一つに接続され、基板の外周に沿って延びる。また異なる半導体チップの上下に隣接する第2のテスト端子同士も接続する。

(もっと読む)

バンドギャップリファレンス回路

【課題】温度に対し高精度なリファレンス電圧の発生を実現する。

【解決手段】ダイオード接続されたトランジスタのベース−エミッタ間電圧を用いた、温度に対して負の特性を持つ電圧に、絶対温度に比例する正の特性を持つ電圧を加えて1次の温度補償を行うとともに、さらに前記トランジスタのベース−エミッタ間電圧に含まれる例えば2次の温度特性成分を打ち消す温度補償信号を発生するN次温度補償信号発生回路105を設け、ベース−エミッタ間電圧に、N次温度補償信号発生回路105からの温度補償信号Vcompを加えることにより、ベース−エミッタ間電圧に含まれる2次の温度特性成分による変動を抑制する。

(もっと読む)

温度測定装置、温度校正装置及び温度校正方法

【課題】熱処理機構を用いて基板を所定の温度に熱処理する熱処理装置において、前記熱処理機構の温度を簡易な方法で適切に校正する。

【解決手段】温度校正装置の温度検査治具10は、熱処理板上に載置される被処理ウェハ70と、被処理ウェハ70上に設けられた複数のホイートストンブリッジ回路71とを有している。ホイートストンブリッジ回路71は、温度変化に応じて抵抗値が変化する4つの測温抵抗体72と、接触子41が接触する4つのコンタクトパッド73と有している。温度校正装置の制御部では、ホイートストンブリッジ回路71が平衡状態となるように、すなわちホイートストンブリッジ回路71のオフセット電圧がゼロになるように、熱処理板の温度を調節する。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】電源線との接続/遮断が切替制御される接続/遮断領域回路を有する半導体装置において、電源線との接続を行う際、突入電流により電源線に急激な電圧降下が生じ、動作中の他の回路が誤動作を起こす問題を解決する。

【解決手段】第1の内部配線と、電源線と第1の内部配線の接続/遮断を切り替える第1のスイッチと、第1の内部配線と接続/遮断領域回路の接続/遮断を切り替える第2のスイッチと、容量素子と、第1の内部配線と容量素子の接続/遮断を切り替える第3のスイッチを備え、接続/遮断領域回路への電源供給を立ち上げる場合、第1のスイッチを遮断し、容量素子の電荷を接続/遮断領域回路に接続された第2の内部配線に供給して閾値電位まで充電した後に、第1のスイッチを接続して、電源線により第2の内部配線を電源線の電位まで充電させる。

(もっと読む)

温度検出装置、温度検出回路およびパワー半導体モジュール

【課題】温度検出回路と絶縁素子とを同一の基板上に形成できるようにし、装置全体の小型化を容易にする温度検出装置を提供する。

【解決手段】温度検出回路200は、温度センサ35で検出された温度をデジタル値に変換するAD変換回路44とデジタル比較回路45を備えている。デジタル比較回路45の出力は、第1パルス発生器52、第2パルス発生器53を経由して絶縁トランス回路101に入力される。絶縁トランス回路101で発生する誘導電流によりパルス信号が信号復調回路102に伝達される。また、温度センサ35で検出された温度が限界温度を越えたときにコンパレータ49からパルス信号が生成され、同様に、信号復調回路102に伝達される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】TEGによる検査結果を容易に確認できるようにしつつ、TEGの占有面積を小さくする。

【解決手段】TEG群300は、第1テスト用パッド310、第2テスト用パッド312、及び複数のTEG(例えば第1TEG320、第2TEG340、及び第3TEG360)を有している。複数のTEGは、電気回路上、第1テスト用パッド310と第2テスト用パッド312の間に位置し、互いに直列又は並列に配置されており、かつ平面視で互いに重なっていない。本実施形態において、TEG群300を構成するTEGは、OBRICH(Optical Beam Induced Resistance Change)用のTEGである。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

半導体装置

【課題】ドライバの故障による出力異常を救済することが可能な故障検出救済回路を含んだ半導体装置を提供すること。

【解決手段】故障検知部1は、ドライバ10の出力の期待電位の逆電位となるようにドライバ10の出力にプルアップ抵抗15またはプルダウン抵抗18を接続し、ドライバ10の入力電位と出力電位とを比較することによりドライバ10の故障を検出する。故障救済部2は、故障検知部1によってドライバ10の故障が検出された場合に、期待電位と同電位となるようにドライバ10の出力にプルアップ抵抗26またはプルダウン抵抗29を接続してドライバ10の故障を救済する。したがって、ドライバ10の故障による出力異常を救済することが可能となる。

(もっと読む)

半導体集積回路

【課題】内蔵された回路の状態を確認する機能を備えた半導体集積回路を更に小型化することができる技術を提供

【解決手段】半導体集積回路1では、コアLSI11と周辺LSI12との間の内部配線WIが異常であると判定回路15が判定すると、判定回路15は、リングオシレータ16Aを発振させることを指示する情報(第1発振指示情報)をリングオシレータ制御部17へ出力する。そしてリングオシレータ制御部17が第1発振指示情報を取得すると、リングオシレータ制御部17が、発振周波数f1で発振するように構成されたリングオシレータ16Aを発振させる。そして、半導体集積回路1内で発生している磁界を近磁界プローブで測定し、発振周波数f1で大きさが変動する磁界を検出した場合に、リングオシレータ16Aが動作していると判断することができる。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

半導体集積回路装置

【課題】 集積回路における時間的に変動するばらつきを検出する回路を提供する。

【解決手段】 集積回路内に検出回路100、演算回路101、ばらつき/電圧変換回路113とを設ける。検出回路100において集積回路の特性ばらつきを検出回路100の出力信号の発振周波数として検出する。演算回路101では、タイマ106にて規定した時間間隔毎に検出したばらつき情報をレジスタ111に格納し、統計演算回路112にて統計処理を施し、集積回路の時間的に変動する特性ばらつきを検出する。更に、ばらつき/電圧変換回路113は、検出された特性ばらつきに対応した電圧情報に変換する。

(もっと読む)

61 - 80 / 1,067

[ Back to top ]