Fターム[5F038DT12]の内容

Fターム[5F038DT12]に分類される特許

141 - 160 / 1,067

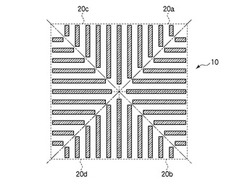

異物検出用パターン及び半導体装置

【課題】異物の種類によらずに高効率で異物の存在を検査しうる異物検出用パターン、並びにこのような異物検出用パターンを有する半導体装置を提供する。

【解決手段】基板上に形成された複数の角部を除いたL字型パターンを有し、複数の角部を除いたL字型パターンは、除いた前記角部の位置が直線上に並ぶように離間して配置されている。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

半導体集積回路装置

【課題】半導体基板の表側に配置された回路が半導体基板の裏側から解析されることを検出する技術を提供することを目的とする。

【解決手段】回路ブロックが配置された第1面と、第1面の反対側の第2面とを有する半導体基板と、半導体基板を搭載する実装基板と、実装基板のうち、回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。半導体基板の第2面と実装基板とが対向するように、半導体基板が実装基板に搭載されている。

(もっと読む)

半導体装置及びこれを用いた電気回路、電気回路の制御方法

【課題】消費電力を増大させずにオンチップでHEMTの動作状況をモニターする。

【解決手段】

この半導体装置10においては、第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層側に、2次元電子ガス(2DEG)層13が形成される。この半導体装置10において、電子は、電子供給層12の表面に形成された第1の主電極であるソース電極14と、同様にこの表面に形成された第2の主電極であるドレイン電極15との間を、この2DEG層13を通って流れる。ゲート電極16とソース電極14との間の電子供給層12上に電位検出電極17が設置される。この電位検出電極17には、動作時にこの電位検出電極17に流れる電流がドレイン電流と比べて無視できる程度となるような、充分に高い抵抗値をもつ抵抗18が接続される。

(もっと読む)

電流制御用半導体素子、およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa及びオフセットbを動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

半導体装置及びその制御方法

【課題】半導体装置に電源遮断(パワーゲーティング)を適用する際に、待機モード時の出力が一意に定まらない場合がある。そのような場合には、複数のバッファ電源線と複数の電源セレクタを用意することでパワーゲーティングを適用する。しかし、このような方法では回路面積が増加してしまうという問題がある。

【解決手段】そこで、パワーゲーティングを適用した回路が非活性状態から活性状態に復帰する際のタイミングを半導体装置に発行されたコマンド、又はサブ電源線が復帰電圧の監視、に基づいて定めることとする。

(もっと読む)

半導体装置及びその検査方法並びにその設計方法

【課題】不良箇所を容易に特定し得る半導体装置及びその形成方法並びにその設計方法を提供する。

【解決手段】配線パターン32aと、ダミーパターン32bと、一方の端部が配線パターンに電気的に接続され、他方の端部がダミーパターンに電気的に接続されたヒューズ32cとを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の設計方法

【課題】TEGパターンより上の層を除去しなくてもTEGパターンを用いた検査を行うことができるようにする。

【解決手段】複数の配線層200,300,400は第1TEGパターン30の上に形成されている。複数の配線層200,300,400には、それぞれ配線242,342,442及び複数のダミーパターン224,324,424が形成されている。電極パッド444は、最上層の配線層400に形成されている。そして平面視において、第1TEGパターン30は、いずれの配線242,342,442及びダミーパターン224,324,424にも重なっていない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 半導体基板上に形成された半導体集積回路の、特にプローブ検査時間を短縮することができる検査工程を提供する。

【解決手段】 検査対象となる半導体基板には、半導体集積回路本体を含む回路領域2aと、それに隣接するスクライブエリアにTEG3aが形成され、回路領域2aには第1パッド電極5a、5bの列が、またTEG3aには第2パッド電極6の列が設けられる。ここでTEG3aに隣接している方の第1パッド電極5aが第2のパッド電極6に対向しないように配置される。このような状態の第1パッド電極5a、5bおよび第2パッド電極6にプローブ針8a、8b、9を接触させて半導体集積回路の検査とTEGの測定とを同時に行う。

(もっと読む)

半導体装置及び半導体テスト方法

【課題】LSIの全体動作のパフォーマンス低下を抑えながら各ブロックに対する電源供給の制御を行うことができ、且つLSI内部のパワースイッチの故障を検出することが可能な半導体装置及び半導体テスト方法を提供することを目的としている。

【解決手段】機能毎に分割されたブロックに対する電源の供給と遮断を制御する半導体装置であって、前記ブロックに供給される電源電圧と当該半導体装置全体に供給される電源電圧とを比較する電圧比較手段と、前記電圧比較手段の出力の変化により、前記ブロックに供給される電源電圧の変化時間を計測する計測手段と、を有する。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

半導体装置及び半導体装置の制御方法

【課題】半導体装置の消費電力を削減する。

【解決手段】回路動作スケジュール補正部14が、回路動作スケジュールを入力し、複数の回路動作期間を連続するように、回路動作期間の開始時刻または終了時刻を補正し、電源スイッチ制御部15が、補正された回路動作スケジュールにしたがって、回路11へ電源を供給するか否かを切り替える電源スイッチ12をオンまたはオフすることで、電源スイッチ12の動作回数が減少し、電源スイッチ12をオフからオンする際の、電源復帰時のエネルギー損失が減少し、消費電力が低減される。

(もっと読む)

半導体集積回路装置の検査方法及び半導体集積回路装置

【課題】複数の集積回路層が厚さ方向に積層されて成る半導体集積回路装置の層間接続不良の有無を、一層積層する毎に短時間で検査することが可能な検査方法及び半導体集積回路装置を提供する。

【解決手段】互いに積層される集積回路層10及び20に、複数の検査用整流素子部15及び25をそれぞれ形成する。複数の検査用整流素子部15(25)は、複数の接続用端子14(24)のそれぞれと正電源配線13a(23a)及び接地配線13b(23b)との間に接続され、整流素子15a,15b(25a,25b)を含み電流により発光する。複数の接続用端子14及び24を互いに電気的に接続したのち、正電源配線13a(又は接地配線13b)と接地配線23b(又は正電源配線23a)との間にバイアス電圧を印加し、検査用整流素子部15又は25の発光に基づいて、接続用端子14及び24の接続状態を検査する。

(もっと読む)

半導体集積回路装置の検査方法及び半導体集積回路装置

【課題】複数の集積回路層が厚さ方向に積層されて成る半導体集積回路装置の層間接続不良の有無を、一層積層する毎に短時間で検査することが可能な検査方法及び半導体集積回路装置を提供する。

【解決手段】互いに積層される集積回路層10及び20に、複数の検査用整流素子部15及び25をそれぞれ形成する。複数の検査用整流素子部15(25)は、複数の接続用端子14(24)のそれぞれと正電源配線13a(23a)及び接地配線13b(23b)との間に接続され、整流素子15a,15b(25a,25b)を含み電流により発光する。複数の接続用端子14及び24を互いに電気的に接続したのち、正電源配線13a(又は接地配線13b)と接地配線23b(又は正電源配線23a)との間にバイアス電圧を印加し、検査用整流素子部25の発光に基づいて、接続用端子14及び24の接続状態を検査する。

(もっと読む)

半導体装置

【課題】ダイシング処理に起因する、チップ用パッド同士のショートを抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板と複数の第1のパッドと、複数の第2のパッドとを備える半導体装置であり、第1のパッドは素子形成領域IMC内に、第2のパッドは素子形成領域IMCを取り囲むダイシングライン領域DLR内に形成される。ダイシングライン領域DLRには、第2のパッド同士が電気的短絡を生じさせやすい第1の領域SLRと、第2のパッド同士が電気的短絡を生じさせにくい第2の領域SURとを有している。第1の領域SLRに対向する位置に配置された一部の第1のパッドは、第2の領域SURに対向する位置に配置された残りの第1のパッドよりも、素子形成領域IMCの外縁の1辺BDLから離れて配置されている。

(もっと読む)

半導体集積回路装置

【課題】制御信号の系統を整理して、不定信号伝播防止回路等の検討漏れの危険性を回避し、さらに、自動化ツールへの搭載へ向けた検討を容易にし、また、チップ内部での電源遮断制御を容易化することができる半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置において、各独立した電源領域AreaA〜AreaIごとに電源遮断の優先順を設け、優先順の高い回路がONしている場合にはそれより優先順の低い電源領域はOFFにできないという規則を設けて、設計方法の容易化を図る。また、各独立した電源領域AreaA〜AreaI内において、さらに別の電源を印加できる領域を設け、その領域に中継バッファ(リピータ)やクロックバッファ、情報退避用の情報保持ラッチを集積する。レイアウト上は、電源線の電流を分散させる目的でセルがロウ方向に並ぶ方向と垂直な方向にまとめてレイアウトすればよい。

(もっと読む)

電流検出回路およびそれを有するインバータ回路が備えられる半導体装置

【課題】電流値だけでなく電流の流れる向きまで検出できる電流検出回路およびそれを有するインバータ回路が備えられる半導体装置を提供する。

【解決手段】下アーム10b、10d、10fのIGBT11b、11d、11fおよびFWD12b、12d、12fに対してセンス素子を備えると共に、各センス素子に対して電流検出抵抗18a〜18fが直列接続させる。これにより、各センス素子および電流検出抵抗18a〜18fに基づいて、具体的には第1電位および第2電位を検出することにより、各相の電流経路に流れる電流の電流値の絶対値および向きを検出することが可能となる。

(もっと読む)

半導体装置

【課題】演算処理や電力消費を増大させることなく、温度特性が安定する半導体装置を提供することを課題とする。

【解決手段】高周波信号を処理する半導体装置1であって、高周波信号を処理する複数の素子2〜8が形成された半導体基板を備え、半導体基板には、複数の素子2〜8のうち温度に応じて特性が変化する特定の素子2,3,5〜8に隣接して該特定の素子2,3,5〜8を加熱する発熱素子9A〜Fが形成されている。

(もっと読む)

141 - 160 / 1,067

[ Back to top ]