Fターム[5F038DT12]の内容

Fターム[5F038DT12]に分類される特許

201 - 220 / 1,067

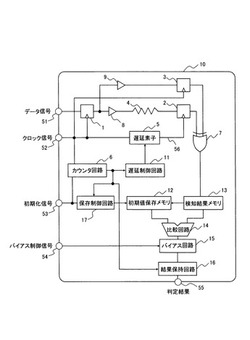

半導体集積回路及び半導体集積回路の試験方法

【課題】実際の動作条件下においてエレクトロマイグレーションの劣化現象を検知すると共に、故障の兆候を検知することが可能な半導体集積回路を提供することである。

【解決手段】本発明にかかる半導体集積回路10は、カウンタ回路6と、遅延クロック信号56を生成する遅延素子5と、クロック信号52のクロックサイクル毎にトグルするデータを入力する第1のフリップフロップ1と、第1のフリップフロップ1からの出力信号を入力する配線4と、遅延クロック信号56に基づき駆動し、配線4からの出力信号を入力する第2のフリップフロップ2と、クロック信号52に基づき駆動し、第1のフリップフロップ1からの出力信号を入力する第3のフリップフロップ3と、第2及び第3のフリップフロップ2、3からの出力信号の排他的論理和を出力する排他的論理和回路7と、を有する。

(もっと読む)

半導体集積回路及びそれを備えた電圧制御装置

【課題】従来技術の半導体集積回路では、チップの特性を精度良く検出できないという問題があった。

【解決手段】本発明にかかる半導体集積回路は、モニタ回路12_1と、連続するM(Mは2以上の整数)個のパルスからなるクロックパルス信号EN_PULSEを生成し、モニタ回路12_1に対して出力する制御回路13と、を備える。また、モニタ回路12は、クロックパルス信号EN_PULSEをM分周し、イネーブル信号ENとして生成する分周器121と、イネーブル信号ENに基づいて設定された期間に発振信号をモニタ出力値として生成するリングオシレータ122と、を備える。

(もっと読む)

半導体ウェーハ、及びその製造方法

【課題】シリコン基板にダメージを与えずに、ゲート下の不純物分布の正確な評価を安定して行うことのできる半導体ウェーハとその製造方法を提供する。

【解決手段】 半導体ウェーハは、半導体基板上の所定の箇所に設定されたモニター領域に、他と電気的接続を有しない断面形状がW字型のダミー充填部を有する。

(もっと読む)

試験装置、測定装置および電子デバイス

【課題】被測定信号のジッタを容易に測定する。

【解決手段】被測定信号の良否を判定する試験装置であって、周期が既知の基準信号のパルス数と、被測定信号のパルス数とを、同一の測定期間内で並行して計数する計数ステップを複数回繰り返す周波数カウンタと、同一の測定期間内で計数した基準信号および被測定信号のパルス数の比、および、基準信号の周期に基づいて、測定期間における被測定信号の平均周期を、それぞれの計数ステップについて算出する平均周期算出部と、平均周期算出部が算出した平均周期のばらつきを算出するノイズ算出部と、平均周期のばらつきに基づいて、被測定信号の良否を判定する判定部とを備える試験装置を提供する。

(もっと読む)

ブリッジ回路のオフセット電圧調整構造およびそれを備えた電子部品

【課題】調整に時間を要することがなく、低コストなブリッジ回路のオフセット電圧調整構造およびそれを備えた電子部品を提供する。

【解決手段】基板100上に形成されたブリッジ抵抗R1、R2、R3、R4と、基板100上に形成された抵抗領域200と、抵抗領域200に形成された3以上の複数のコンタクト300と、コンタクト300とブリッジ抵抗R1、R2、R3、R4を電気的に接続する配線部400と、を有し、ブリッジ抵抗R1、R2、R3、R4と、配線部400により複数のコンタクト300から選択されてブリッジ抵抗R1、R2、R3、R4に接続された調整抵抗Ra、Rbとからブリッジ回路10を構成し、この選択を配線部400の製造工程において行なう構成とする。

(もっと読む)

半導体装置及びパルス幅検出方法

【課題】半導体装置内部で発生するパルス信号のパルス幅を精度高く簡単に検出する。

【解決手段】ICチップ20に設けられた内部パルス波形変換回路11は、第1のイネーブル信号PLS_RISE_ENが有効で第2のイネーブル信号PLS_FALL_ENBが無効な期間において内部パルス信号PLSが立ち上がるタイミングで予め定められた方向に変化し且つ該変化した後はその状態が予め定められた時間以上継続する内部パルスモニター信号PLSMONを生成すると共に、第1イネーブル信号PLS_RISE_ENが無効で第2イネーブル信号PLS_FALL_ENBが有効な期間において内部パルス信号PLSが立ち下がるタイミングで上記予め定められた方向に変化し且つ該変化した後はその状態が前記予め定められた時間以上継続する内部パルスモニター信号PLSMONを生成する。生成された内部パルスモニター信号PLSMONは、内部パルス信号PLSのパルス幅を検出するテスタ22に対して出力される。

(もっと読む)

半導体集積回路装置

【課題】デバイスばらつきなどを評価するプログラムや装置などを不要としながら、短時間で高精度なデバイスばらつきを評価する。

【解決手段】ペアとなるリングオシレータ91,101から出力される信号A,Bをカウンタ12,13によってカウントし、いずれかのカウンタがカウントフルとなると、差分演算部14は、信号Aが信号Bよりも大きいと信号Bの反転信号を乗算器16に出力し、信号Aが信号Bよりも小さいと、信号Aの反転信号を出力する。乗算器16は、入力された演算結果を二乗して、加算器17に出力する。加算器17は、フリップフロップ19に格納された値と乗算器16の演算結果とを加算する。その加算結果は、フリップフロップ19に格納される。以下、同様の処理を各ペアとなるリングオシレータすべてについて行い、ばらつきデータとして出力する。

(もっと読む)

クロックジッタ抑制方法及びプログラム

【課題】クロックジッタ抑制方法及びプログラムにおいて、比較的短時間、且つ、比較的低コストでプログラマブルデバイス等の半導体集積回路のクロックジッタを確実に抑制することを目的とする。

【解決手段】クロックバッファに接続された記憶素子に論理値を設定し、記憶素子の閾値電圧を可変設定し、半導体集積回路内の解析対象となる対象回路を動作させた状態で記憶素子に保持されている値を読み出し、閾値電圧と、読み出された値が前記論理値と反転関係にある記憶素子と、読み出しの対象となった各記憶素子の位置情報に基づいて、クロックバッファの電源電圧のノイズの影響度と一定以上のノイズの影響を受ける箇所を特定し、する解析処理を行い、解析処理の結果に基づいて半導体集積回路の構成要素の配置と配線の制約条件を作成し、ノイズが低減するように制約条件の配置を変更して再配置する再配置処理、又は、制約条件の配線を変更して再配線する再配線処理を行うように構成する。

(もっと読む)

半導体装置

【課題】省電力化および信頼性の向上、または小面積化を実現可能な半導体装置を提供する。

【解決手段】電源遮断が行われない内部電源Vint0と電源遮断が行われる内部電源Vint1との間を接続する電源スイッチSWと、電源遮断が行われる内部電源Vint1の電圧を判定する内部電圧判定回路VINTDETを設ける。電源遮断が行われる内部電源Vint1は、外部電源Vextからレギュレータ回路VREGを用いて生成する。Vint1の電源遮断時は、SWをオフにし、VREGのオフおよびVREG出力の接地電位GNDへのショートを行い、Vint1の電源復帰時は、VREGのオンおよびショートの解除を行い、上昇したVint1の電圧をVINTDETで判定した上で回路ブロックBLK1の動作開始およびSWのオンを行う。

(もっと読む)

高電圧集積回路用のモード選択のための方法と装置

【課題】追加の高電圧回路の不便なしに高電圧集積回路の端子に機能性を追加する方法を開示する。

【解決手段】特典は追加の端子の犠牲なしに集積回路の試験、トリミング・パラメータ、または他の目的で代替動作モードを選択することができることである。一実施形態において、普通の低電圧回路が、通常高電圧に曝される端子の電圧をモニタリングする。簡単な電圧検出器と通常のラッチの構成により、集積回路が意図された用途にないときには試験とトリミング・モードに容易に入ることができるが、集積回路が意図された用途で動作しているときには試験とトリミング・モードに入ることが禁止される。

(もっと読む)

半導体集積回路及び電子機器

【課題】システマテックばらつきとランダムばらつきの両方を考慮した適応型電圧スケーリング技術を実現することにある。

【解決手段】適応型電圧スケーリングを実施するシステム構成において、プロセスばらつきの種類毎に最適な検出回路を設置する。すなわち、システマテックばらつき検出用にゲートディレイの平均値に対する相対値を生成する第1測定回路(100)、及び、ランダムばらつき検出用にゲートディレイの標準偏差に対する相対値を生成する第2測定回路(200)を別々に設置する。夫々の測定回路で生成された相対値に基づいて電源電圧を決定するための制御情報(VCNT)を生成する。これを生成するときは例えばテーブルデータを参照する。

(もっと読む)

半導体装置

【課題】パワー素子の駆動が不当に低下することが抑制された半導体装置。

【解決手段】複数のパワー素子が同一の半導体基板に形成された半導体装置であって、半導体基板における複数のパワー素子それぞれと隣接する位置に形成された複数の検温素子と、該検温素子の出力信号に基づいて、パワー素子の駆動信号を制御する制御部と、を有し、制御部は、複数の検温素子の出力信号に基づいて、複数のパワー素子の内、他のパワー素子と比べて発熱状態が異なるパワー素子を算定し、算定したパワー素子の温度が、他のパワー素子の温度と同じになるように、駆動信号を制御する。

(もっと読む)

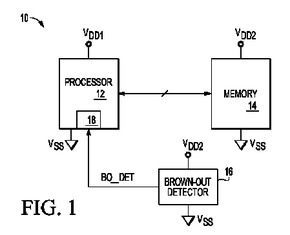

ブラウンアウト検出回路を有するデータ処理システム

ブラウンアウト検出回路(16)は、第1抵抗素子(38)と、第1トランジスタ(46)と、第2トランジスタ(50)と、比較器(40)とを備える。第1抵抗素子(38)が、第1電源電圧端子および第2端子に接続される第1端子を有する。第1トランジスタ(46)は、第1導電性タイプであり、第1抵抗素子(38)の第2端子に接続される第1電流電極と、制御電極と、第2電流電極とを有する。第2トランジスタ(50)は、第2導電性タイプであり、第1トランジスタ(46)の第2電流電極に接続される第1電流電極と、制御電極と、第2電源電圧端子に接続される第2電流電極とを有する。比較器(40)は、第1抵抗素子(38)の第1端子に接続される第1入力端子と、第1抵抗素子(38)の第2端子に接続される第2入力端子と、ブラウンアウト検出信号を供給するための出力端子とを有する。  (もっと読む)

(もっと読む)

半導体集積回路、動作電圧制御方法

【課題】動作電圧を制御してプロセスばらつきを補償する条件で設計した半導体集積回路の起動問題を解消する。

【解決手段】本発明による半導体集積回路は、プロセスばらつきに対して第1のコーナー条件で設計された第1回路部1と、第1の条件より狭い第2のコーナー条件で設計された第2回路部2と、第1回路部1における遅延量に応じて、第1回路部1及び第2回路部2に供給する動作電圧を変更し、動作電圧の変化による遅延特性が第2コーナー条件における遅延特性に適合した場合、第2回路2を起動する制御部12とを具備する。

(もっと読む)

剥離テスト装置及び剥離テスト方法

【課題】剥離が発生した段階を知ることのできるテスト方法の提供。

【解決手段】前記複数の剥離補強ブロック2−1,2,3,4の各々は、複数の配線層に形成された配線群と、前記複数の配線層間で前記配線群を電気的に接続する、導体ホールとを備える。前記テスト回路1は、前記複数の剥離補強ブロックに対応して設けられた、複数のデータ保持回路と、前記複数の剥離補強ブロックの各々の一端に、テスト信号を供給する、テスト信号供給端と、前記複数のデータ保持回路に接続された、不揮発性の記憶回路とを備える。前記複数のデータ保持回路の各々は、対応する前記各剥離補強ブロックの他端から前記テスト信号に応じて出力される信号をテスト結果データとして保持する。前記不揮発性の記憶回路は、前記各データ保持回路に保持された前記テスト結果データを、前記各データ保持回路と対応付けて記憶するように、前記各データ保持回路と接続されている。

(もっと読む)

遅延時間差測定回路

【課題】本発明の一実施例では、2つの信号間の遅延時間差を信号のエッジに応じて正確に測定する遅延時間差測定回路を提供することを目的とする。

【解決手段】上記課題を解決するため、2本の信号線の伝播遅延時間差を測定する遅延時間差測定回路は、該2本の信号線に接続され、選択信号に応じて一方の信号線を伝播する信号を出力する選択回路と、該選択回路に接続され、該選択回路の出力信号を一定時間遅延させて該選択信号として出力する切替回路と、該選択回路の出力側と該2本の信号線の入力側を接続する帰還経路と、該帰還経路に接続され、該帰還経路を伝播する信号の自己発振周期に基づいて該2本の信号線を伝播する信号の遅延時間の差を算出する制御回路とを有する。

(もっと読む)

半導体装置及び半導体チップ

【課題】半導体チップを製造する際のダイシング精度の悪化を防止するとともに、流通後のTEGを用いた測定の実行を完全に防止する。

【解決方法】半導体装置は、複数の製品領域と、それら製品領域間に設けられたスクライブ領域とを備える。複数の製品領域のそれぞれは、プロービング用電極34、40とセンス電極36、38を少なくとも有するTEG30を有している。TEG30には、TEG内の他の部分と比較して電流許容量が低く設定されているセンス配線36a、38aが設けられている。半導体装置では、センス配線36a、38aに所定電流以下の電流が印加された状態でTEG30の特性を測定することができる。その一方、センス配線36a、38aに所定電流を越える電流を印加するとセンス配線36a、38aが破壊される。

(もっと読む)

半導体装置、半導体装置の試験方法、及びデータ処理システム

【課題】インターフェースチップを用いるタイプの半導体装置において、インターフェースチップとコアチップ間の複数の貫通電極にそれぞれ関する複数の電流パスで大きなAC特性の差がないことの確認試験を行えるようにする。

【解決手段】インターフェースチップ及びコアチップと、これらを電気的に接続するそれぞれが貫通電極を含む測定対象信号線130及び基準信号線131と、を備え、インターフェースチップは、信号発生回路100が発生したテストクロックをコアチップへ送出し、コアチップは、信号発生回路101がテストクロックから所定の測定信号を発生し、且つ所定の測定信号を測定対象信号線130及び基準信号線131へ同時に送出し、更に、インターフェースチップは、更に、測定対象信号線130及び基準信号線131を介して入力した複数の所定の測定信号の位相差をオペアンプ117によって検出し、判定回路102が試験結果を出力する。

(もっと読む)

半導体装置

【課題】 パッケージに封止される半導体素子は、使用環境によって湿度の影響を受けて、半導体素子の劣化が起こることがある。パッケージに実装することが容易で、半導体素子周囲の湿度・水分量を測定・記録できる湿度センサを得る。

【解決手段】 半導体基板2上に形成した絶縁膜7の上に、水溶性金属の薄膜8を用いた湿度センサ6を形成し、水溶性金属の薄膜8の抵抗を測定する。水溶性金属とは、電位−pH図において、電位がゼロ、pHが7付近で腐食域にある金属を意味する。

(もっと読む)

LSI,鉄道用フェールセーフLSI,電子装置,鉄道用電子装置

【課題】従来のフェールセーフLSIは、チップ内のプロセッサや比較回路の配置について言及されていたが、パッケージの信号ピン配置までは言及されていなかった。また、多様な周辺回路や高速な外部メモリへの対応も考慮されていなかった。

【解決手段】2つのプロセッサからの出力を照合して一本化された内部インタフェースを共通系内部バスに接続し、その共通系内部バスに複数の外部インタフェース回路を接続する。また、2つの系統に関する信号ピンをパッケージの対角に配置するともに、それらの間に共通系に関する信号ピンを配置するようにする。

(もっと読む)

201 - 220 / 1,067

[ Back to top ]