Fターム[5F038DT12]の内容

Fターム[5F038DT12]に分類される特許

41 - 60 / 1,067

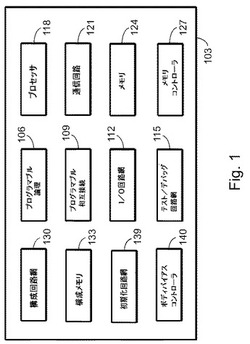

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

半導体装置

【課題】セキュリティ情報を格納した領域への物理的な破壊攻撃を、従来よりも簡単な手法で検知する。

【解決手段】半導体装置1において、第1の機能モジュール3は、正常に動作しているか否かのテスト対象となる。第2の機能モジュール2は、第1の機能モジュール3にテストデータを出力し、テストデータに応じて第1の機能モジュールから出力された出力信号が正常なデータパターンと一致するか否かを判定する。第3の機能モジュール7は、耐タンパ性を必要とする。シールド配線SLは、基板に対して垂直方向から見たときに第3の機能モジュール7が設けられた領域を覆うように設けられ、その両端部は第1の機能モジュール3と接続される。シールド配線SLが断線しているとき、上記の出力信号は正常なデータパターンと一致しなくなる。

(もっと読む)

半導体装置

【課題】出力端子に接続される内部回路の動作開始を早く行うことができる定電圧発生回路を備えた半導体装置を提供する。

【解決手段】クロック信号VOSCが入力されると、内部の複数のノードにおいてポンピング動作を行い、入力端子に供給される電荷を複数のノードを介して出力端子へと順次転送し、出力端子から出力電圧を発生する昇圧回路20と、出力電圧が予め設定された電圧に達した場合、非活性レベルの検知信号VUPTを出力する電圧検出回路30と、検知信号が活性レベルの場合、クロック信号を昇圧回路へ出力し、検知信号が非活性レベルの場合、クロック信号の昇圧回路への出力を停止するクロック信号制御回路40と、を備え、クロック信号制御回路は、検知信号が非活性レベルであっても、入力される制御信号RESETTのレベルに応じてクロック信号を昇圧回路へ出力する。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

検証装置、検証方法及びプログラム

【課題】検証する範囲を少なくして、検証コストや検証時間の増大を抑制する。

【解決手段】抽出部12が、第1のクロック信号で動作する回路部21と、第2のクロック信号で動作する回路部22とを含む検証対象回路(論理回路20)から、ハンドシェイクの手順に従って回路部21と回路部22間でのデータの送受信を行うハンドシェイク部23を抽出し、検証部13が抽出されたハンドシェイク部23の信号が、その手順を満たすかを検証し、手順を満たさない信号があるとき、回路部21と回路部22のうち当該信号を出力する側で、当該信号が手順を満たさなくなる条件が回路動作時に起こり得るか検証する。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】不良電流パスの選別に要する時間を短縮する。

【解決手段】半導体装置は、それぞれ少なくとも1つの貫通電極を含み、インターフェイスチップ内に第1のノードn1を有する複数の電流パス101Xと、互いに異なる複数の電圧値からなる比較電圧DACOUTを生成する比較電圧生成部102と、複数の電流パス101Xそれぞれの第1のノードn1の電圧TSVCXと、比較電圧DACOUTの上記複数の電圧値それぞれとを比較し、比較の結果を示す比較結果信号CMPXを電流パス101Xごとに出力する比較部103と、比較結果信号CMPXに応じて、複数の電流パス101Xのそれぞれが高抵抗化しているか否かを示す結果信号RESLTXを生成する結果信号生成部104とを備える。

(もっと読む)

半導体装置

【課題】データの誤書換を防止することが可能な低消費電力の半導体装置を提供する。

【解決手段】マイクロコンピュータ1は、電源電圧VCCが正常範囲から外れた場合にリセット信号REを出力する電圧検出器2と、各々がデータを不揮発的に記憶する複数のメモリセルを含むメモリアレイ5と、イレーズコマンドまたはプログラムコマンドに応答して、電圧検出器2の応答時間TR以上の保留時間TSだけ経過した後にデータのイレーズまたはプログラムを実行し、リセット信号REに応答してリセットされる制御部7とを備える。したがって、電圧検出器2の応答時間TRが長い場合でも、データの誤書換を防止できる。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置及びその評価方法

【課題】大規模な被測定素子の測定を短時間で行うことができ、且つ、高抵抗状態の短絡不良が発生した場合でも、不良の発生箇所を容易に特定することができるようにする。

【解決手段】直列接続された第1の被評価パターン101、及び該第1の評価パターンと隣接して配置された第2の被評価パターン102と、第2の被評価パターンとそれぞれ電気的に接続可能に設けられたノード情報伝達回路105とを備えている。第1の被評価パターンと第2の被評価パターンとは、互いに対向する領域により被測定素子103が構成されている。複数の第1の被評価パターンには、外部から所定の電圧が印加され、第2の被評価パターンとノード情報伝達回路とが電気的に接続されることにより、被測定素子の評価結果である第2の被評価パターンの電位がノード情報伝達回路に入力される。ノード情報伝達回路は入力された第2の被評価パターンの電位を外部へ順次出力する。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体集積回路装置

【課題】 リングオシレータ回路を構成するインバータを切り替えることで変化する配線抵抗や配線容量などの変動をリングオシレータ回路の出力信号から得られる周波数変動から除去し、半導体回路の内部に実装されているトランジスタのランダムばらつきを検出する半導体回路装置を提供する。

【解決手段】 入力された信号の論理レベルを反転させる複数の回路素子を直列に接続した発振回路と、発振回路の出力周波数をカウントする信号処理部と、第1の回路素子に電源電圧を印加する電源端子と接地端子との間において互いに並列に接続された、互いの特性を比較した場合においてばらつきを持つ複数のトランジスタと、複数のトランジスタのうち、選択制御部によってそれぞれの1つが順番に選択されるようにタイミング信号を制御する。

(もっと読む)

容量測定回路、半導体装置および容量測定方法

【課題】本発明は、特別な装置を用いずに、微細素子の容量を直接測定することができる容量測定回路、半導体装置および容量測定方法を提供する。

【解決手段】本発明に係る容量測定回路1は、少なくとも1つの第1リングオシレータ(測定用リングオシレータ4)と、第1周辺回路部(測定用周辺回路部5)と、第2リングオシレータ(参照用リングオシレータ6)と、第2周辺回路部(参照用周辺回路部7)とを備えている。第1リングオシレータおよび第2リングオシレータに電力を供給する電源と、第1周辺回路部および第2周辺回路部に電力を供給する電源とは異なる。容量測定回路1は、第1出力信号の周波数および第1リングオシレータに流れる電流値より算出した第1容量から、第2出力信号の周波数および第2リングオシレータに流れる電流値より算出した第2容量を差引くことで測定対象の容量を測定することができる。

(もっと読む)

半導体集積装置及びテスト方法

【課題】従来技術では、アナログ信号を扱うアナログモジュールの試験に適用できず、試験時間の短縮ができないという問題点がある。

【解決手段】アナログ信号を入力し、同一機能を備える複数のアナログモジュールと、テスタからの選択信号に応じて、前記複数のアナログモジュールの出力のうち第1のアナログモジュールの出力、もしくは、前記第1のアナログモジュール以外の出力を選択する信号選択回路と、前記信号選択回路が選択したアナログモジュールの出力を加算する加算回路を備える算出回路と、を有する半導体集積装置。

(もっと読む)

半導体集積回路及び半導体集積回路の動作制御方法

【課題】温度が高くなりすぎたりあるいは低くなりすぎたりする発振状態となって、半導体集積回路が誤動作、動作停止等することを防止する。

【解決手段】実施形態によれば、半導体集積回路1は、回路部の温度又は動作速度に基づいて、温度が安定するように、回路部の制御パラメータを調整して、フィードバック制御を実行する制御部と、温度の時系列データである第1の履歴データと、制御パラメータの時系列データである第2の履歴データとを含む履歴データを格納する履歴レジスタ17と、履歴データからフィードバック制御の有効性を判定する有効性判定部24とを有する。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

41 - 60 / 1,067

[ Back to top ]