Fターム[5F043FF02]の内容

Fターム[5F043FF02]に分類される特許

1 - 20 / 49

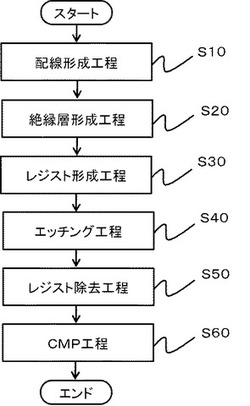

半導体装置の製造方法

【課題】配線幅が異なる第1及び第2の配線を有する配線パターンの上に形成された絶縁層を、十分に平坦化すること。

【解決手段】基板上に、第1の配線及び第1の配線よりも配線幅が小さい第2の配線を有する配線パターンを形成する配線形成工程S10と、配線パターンの上から、第1の絶縁層及び第2の絶縁層をこの順に形成する絶縁層形成工程S20と、第2の絶縁層の上に、配線パターンの反転パターンを有するレジストパターンを形成するレジスト形成工程S30と、第2の絶縁層の方が第1の絶縁層よりもエッチングされやすい条件で等方性エッチングするエッチング工程S40と、レジストパターンを除去するレジスト除去工程S50と、を有する半導体装置の製造方法。

(もっと読む)

複合基板の製造方法

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成するステップと、犠牲層の一部が露出するように半導体結晶層をエッチングし、半導体結晶層を複数の分割体に分割するステップと、転写先基板に接することとなる半導体結晶層形成基板側の第1表面と、第1表面に接することとなる転写先基板側の第2表面と、が向かい合うように、半導体結晶層形成基板と転写先基板とを貼り合わせるステップと、半導体結晶層形成基板および転写先基板をエッチング液に浸漬して犠牲層をエッチングし、半導体結晶層を転写先基板側に残した状態で、転写先基板と半導体結晶層形成基板とを分離するステップと、を有し、前記半導体結晶層が、GexSi1−x(0<x≦1)からなる、複合基板の製造方法を提供する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

低反射基板の製造方法、および光起電力装置の製造方法

【課題】短時間のエッチングで低反射化が可能な低反射基板の製造方法を得る。

【解決手段】低反射基板の製造方法は、(100)単結晶シリコン基板1aを挟んだ両面の上に不純物拡散層2を形成する工程と、両面に形成された不純物拡散層の上に50nm以上400nm以下の膜厚のシリコン酸化膜3を形成する工程と、一方の上のシリコン酸化膜に対してブラスト加工を施すことにより、シリコン酸化膜を貫通して不純物拡散層に達する開口4を形成する工程と、基板をシリコン酸化膜が耐性を有するアルカリ水溶液に浸漬して開口を介したアルカリ水溶液による不純物拡散層のエッチングを行うことにより、シリコン酸化膜と基板との間にアンダーカットを形成する工程と、引き続きアルカリ水溶液により、アンダーカットの空間的な広がりに依存しつつシリコン(111)面を露出させる異方性エッチングを行う工程と、その後にシリコン酸化膜を除去する工程とを含む。

(もっと読む)

埋め込みヘテロ構造半導体レーザの製造方法及び埋め込みヘテロ構造半導体レーザ

【課題】耐圧特性を十分に維持しながら放熱特性を向上させることが可能な埋め込みヘテロ構造半導体レーザの製造方法等を提供する。

【解決手段】埋め込みヘテロ構造半導体レーザの製造方法は、半導体基板1上に半導体積層9とマスク層11を形成する工程と、マスク層11を用いて半導体構造物10をエッチングすることにより、第1方向に沿って延びる半導体メサ15であって、第1方向と直交する第2方向において被エッチング領域17と隣接する半導体メサ15を形成する工程と、マスク層11を半導体メサ15上に残した状態で、被エッチング領域17の第1領域17A1のみに埋め込み層19Aを形成する工程と、上部電極25を形成する工程と、を備える。上部電極25は、半導体メサ15の上面15Tから被エッチング領域17の第2領域17A2に亘って形成されることを特徴とする。

(もっと読む)

エッチングパターン作成装置、エッチングパターン作成方法、プログラムおよびコンピューター読み取り可能な記録媒体

【課題】サイドエッチングを考慮してエッチングパターンを作成することのできるエッチングパターン作成方法、エッチングパターン作成装置、プログラムおよびコンピューター読み取り可能な記録媒体を提供しようとするものである。

【解決手段】 導体パターンを含む設計データから上記導体パターンの外形形状であるアウトライン形状を作成するアウトライン形状作成手段と、上記アウトライン形状作成手段により作成されたアウトライン形状に対する補正値を設定する設定手段と、上記設定手段により設定された補正値分だけ上記アウトライン形状作成手段により作成されたアウトライン形状を補正してエッチングパターンを作成するエッチングパターン作成手段とを有するようにしたものである。

(もっと読む)

半導体装置の製造方法

【課題】レーザ光の照射を利用したエッチング加工による半導体装置の製造方法であって、複雑形状や深くて大きい除去領域等のエッチング加工が必要な広範囲の半導体装置の製造に適用可能で、高いエッチング速度が得られる半導体装置の製造方法を提供する。

【解決手段】単結晶シリコンからなる基板10に対して、焦点位置を移動させてレーザ光Lをパルス照射し、前記単結晶シリコンを部分的に多結晶化して、前記単結晶シリコン中に連続した改質層11を形成する改質層形成工程と、前記改質層11をエッチングして除去するエッチング工程と、を備える半導体装置の製造方法とする。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

メンブレン部を有する半導体装置とその製造方法

【課題】メンブレン部と梁部の下部のSi(100)基板そのものを除去してブリッジ構造を形成するためのSi異方性ウェットエッチングの処理時間を短縮できる半導体装置技術を提供すること。

【解決手段】メンブレン部51と梁部52〜55は、Si(100)基板の<100>方向に形成され、梁部52〜55はメンブレン部51の対向する二辺上でのみメンブレン部51を支持し、梁部52〜55の最短部分の長さが幅よりも長い構成となっている。メンブレン部51上には赤外線を検出するための感熱部90(赤外線センサーの場合)と赤外線吸収膜91が形成され、検出した赤外線によって発生される信号を、配線92、93が感熱部90からメンブレン部51、梁部53、55を通って外部へと導いている。メンブレン部51は底面保護層94、層間膜95、上面保護層96によってエッチング溶液から保護されている。

(もっと読む)

半導体装置の製造方法

【課題】窒化物半導体層を有する半導体装置を低コストで製造する。

【解決手段】基板上に第1の窒化物半導体の犠牲層を形成する犠牲層形成工程と、前記犠牲層上に第2の窒化物半導体層を形成し、前記第2の窒化物半導体層上に窒化物半導体層を積層した積層窒化物半導体層を形成する積層半導体形成工程と、前記犠牲層の表面が露出するまで、前記第2の窒化物半導体層及び前記積層窒化物半導体層をエッチングすることによりトレンチを形成し、前記トレンチ及び前記積層窒化物半導体層表面に接続電極を形成する接続電極形成工程と、前記接続電極の形成された前記基板を電解液に浸漬させ、前記電解液に対し前記接続電極に電位を印加し、前記犠牲層を除去し前記基板を剥離する犠牲層除去工程とを有することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

電解質に対する半導体構造の局部的な電気化学的ポテンシャルの改変による光電気化学(PEC)的エッチングの制御

【課題】選択性が高い光誘導性のエッチングを達成するために、電解質に対する半導体構造の局部的電気化学的ポテンシャルを戦略的に改変することを含む、III−窒化物半導体構造を製造するための方法を提供すること。

【解決手段】上記方法は、電気的抵抗層または半導体構造の中の電子のフローを妨げる層の適切な配置によって、および/またはPECエッチングの間に、半導体構造の特定の層と接触するカソードを配置することによって、半導体構造または半導体デバイスの電気的ポテンシャルを局部的に制御し、水平方向および/または垂直方向の光電気化学(PEC)的エッチング速度を局部的に制御する。

(もっと読む)

MEMSデバイスの検査構造及び方法

【課題】半導体装置においてアンダーエッチングを測定する。

【解決手段】構造40a〜40e中に犠牲層41c〜41eの存在を判断する方法で、該方法は、平面にてなる主面を有する基板に配置された少なくとも一つの構造40a〜40eを設け、ここで上記少なくとも一つの構造は、少なくとも一つの側部で固定され、所定の大きさの力、例えば機械的力が当該構造に作用し、基板に垂直な部品を有し、かつ、基板の上記平面に垂直な上記少なくとも一つの構造の歪みを判断し、かつ、上記少なくとも一つの構造の歪みを、上記基板と上記構造との間の犠牲層の存在に関連づけることを備える。

(もっと読む)

半導体素子の製造方法

【課題】ELOG法を用いて形成された開口面積の大きい空洞を半導体層内部に導入することにより成長用基板をウェットエッチング処理または外力印加によって容易に剥離することができる半導体素子の製造方法を提供する。

【解決手段】

成長用基板上を部分的に覆う選択成長用のマスクを成長用基板上に形成する。次に、成長用基板上のマスクで覆われていない非マスク部において、マスクの膜厚よりも厚い緩衝層を成長させた後、緩衝層の表面に所定のファセットを表出させる。次に、緩衝層を起点として半導体膜を横方向成長させてマスク上部に空洞を形成しつつマスクを覆う横方向成長層を形成する。横方向成長層の上にデバイス機能層をエピタキシャル成長させる。空洞形成工程は、互いに異なる成長速度で半導体膜の成長を行う第1ステップおよび第2ステップを交互に複数回実施する。

(もっと読む)

シリコン微細構造体の製造方法及び微細流路デバイスの製造方法

【課題】曲線を含む輪郭からなるシリコン単結晶微細構造を基板空洞上に形成するに際して,ドライエッチングを使わず1回のフォトリソグラフィだけで形成可能なシリコン構造体の製造方法を提供する。

【解決手段】シリコン窒化膜301を介し2枚のシリコン基板20、30を貼り合わせた後一方の基板を微小構造体の厚さにあわせて薄膜化する.特定の結晶異方性エッチング液で薄膜部をエッチングすることにより曲線輪郭の構造体を加工する。その後,LOCOS酸化膜を選択的に微細構造体表面に形成しこれを保護膜として,通常の結晶異方性エッチング液で構造体下部のエッチングを行ことにより,1枚のフォトマスクのみで膜厚を制御した構造体の加工ができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属層にノッチ形状が形成されず、多結晶シリコン層から金属層へのシリコンの拡散を防止したMIPSゲート構造を有する半導体装置を提供する。

【解決手段】MIPSゲート構造を有する半導体装置の製造方法において、MIPSゲートの作製工程は、半導体基板上に、ゲート絶縁膜、メタル層、および多結晶シリコン層を順次堆積する工程と、多結晶シリコン層の上に形成したエッチングマスクを用いて、多結晶シリコン層をエッチングする工程と、メタル層を選択的にエッチングして、下方に向かって側壁がテーパ状に張り出したメタル層を残す工程と、多結晶シリコン層の側壁を含む平面から外方に突出したメッキ層のテーパ部を酸化して、酸化テーパ部とする酸化工程と、酸化テーパ部をエッチングで除去する除去工程とを含む。

(もっと読む)

異方性エッチングによる構造体の作製方法、及びエッチングマスク付きシリコン基板

【課題】構造体を異方性エッチングする際の補正エッチングマスクを配置するスペースをより小さくできて、シリコンウェハ上により多くの構造体を配置できる構造体の作製方法、エッチングマスク付きシリコン基板を提供する。

【解決手段】構造体の作製方法、エッチングマスク付きシリコン基板において、単結晶シリコン基板100上に、凸部コーナーを持つ目標形状に対応する基本エッチングマスク103と、補正エッチングマスク107を形成する。補正エッチングマスク107の第1の部分は<110>方向に伸び、両方の端部が基本エッチングマスクに連結され、1つの端部が基本エッチングマスク103の凸部コーナーに連結される。第2の部分は、第1の部分の<110>方向に伸びる辺で第1の部分に接合し、第2の部分は1つの凸部コーナーを有し、開口部は、第1の部分と第2の部分が接合する境界を跨いで伸びる。

(もっと読む)

基板構造体及びこの基板構造体を除去する方法

【課題】 半導体層と基板をエッチングで分離する効率を高め、かつプロセスにかかる費用を抑えることができる、基板構造体を除去する方法の提供。

【解決手段】 本発明の基板構造体を除去する方法は、基板上にフォトリソグラフィーエッチング方式で複数の柱状体を製作し、前記複数の柱状体上にIII族窒化物半導体層を成長させ、化学エッチング方式で複数の柱状体をエッチングし、前記III族窒化物半導体層と前記基板を分離する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、絶縁膜のホール内に形成される導電性プラグ等の導電性材料のコンタクト抵抗が基板面内でばらつくのを防止すること。

【解決手段】シリコン基板30の上方に第1の層間絶縁膜45を形成する工程と、第1の層間絶縁膜45の上方に強誘電体キャパシタQを形成する工程と、強誘電体キャパシタQの上方に、水素バリア絶縁膜55、57、62と第2の層間絶縁膜58とを有する積層膜を形成する工程と、エッチングにより積層膜にホール58b、58cを形成する工程と、ホール58b、58c内に金属配線(導電性材料)69を埋め込む工程とを有し、ホール58b、58cを形成する工程において、水素バリア絶縁膜55、57、62のエッチングを、第2の層間絶縁膜58のエッチングとは異なるエッチング手法で行う半導体装置の製造方法による。

(もっと読む)

半導体をその基板から分離する方法

【課題】 本発明の目的は半導体をその基板から分離する方法を提供することである。

【解決手段】 複数の棒状体を基板上に形成し、複数の棒状体上で半導体層をエピタキシー成長させ、更に、複数の棒状体の間の空隙にエッチング液を注入することによって、半導体層をその基板から分離する。複数の棒状体の間の空隙がエッチングの反応面積を大幅に増加させることができるため、本発明による方法によれば、エッチングによって半導体層を基板から分離する効率を向上させ、製造工程のコストを低減させることができ、しかも、基板に使われる材料も前記分離方法に制限されない。

(もっと読む)

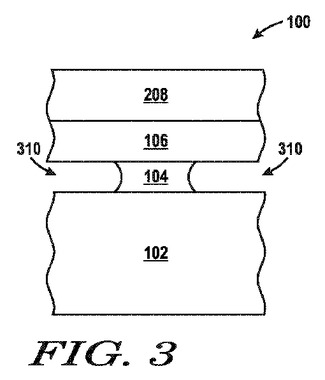

ディファレンシャルエッチング層の除去を含む電子デバイスの形成方法

電子デバイスを形成する方法は、基材、ディファレンシャルエッチング層、及び半導体層を含むワークピースのある面上に金属層を形成する工程を含むことができる。ディファレンシャルエッチング層は基材と半導体層の間に位置することができ、半導体層はワークピースのある面に沿って位置することができる。本方法は、基材と半導体層の間からディファレンシャルエッチング層の少なくとも大部分を選択的に除去する工程、及び基材から半導体層と金属層を分離する工程をさらに含むことができる。選択的な除去は、ウェットエッチング、ドライエッチング、又は電気化学的な技術を用いて実施することができる。特定の実施形態では、金属層のメッキ及びディファレンシャルエッチング層の選択的な除去に同じメッキ浴を使用してもよい。  (もっと読む)

(もっと読む)

1 - 20 / 49

[ Back to top ]