Fターム[5F044AA07]の内容

ボンディング (23,044) | ワイヤによるペレット電極との接続構造 (951) | パッケージの配線部との接続 (63)

Fターム[5F044AA07]の下位に属するFターム

配線部が多層のもの (10)

Fターム[5F044AA07]に分類される特許

1 - 20 / 53

半導体チップの実装方法、及び光電変換モジュールの製造方法

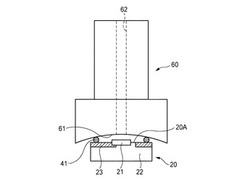

【課題】フェイスアップ実装方法において、低コストで半導体チップを損傷する虞のない半導体チップの実装方法を提供する。

【解決手段】主平面20Aと、裏面20Bとを備えた半導体チップ20を基板10上に実装する半導体チップ実装方法であって、半導体チップ20の主平面20Aにチップ側バンプ41を形成するチップ側バンプ形成工程と、ピックアップ手段60の吸着面61にチップ側バンプ41を当接させながら半導体チップ20をピックアップするピックアップ工程と、裏面20Bが基板10と対向するように半導体チップ20を基板10の所定位置に載置する載置工程と、半導体チップ20を基板10に固定する固定工程と、を有する半導体チップの実装方法により上記課題が解決される。

(もっと読む)

電子装置およびその製造方法

【課題】防振部材を介して電子部品をケーシングに収容するとともに、電子部品とケーシングとをワイヤボンディングにより接続してなる電子装置において、ワイヤボンディング時にワイヤボンディング荷重の逃げを無くしつつ、ケーシングの高さばらつきに影響されることなく、入れ子等の支持治具の工夫を不要として、防振部材の剥離を抑制する。

【解決手段】電子部品10の他端面12を支持治具1に対向させた状態で、電子部品10を支持治具1上に搭載し、次に電子部品10の一端面11上に防振部材40を搭載し、次に、支持部22および開口部24を有するケーシング20を用い、防振部材40を介して電子部品10の一端面11と支持部22とが対向した状態で、ケーシング20を電子部品10に取り付けるとともに支持治具1上に支持し、続いて、開口部24を介して、電子部品10の一端面11とケーシング20との間をワイヤボンディングする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の小型化を図る。

【解決手段】半導体チップ5の複数の第1電極パッドaと配線基板2の複数の第1接続部3b1を、複数の第1ワイヤ10b1を介して電気的に接続する工程と、第2電極パッドbと前記配線基板の複数の第2接続部3b2を、第2ワイヤ10b2を介して電気的に接続する工程と、第3電極パッドcと前記配線基板の複数の第3接続部3b3を、第3ワイヤ10b3を介して電気的に接続する工程とを有し、前記複数の第1ワイヤ10b1のそれぞれを前記複数の第1接続部3b1のそれぞれの前記第1部分に接続し、前記第3ワイヤ10b3を前記第3接続部3b3の前記第2部分に接続し、前記複数の第110b1、第210b2および第3ワイヤ10b3は、平面視において、前記半導体チップ5の前記第2辺の中心部を経由し、かつ前記第2辺と直交する仮想線5sに対して鋭角をなす角度で、前記複数の電極パッドから延在させる。

(もっと読む)

半導体装置

【課題】配線の引き回しが容易で、ワイヤショートの発生を低減された半導体装置を提供する。

【解決手段】半導体装置は、第1及び第2電極パッド列13、14に各々近接して配置された第1及び第2接続パッド群21、22を有する絶縁基板11の開口部12から、第1電極パッド列13及び第2電極パッド列14が露出されるように半導体チップが搭載され、第1接続パッド群21は、第1電極パッド列13の電極パッドにワイヤaを介して接続された第1の接続パッド24と、第1の接続パッド24に接続されかつ第1電極パッド列13の電極パッドと接続されていない第2の接続パッド25とを有し、第2接続パッド群22は、第2電極パッド列14の電極パッドにワイヤbを介して接続された第3の接続パッド26と、第2の接続パッド25にワイヤBを介して接続されかつ第2電極パッド列22の電極パッドに接続されていない第4の接続パッド27とを有する。

(もっと読む)

半導体チップ、及びこれを備えた半導体装置

【課題】半導体チップをフェースアップ方式、フェースダウン方式で実装した際の配線遅延の変動や配線の引き回しが複雑になることを抑えることが可能な半導体チップ及び半導体装置を提供する。

【解決手段】本発明にかかる半導体チップ1は、複数の電極端子を備えた半導体チップであって、複数の電極端子のうち、固定端子2が半導体チップ1の対称線を中心として半導体チップ1の幅の50%の範囲内に配置されている。また、本発明にかかる半導体装置は、このように固定端子2が配置された半導体チップ1と、半導体チップ1が実装されると共に、半導体チップ1が備える固定端子2と接続される電極パッド21を備えるパッケージ基板10と、を有する。

(もっと読む)

ワイヤボンディング方法及びワイヤボンディング用のレーザ溶接装置

【課題】Cu系のボンディングワイヤとCu系の端子との間に広くて浅くて強固な接合を得ること。

【解決手段】X−Yステージ20上で半導体チップ12の各電極パッド14とそれに対応する端子(電極パッド14,リード18)とを電気的に接続するために、ビーム断面が矩形状のグリーンパルスレーザ光SHGを用いて断面矩形の平角型Cu(またはCu合金)のボンディングワイヤ22の先端部を各端子(電極パッド14,リード18)にレーザ溶接で接合する。

(もっと読む)

半導体装置

【課題】半導体素子の電極と配線部材を繋ぐ金属細線において、異径の金属細線を配置して、パワーモジュールの小型化を図るとともに、機械的信頼性の高い半導体装置を提供する。

【解決手段】スイッチング素子1、このスイッチング素子1に形成された第一の電極4と第二の電極5、これら各電極と配線部材とを接続する金属細線、前記スイッチング素子1、配線部材、金属細線を収納する外装ケース7、及び前記外装ケース7に封入する封入樹脂11を有する半導体装置であって、第一の金属細線6は第二の金属細線9よりも線径が大きく、かつ長くし、第一の金属細線6の近傍に略並行に第二の金属細線9を配線した。

(もっと読む)

半導体装置

【課題】ワイヤボンディング処理に適し、小型化を実現でき、回路設計容易な半導体素子および半導体キャリアを提供する。

【解決手段】半導体キャリア6と半導体素子1とがワイヤ9で電気的に接続される構造の半導体装置において、半導体キャリア6の電極4と半導体素子1の電極2を、隣接間の距離およびワイヤ間の最小距離が、ワイヤボンディング処理に必要な距離以上であり、かつ、半導体素子1の電極2の一部が同一直線上にない位置に配置することにより、半導体素子1を小型化する。

(もっと読む)

高周波半導体装置

【課題】本発明は、ゲートワイヤおよびドレインワイヤのワイヤ長を延長できる高周波半導体装置を提供することを目的とする。

【解決手段】キャビティを有するパッケージと、該キャビティ底面に配置され、上面にゲート電極、ソース電極、ドレイン電極を有する半導体チップと、該キャビティ底面に配置されたゲートフレーム、ドレインフレーム、ソースフレームと、該ゲート電極と該ゲートフレームを接続するゲートワイヤと、該ドレイン電極と該ドレインフレームを接続するドレインワイヤと、該ソース電極と該ソースフレームを接続するソースワイヤとを備える。そして、該半導体チップは、該半導体チップが該キャビティ底面の中央部に配置された場合と比較して該ゲートワイヤおよび該ドレインワイヤの長さが長くなるように該中央部から所定のオフセットだけ離間して配置されたことを特徴とする。

(もっと読む)

端子、実装構造体及びこれらの防食方法

【課題】中空パッケージにおける端子とワイヤーとの異種金属接合部分の腐食を、容易にかつ確実に防止できる端子、実装構造体及びこれらの防食方法を提供する。

【解決手段】端子4を構成する金属層2上に、フッ素系樹脂又はシリコーン系樹脂などからなる撥水撥油性樹脂層3を形成する。また、このような端子4を備える素子5を、中空状のパッケージ本体10に搭載し、超音波を利用したワイヤーボンディング法により、素子5の端子4とパッケージ本体10のインナーリード11とを、第一の金属とは主成分が異なる第二の金属からなるワイヤー15を介して相互に接続して実装構造体とする。

(もっと読む)

めっき析出物

【課題】厚みの均一な無電解パラジウムめっき皮膜が形成された被めっき体を提供する。

【解決手段】被めっき体と、無電解ニッケルめっき皮膜と、無電解ニッケル-パラジウムめっき皮膜と、無電解パラジウムめっき皮膜と、置換金めっき皮膜と、を有し、前記無電解ニッケルめっき皮膜、前記無電解ニッケル-パラジウムめっき皮膜、前記無電解パラジウムめっき皮膜及び前記置換金めっき皮膜の順序に積層され、前記置換金めっき皮膜が最表層に位置してなる、めっき析出物。

(もっと読む)

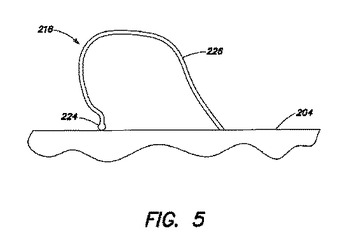

一体化された干渉シールドを備えた半導体パッケージおよびその製造方法

半導体モジュールパッケージのための一体化された電磁干渉(EMI)シールドである。一体化されたEMIシールドは、パッケージの基板内の接地面とパッケージのモールド化合物の上端上にプリントされた導電層との間に電気的に接続された複数のワイヤボンドばねを含む。ワイヤボンドばねは、ワイヤボンドばねの上端と導電層との間の電気的接続によるコンタクトを与えるばね効果を生じさせる、定められた形状を有する。ワイヤボンドばねを、モジュールパッケージ内において、パッケージに含まれる装置すべてまたはその一部の周りのいずれかの場所に配置することにより、これらの装置の周りに完全なEMIシールドを形成する。  (もっと読む)

(もっと読む)

半導体装置

【課題】高周波特性の劣化を抑え、小型化を図った半導体装置を提供する。

【解決手段】配線基板1の主面上に搭載された半導体チップ5は、第1の増幅手段PW1の入力部と電気的に接続するチップ側入力用電極6Aと、第2の増幅手段PW2の出力部と電気的に接続するチップ側出力用電極6Bを含み、配線基板1は、主面上に、基板側入力用電極2Aと基板側出力用電極2Bとを有し、第1の増幅手段PW1の出力部は第2の増幅手段PW2の入力部と電気的に接続され、チップ側入力用電極6Aと基板側入力用電極2Aは入力用ワイヤ7Aによって電気的に接続され、チップ側出力用電極6Bと基板側出力用電極2Bは、出力用ワイヤ7Bによって電気的に接続され、入力用ワイヤ7Aは半導体チップ5の平面形状を成す一対の第1の辺のうちの一つの辺を跨ぐように形成され、出力用ワイヤ7Bは一対の第2の辺のうちの一つの辺を跨ぐように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、電極端子に対するワイヤボンディングを行う半導体装置の製造方法に関し、特に電極端子を固定した状態で超音波振動を伴うワイヤボンディングを行う半導体装置の製造方法を提供することを目的とする。

【解決手段】電極端子のワイヤボンディング面の裏面が半導体装置のケースと接するように、該電極端子を該ケースに装着する工程を備える。さらに該ワイヤボンディング面の一部に固定用冶具を押し当て、該電極端子を該ケースと該固定用冶具で挟んで固定した状態で該ワイヤボンディング面のうち該固定用冶具が押し当てられていない部分に対し、超音波印加を伴うワイヤボンディングを行う工程とを備えることを特徴とする。

(もっと読む)

表面実装用の水晶発振器

【課題】ICチップの水晶端子の位置に拘わらず、水晶片の励振電極の一方が発振用増幅素子の出力側となる生産性に富んだ表面実装用の水晶発振器を提供する。

【解決手段】一対の励振電極を両主面に有する水晶片2とICチップ1とを容器本体3に収容し、IC端子中の水晶端子6(x、y)と前記励振電極とはワイヤーボンディングを経て電気的に接続し、前記ICチップの出力側に接続した一方の励振電極は前記容器本体の開口端面側に位置し、前記一方の励振電極にイオンビームを照射して発振周波数を調整してなる表面実装用の水晶発振器において、前記一対の励振電極はそれぞれ前記ICチップの入出力端となる水晶端子に選択的に導通可能な第1と第2の回路端子10(x1、x2)又は10(y1、y2)に接続し、前記発振用増幅素子の入出力端となる前記水晶端子は前記第1と第2の回路端子のいずれかに前記ワイヤーボンディングによって接続した構成とする。

(もっと読む)

半導体装置および当該半導体装置の製造方法

【課題】高周波特性を重視する回路に接続される電極パッドの寄生容量の増大を抑える。

【解決手段】半導体チップ100は、複数の内部回路と、外縁近傍に設けられ、それぞれ複数の内部回路のいずれかに電気的に接続された複数の電極パッドとを含む。複数の電極パッドは、プローブが接するためのプローブ用領域104と、プローブ用領域104とは異なる位置に設けられ、ワイヤ108をボンディングするためのボンディング用領域とを含む長パッド102と、ボンディング用領域を含むがプローブ用領域を含まない構成とすることにより長パッド102よりもパッド面積が小さく形成された高周波信号を入出力する高周波用の小パッド110とを含む。

(もっと読む)

半導体装置とワイヤボンディング方法

【課題】 半導体装置が機能するのに必要な半導体構造を製造できる有効面積を拡大する技術を提供する。

【解決方法】 本発明の半導体装置2では、活性領域4に第1ボンディングパッド24が形成されていると共に、不活性領域6に第2ボンディングパッド26が形成されている。本発明の半導体装置2では、外部回路と半導体装置2を、第1ボンディングパッド24を用いて接続する場合、一旦を外部回路とボンディングしたワイヤ14を第1ボンディングパッド24でボンディングする。さらにそのワイヤ14を、第1ボンディングパッド24で切断しないで第2ボンディングパッド26にボンディングする。第1ボンディングパッド24でワイヤ14を切断しないので、第1ボンディングパッド24の面積を縮小することがでる。これにより、半導体構造を製造できる有効面積である半導体領域8を拡大することができる。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】回路基板に電子部品が実装されて構成される半導体装置において、容易に確認することができる管理用情報を付与すること。

【解決手段】回路基板(20)に電子部品(10)が実装されて構成される半導体装置(1)であって、前記電子部品と前記回路基板の電極同士をワイヤボンディング方式により接続する接続部材(30)に、当該半導体装置の管理用情報が付与されていることを特徴とする、半導体装置。電子部品は、半導体素子(チップ)、LSI、IC、コンデンサ、リレー、コネクタ等、如何なるものであってもよい。

(もっと読む)

多基板ブロック式パッケージおよびその製造方法

【課題】多基板ブロック式パッケージおよびその製造方法を提供する。

【解決手段】チップ40の能動面400を複数の機能ブロックに分割し、該機能ブロックのそれぞれは、ボンディングワイヤ41により対応する基板31に電気的に接続され、該機能ブロックのそれぞれが独立したシステムを有しているため、システム設計者は、該機能ブロックのそれぞれに独立した回路レイアウトを設計することができ、基板31またはその他のシステムに制限されることなく、配線がしやすくなり、該パッケージを小さく薄くなるように設計することを可能にするとともに、該機能ブロックのそれぞれと対応する基板31とはそれぞれ独立しているため、基板31同士は互いに影響しあうことはなく、好ましい交換性、信頼性及び封止面積の縮小が図られるようになる。また、前記の多基板ブロック式パッケージの製造方法が提供される。

(もっと読む)

ユニバーサル配線ラインを含む半導体チップ、半導体パッケージ、カード及びシステム

【課題】ユニバーサル配線ラインを含む半導体チップ、半導体パッケージ、カード及びシステムを提供する。

【解決手段】半導体基板上の集積回路部と、半導体基板上に集積回路部と電気的に連結されるように配された一つ以上の導電性パッドと、半導体基板上に一つ以上の導電性パッドと離隔されて配され、集積回路部と電気的に絶縁された複数のユニバーサル配線ラインと、を備える半導体チップである。

(もっと読む)

1 - 20 / 53

[ Back to top ]