Fターム[5F044LL04]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | ハンダ付け方法 (478)

Fターム[5F044LL04]の下位に属するFターム

加熱方法 (145)

Fターム[5F044LL04]に分類される特許

161 - 180 / 333

リフロー装置及び半導体装置の製造方法

【課題】リフロー工程でのフラックスの飛散エリアを十分に縮小できるリフロー装置及び半導体装置の製造方法を提供する。

【解決手段】本発明に係るリフロー装置は、フレキシブルテープ3上に素子5を実装する際、前記素子5と前記フレキシブルテープ3とを半田ペースト6によって接合するためのリフロー装置であって、前記半田ペースト6を加熱して溶融させる本ヒート用ステージ2と、前記本ヒート用ステージ2によって前記半田ペースト6を加熱する際に前記素子5及び前記半田ペースト6を覆うフラックス飛散防止治具4と、を具備することを特徴とする。

(もっと読む)

半導体モジュール及びその製造方法

【課題】リフロー処理によりモジュール基板に反りが発生した場合での半導体モジュールの実装歩留の低下を抑制する。

【解決手段】半導体モジュール70には、実装部品1乃至3が実装される。半導体モジュール70に設けられる基板41のリード端子と基板41上に載置される実装部品の外部端子とを接続するはんだは、基板41の反りが大きい中央部の単位面積当たりのはんだ量を多くし、端部側になるほどはんだ量を減少させ、基板41の反りが小さい端部の単位面積当たりのはんだ量を少なくしている。

(もっと読む)

半導体装置の製造方法および装置

【課題】装置の構成が簡単かつ安価な半導体装置の製造方法および装置等を提供するものである。

【解決手段】バンプ同士またはバンプと電極部とを近接させて接合する工程において、特に熱による半田の溶融による接合に関して、近接していく側の位置をモニタリングすることで、接合状態を検査することを特徴とする構成である。

(もっと読む)

実装済み基板およびその製造方法

【課題】実装部品の製造プロセスを変更しなくても、またアンダーフィル剤を使用しなくても、実装部品と配線基板との接合信頼性を高め易い実装済み基板を得ること。

【解決手段】所定パターンの配線が形成された配線基板1と、該配線基板に表面実装された実装部品20とを備え、配線基板の部品実装面MS2と実装部品の下面との間に形成された複数のはんだ接合部SJ2,SJ2,……により実装部品が配線基板に接合されている実装済み基板30を得るにあたり、リフローさせたはんだに部品実装面側から実装部品側に向かう外部応力を付与し、この状態で当該はんだを固化させてはんだ接合部とする。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】金属ワイヤ等の多数の接合部材を電極表面に簡易且つ精度良く接続することができる半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】半導体素子2又は回路基板の表面に形成された複数の端子1に、導電材料3を介して接合部材4を接続する半導体装置の製造方法は、前記複数の接合部材4を保持する工程と、保持された前記接合部材4を、前記接合部4材の融点未満の温度に加熱する工程と、前記端子1の表面に形成された前記導電材料3に前記接合部材4を接触させることにより、前記導電材料3を溶融させて、前記端子1に前記接合部材4を接続させる工程と、を含む。

(もっと読む)

半導体装置、及びその製造方法、並びにそれに用いるはんだ供給装置

【課題】半導体パッケージを基板に実装するに際し、はんだ付け時の擬似接触、未はんだ、及びブリッジによるはんだ付け不良を防止することが可能な半導体装置、及びその製造方法、並びにそれに用いるはんだ供給装置を提供することを課題とする。

【解決手段】半導体パッケージ10を基板20に実装するに際して、はんだ供給装置40により複数のランド端子21・21・・・上に半導体パッケージ10のバンプ11・11・・・の形状に応じてクリームはんだ粒3・3・・・を供給し、当該供給されたクリームはんだ粒3・3・・・により各ランド端子21・21・・・上に形成されるクリームはんだ4・4・・・、半導体パッケージ10及び基板20をリフロー等して加熱することにより、半導体パッケージ10のバンプ11・11・・・と基板20のランド端子21・21・・・とをはんだ付けして構成する。

(もっと読む)

半導体装置の製造方法、半導体装置の洗浄方法および洗浄装置

【課題】半導体装置の回路基板と半導体素子との隙間の洗浄効果を高める。

【解決手段】回路基板2に半導体素子3を実装する半導体装置1の製造方法において、回路基板2に形成された電極21および半導体素子3に形成された半田バンプ31の少なくとも一方にフラックス7を供給する工程と、フラックス7を供給した後、電極21と半田バンプ31とを接合する工程と、電極21と半田バンプ31とを接合した後、回路基板2と半導体素子3との隙間に蒸気81を供給して、回路基板2と半導体素子3との隙間を洗浄する工程と、を含む。

(もっと読む)

液状封止樹脂組成物、半導体装置および半導体装置の製造方法

【課題】優れたフラックス残渣の溶解または拡散作用を有する液状封止樹脂組成物を提供し、かつフラックス剤を用いる工程を経て製造される半導体装置の信頼性を向上すること。

【解決手段】半田リフローをする際にフラックス剤を使用して、半導体素子と相手体とを半田バンプで接続した後、前記半導体素子と前記相手体との間を封止するために用いる液状封止樹脂組成物であって、前記液状封止樹脂組成物に用いるエポキシ樹脂とアミン硬化剤との150℃におけるゲルタイムが、1000秒以上10000秒未満であることを特徴とする液状封止樹脂組成物。

(もっと読む)

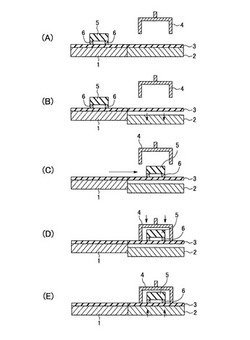

電子装置の製造方法

【課題】接着剤後入れ工法における接着剤未充填の電子装置搬送時に接合部が破損し易いという課題と、接着剤先入れ工法における実装基板と電子部品との空間部に充填される接着剤に未充填部が発生し易いという課題とを同時に解決する。

【解決手段】実装基板に第1の接着剤を塗布する塗布工程と、接続パッドとバンプとが接触するように実装部に電子部品を載置した後、電子部品の反実装面に加熱ヘッドを押し付けて電子部品を加熱し、第1の接着剤を硬化させて実装基板と電子部品とを接着する第1の加熱工程と、減圧下で実装基板と電子部品との間の空間部に第2の接着剤を充填する充填工程と、その実装基板および電子部品を減圧下から大気圧下に戻した後、電子部品の反実装面に加熱ヘッドを押し付けて電子部品を加熱し、第2の接着剤を硬化させると共に、接続パッドとバンプとを接合させる第2の加熱工程とを備える。

(もっと読む)

半導体モジュールの製造方法

【課題】半導体チップと基板との間の隙間に充填されるアンダーフィルが不所望領域へ広がりにくい半導体モジュールの製造方法を提供すること。

【解決手段】フリップチップ実装された半導体チップ5と対向する基板1上の銅箔パターン2(電極20群やグラウンド電極21)がビア導体3を介して基板1の底面側の銅箔パターン2(電極22群やグラウンド電極23)と導通されており、この底面側の銅箔パターン2に熱源8を接触させた状態で、半導体チップ5と基板1との間の隙間に液状のアンダーフィル6を注入して充填させる。また、基板1上には予め所定領域に半田レジスト膜4を形成しておき、半導体チップ5と対向する方形状領域Aに形成された半田レジスト膜4の外周部で基板面露出部10に隣接する枠状部分4aが、銅箔パターン2と重なり合わずに半導体チップ5の実装領域を全周に亘って包囲するようにしておく。

(もっと読む)

半導体製造装置および半導体装置の製造方法

【課題】生産性を損なうことなく、配線基板等の反りおよび配線基板と半導体チップ等との接合不良が低減された半導体装置を提供する。

【解決手段】一または二以上の配線基板303と、少なくとも二つ以上の半導体チップ301または半導体装置とを同時に加熱する一括リフロープロセスにより、配線基板に半導体チップまたは半導体装置を加熱接合するための半導体製造装置であって、該半導体製造装置が配線基板303を吸着固定するステージ300と、半導体チップ301または半導体装置を非接触で加熱する熱源100と、熱源100の熱量を制御する制御部とを少なくとも備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数の第1の凹部と第1の凹部内に形成された第2の凹部とを有した支持基板を準備した後に(ステップS1)、第2の凹部に、第1の電極層を配置する(ステップS2)。次に、複数の第2の電極層を配設した半導体素子を、支持基板に接近させる(ステップS3)。次に、加熱処理により、第2の電極層を支持基板の第1の凹部に受容しながら、第2の電極層内に第1の電極層の一部を貫入する(ステップS4)。そして、第1の電極層及び第2の電極層を冷却し、支持基板を第1の電極層及び第2の電極層から離反する(ステップS5)。

(もっと読む)

電子回路モジュール及び電子回路モジュールの製造方法

【課題】高温にしたノズルで半導体チップ等を吸着し、基板の電極部上に設けた半田を加熱してフリップチップ実装する場合、電極間での温度上昇にばらつきがあると、接続の信頼性が低下してしまう。

【解決手段】半導体チップがフリップチップ実装される配線基板12上には、配線パターン18〜34の一部に電極部18a〜34aが確保されており、各電極部18a〜34a上に半田36が塗布されている。このとき半田36は、配線パターン18〜34への熱の分散(逃げ)を考慮して予めの使用量(塗布量)が個別に調整されている。例えば、面積の大きい配線パターン18では半田36の使用量を少なくし、その他の配線パターン20〜34では半田36の使用量を多くする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子をフリップチップで実装を行う際、加熱におけるはんだの量の減少を生じず、半導体素子と回路基板の接続不良がないようにする手段を提供する。

【解決手段】貫通孔を有する第1フィルム101及び第2フィルム103を互いに貫通孔の開口が大きい面101a、103aを向かい合せて、その真ん中にはんだボール102を載置し、半導体素子104の電極106と回路基板100の電極105をそれぞれ第1フィルム及び第2フィルムの貫通孔の開口小さい面101b、103bを位置合わせ、真空で加圧及び加熱により、半導体素子、フィルム、回路基板が互いに接着すると同時に、はんだボールを介して、半導体素子の電極と回路基板の電極が電気的に接続される。

(もっと読む)

はんだペースト、電気基板、及び電気基板の製造方法

【課題】隣接する導通部が電気的に接続してショートするのを抑制することができるはんだペースト、電気基板、及び電気基板の製造方法を得る。

【解決手段】隣接する夫々の導通部の間が狭い場合は、はんだペースト10の塗布範囲がばらつくことで、導通部同士が電気的に接続してショートすることが考えられる。しかし、隣接す導通部の間に、磁力によって磁性体粉末16が集められる。磁性体粉末16は、磁性部16Aを絶縁層16Bで覆うことで構成されている。つまり、隣接する導通部34同士の間が狭い場合でも、磁性体粉末16の絶縁層16Bにより、隣接する導通部34が電気的に接続してショートするのを抑制することができる。

(もっと読む)

液状封止樹脂組成物及びそれを用いた半導体装置の製造方法

【課題】 フリップチップパッケージの端子接合と封止をリフロー加熱により一括に行うことができ、高接続信頼を有する液状封止樹脂組成物及びそれを用いた半導体装置の製造方法を提供する。

【解決手段】 リフロー加熱によりフリップチップパッケージの端子接合と封止を同時に行うことができる液状封止樹脂組成物において、リフロー加熱が半田の融点よりも低い温度のリフロー予備加熱温度と半田の融点よりも高い温度のリフロー本加熱温度を有し、前記液状封止樹脂組成物の粘弾性測定における粘度が、リフロー予備加熱時の温度範囲で1Pa・s以下で、リフロー本加熱時のピーク温度でのゲルタイムが30s以下である液状封止樹脂組成物。

(もっと読む)

半導体装置、半導体装置の実装方法、および半導体装置の実装構造

【課題】回路基板への実装が容易で、実装信頼性の高い半導体装置を実現する。

【解決手段】本発明の半導体装置1は、半導体基板2と、電極21に設けられるAuバンプ3とを備える。Auバンプ3は、突起3aを備え、Auバンプ3の周囲には、Ni層31を介して半田層32が形成されている。突起3aにより低加重で容易に半導体装置1を実装することができる。また、回路基板6上の電極61に供給する半田62の量を少なくしても、実装後は十分な量の半田33で接合することができる。さらに、Ni層3がバンプ食われを防止するので、高い実装信頼性を確保することができる。

(もっと読む)

電子部品実装装置及び実装方法

【課題】狭ピッチのバンプを有するハイエンド電子部品を実装可能な電子部品の実装方法及び実装装置を提供する。

【解決手段】ヘッドツール3の吸着ノズル11により吸着保持された電子部品1の各半田バンプ1bと回路基板4の各半田部2の当接を検出した後、各半田バンプ1b及び各半田部2を加熱により溶融させ、ヘッドツール3の吸着ノズル11による電子部品1への吸着保持の解除のタイミングを、半田の溶融中に解除するのではなく、半田が溶融後冷却されて固化した後に解除を行う。

(もっと読む)

二重ポスト付きフリップチップ相互接続

パッケージ化された超小型電子アセンブリは、前面(122)と、前面(122)から離れる方に延伸している複数の第1の固体金属ポスト(110)と、を有している超小型電子素子(104)を備えている。第1のポスト(110)の各々は、前面(122)の方向における幅および前面(122)から延びる高さを有しており、この高さ(H2)は、幅(W1)の少なくとも半分になっている。上面(101)と、上面(102)から延伸して第1の固体金属ポスト(110)に接合されている複数の第2の固体金属ポスト(108)と、を有している基板(102)も設けられている。  (もっと読む)

(もっと読む)

実装基板

【課題】半田が溶融する時の電子部品14の中心軸のズレを抑制し且つ電子部品14の回転方向のズレを許容する。

【解決手段】電子部品14の電極は第1〜第4の半田付け位置P1〜P4において第1〜第4のランド部13a〜13dに接続され、第1の半田付け位置P1と第3の半田付け位置P3は電子部品の対角上に配置され、第2の半田付け位置P2と第4の半田付け位置P4は電子部品の他の対角上に配置され、第1のランド部13aは、第1の半田付け位置P1から+Y方向に向けて延長され、第2のランド部13bは、第2の半田付け位置P2から+Y方向に対して略90度の角度に向けて延長され、第3のランド部13cは、第3の半田付け位置P3から+Y方向に対して略180度の角度に向けて延長され、第4のランド部13dは、第4の半田付け位置P4から+Y方向に対して略270度の角度に向けて延長されている。

(もっと読む)

161 - 180 / 333

[ Back to top ]