Fターム[5F044LL09]の内容

ボンディング (23,044) | フェイスダウンボンディング (4,630) | 異方性導電材料によるもの (820)

Fターム[5F044LL09]に分類される特許

801 - 820 / 820

ICチップおよび表示装置

【課題】 ICチップの接続品質を均一且つ安定させ、接続信頼性を高めることを目的とする。

【解決手段】 半導体基体2と、その上に形成されている回路形成層3の表面に複数のバンプ4とを有し、基板の電極端子に実装されるICチップ1において、複数のバンプは、実装後のICチップの反りに応じて半導体基体の表面からの高さをそれぞれ異ならせる。

(もっと読む)

半導体装置

【課題】 異方性導電部材を用いて半導体チップと回路基板を異方性導電粒子の捕捉数を増大させ、かつ、絶縁性を低下させずに接続することを目的とする。

【解決手段】 複数の突起状電極が形成された半導体装置において、粒子の流動を阻害する形状の突起状電極5が形成された半導体チップ1と、配線層3が形成され、表面に前記突起状電極に対応した複数の回路基板電極が形成された回路基板4と、絶縁性樹脂2及びこの絶縁性樹脂中に分散された導電性粒子6からなり、前記半導体チップと前記回路基板とを熱圧着することにより、前記突起電極5と前記回路基板電極3との間に前記導電性粒子6を捕捉させて前記半導体チップ1と前記回路基板4とを接合する異方性導電部材2とを有する構成とする。

(もっと読む)

実装基板、および表示装置

【課題】異方性導電膜を確実に実装領域に仮留めすることが可能で、これによりICチップやFPCを接続状態良好に実装することが可能な実装基板、およびこの実装基板を用いた表示装置を提供する。

【解決手段】フィルム状の異方性導電膜3を介してICチップ33が実装されるものであって、配線が設けられた支持基板2と、配線の端子11を露出させる開口部を有して支持基板2上を覆う有機絶縁膜12とを備えた表示パネル(実装基板)において、ICチップ33が実装される有機絶縁膜12側の第1搭載部7に、フィルム状の異方性導電膜31を密着させるための密着領域14が設けられている。この密着領域14は、異方性導電膜31の配置部である第1搭載部7の端部に設けられ、有機絶縁膜12よりも異方性導電膜31との密着性が良好な材料パターンとして金属パターン15が設けられている。

(もっと読む)

有機−無機複合体およびその製造方法

【課題】従来とは全く異なる形態の異方導電性シートを得ることを介して、他の用途へも適用可能な有機−無機複合体およびその製造方法を提供すること。

【解決手段】有機樹脂からなるフィルムに複数の貫通孔11が形成されてなる分離膜10と、上記貫通孔11に充填された無機粒子12とを有する有機−無機複合体1。当該有機−無機複合体1の好適な製造方法である、有機樹脂からなるフィルムに複数の貫通孔11が形成されてなる分離膜10の一方の主面側に無機粒子と溶剤とを含む懸濁液3を存在させて、分離膜10の他方の主面側から懸濁液の溶剤を通過させかつ無機粒子を実質的に通過させない補助膜2を介して吸引することで分離膜10の貫通孔11に無機粒子12を充填する工程を有する有機−無機複合体1の製造方法。

(もっと読む)

半導体チップの接続構造及びこれに用いる配線基板

【課題】半導体チップの厚みが薄い場合でも優れた接続信頼性を得ることが可能な半導体チップの配線基板への接続構造及びこれに用いる配線基板を提供する。

【解決手段】周縁部に多数の電極2を有する半導体チップ1と、これに相対する電極5を有する配線基板4の接続構造であって、前記半導体チップおよび/または配線基板の電極が絶縁面より突起してなり、少なくとも接続後の半導体チップの周縁部電極に囲まれた領域内に前記突起電極と略同等高さのダミー電極6が設けられ、前記ダミー電極は接続面を投影した時、三角状、エル(L)字状のいずれかもしくはこれらの2種が接続領域内に複数個存在し、さらにこれらの頂点が接続領域の中央部に向けて形成されており、厚みが0.3mm以下の前記半導体チップと配線基板とが接着剤11で接続されてなる半導体チップの接続構造。

(もっと読む)

実装構造およびその製造方法

【課題】半導体装置と回路基板との間の接続部位におけるショートの防止。

【解決手段】端子電極2を有する半導体装置100が、入出力端子電極8を有する回路基板9に実装され、端子電極2と入出力端子電極8とが対向配置されて電気接合層13を介して電気接続されている。IC基板1の一面1aに設けられた端子電極2と、一面1aに設けられたパッシベーション4と、パッシベーション4を覆う保護膜5とを有する。端子電極2の上部はパッシベーション4と保護膜5とが除去されており、端子電極2上に凹部45が形成されている。電気接合層13は、その周囲が凹部45によって囲まれることで周囲への流出が阻止される。

(もっと読む)

回路接続用接着剤

【課題】 熱膨張率差に基づく内部応力による接続抵抗の増大、接着剤の剥離、チップや基板の反りの発生が抑制された回路接続用接着剤を提供する。

【解決手段】 相対峙する回路電極を加熱、加圧によって、加圧方向の電極間を電気的に接続する加熱接着性接着剤において、前記接着剤中には、少なくとも平均粒径10μm以下のゴム粒子が分散され、熱によって硬化する反応性樹脂、及び潜在性硬化剤としてスルホニウム塩を含有し、該接着剤のDSC(示差走査熱分析)での発熱開始温度が60℃以上で、かつ硬化反応の80%が終了する温度が260℃以下である回路接続用接着剤。

(もっと読む)

電気光学装置、実装構造体及び電子機器

【課題】

信号減衰が極力抑制された、基板上に実装された半導体素子と配線基板とが接続してなる実装構造体、信号減衰が極力抑制された表示特性が良好な電気光学装置、その電気光学装置を用いた電子機器を提供すること。

【解決手段】

電気光学物質を保持する基板20と、基板20上に設けられた基板側第1配線及び基板側第2配線25と、基板20上に配置された半導体素子30と、半導体素子30の基板側の面に設けられた第1入力用バンプ及び第2入力用バンプと、半導体素子30の基板20側の面に設けられ、基板側第1配線と接続する出力用バンプと、基板20上に実装されたベース基材41と、ベース基材41に設けられ、第1入力用バンプと電気的に接続する第1配線42aと、ベース基材41に設けられ、基板側第2配線25を介して前記第2入力用バンプと電気的に接続する第2配線42bとを具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体チップの絶縁膜にLow−kなどの脆い材料を用いてもクラックや剥離が生じない半導体装置およびその製造方法を提供する。

【解決手段】電極パターン6が形成された基板5などの被搭載体の上に半導体チップ1が搭載された半導体装置を、半導体チップ1がその電極面に背反する背面において凹状の支持フレーム10の内底面に固定され、支持フレーム10の端部が基板5の電極面に固定されることで、半導体チップ1のAl電極2上に形成されたはんだバンプ4と、対応する電極パターン6とが所定の間隙にて対向配置され、これら対向配置されたはんだバンプ4と電極パターン6とが、前記間隙に配置された変形容易な導電性樹脂11により電気的に接続された構造とする。半導体チップ1が宙吊りになった状態で、はんだバンプ4と電極パターン6とを導電性樹脂11によって電気的に接続させるので、この接続部分に基板5等の熱膨張・収縮で発生する応力は導電性樹脂11の変形により緩和され、バンプ周辺部への応力集中がなくなり、半導体チップ1の絶縁膜1aの応力破壊を防止できる。

(もっと読む)

異方性導電フィルムによる電極接続体

【課題】 異方性導電フィルム(ACF)による電極接続体において、特にACFの貼付位置に高精度が要求される場合、その貼付位置が適正であるかどうかを高価な設備を新たに導入することなく、目視にて容易に判定できるようにする。

【解決手段】 第1基板(例えば液晶パネル10の端子部12a)に形成されている第1電極群13と、第2基板(例えばフレキシブル基板)に形成されている第2電極群とをACF30を介して電気的・機械的に接続する電極接続体において、上記端子部12aと上記フレキシブル基板の少なくとも一方に、上記ACF30の貼付位置を目視(顕微鏡目視)にて判定可能とする例えば2つのドットマークMJ1,MJ2を含むフィルム位置判定マークMJを設ける。

(もっと読む)

回路基板及び実装後基板

【課題】 異方性導電膜に孔が発生することを防止する回路基板及び該回路基板に集積回路素子を実装した実装後基板を提供する。

【解決手段】 導電性パターン3及び被覆膜2が積層された基板1に異方性導電膜4を転写する場合、被覆膜2の開口部21が矩形状をなすため、開口部21の角部において異方性導電膜4が基板1又は導電性パターン3に密着できず、気泡6、6、…を生じる。異方性導電膜4が転写された基板1にIC5を実装する場合、IC5の上面から所定の温度及び圧力でIC5を基板1に押圧して熱圧着を行う。熱圧着時に加えられる熱のため、気泡6、6、…が膨張する。膨張した気泡は、基板1の開口部21の角部に設けられた貫通孔11、11、…を通って基板1の外部に抜けるため、気泡が膨張して異方性導電膜4を破って孔が発生することを防止できる。

(もっと読む)

異方性導電膜貼付方法

【課題】 生産性の向上による高性能化を確実に図ることのできる異方性導電膜貼付方法を提供する。

【解決手段】 異方性導電膜貼付方法は、貼付部位Faを被着部Pcに対向し、貼付部位Faおよび被着部Pcの両者を対向配置された接離可能な貼付ヘッド2および支持台3によって挟持するとともに貼付部位Faを加熱し、該挟持・加熱状態で搬送する。

(もっと読む)

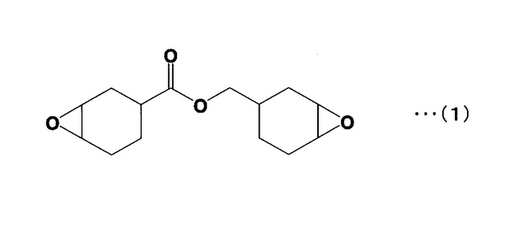

エポキシ樹脂組成物並びに半導体装置及びその製造方法

【課題】フリップチップ実装による半導体装置の製造効率を改善するため、圧接工程において短時間で硬化し、ボイドレスの優れた接着性を備えた硬化樹脂層を形成できるエポキシ樹脂組成物を提供する。

【解決手段】エポキシ樹脂及び硬化剤を含有すると共に室温で液状であるエポキシ樹脂組成物に関する。硬化剤として、2−メチルイミダゾールと下記化学式(1)で示される脂環式エポキシとの付加反応物を用いる。このエポキシ樹脂組成物を用いてフリップチップ実装を行えば、動作信頼性の高い半導体装置を効率よく製造することができる。

【化1】 (もっと読む)

(もっと読む)

半導体チップの接続構造及びこれに用いる配線基板

【課題】 半導体チップの厚みが薄い場合でも優れた接続信頼性を得ることが可能な半導体チップの配線基板への接続構造及びこれに用いる配線基板を提供する。

【解決手段】半導体チップ1と配線基板4の接続構造であって、半導体チップおよび/または配線基板に突起電極2が設けられ、突起電極表面の平均粗さ(JIS、B0601、10点平均粗さ)が0.5μm以上であり、接続後の半導体チップの周縁部電極に囲まれた領域内に突起電極と略同等高さのダミー電極6が設けられ、ダミー電極は接続面を投影した時、三角状、エル(L)字状のいずれかもしくはこれらの2種、または、半円弧状、コの字状のいずれかもしくはこれらの2種が複数個存在し、さらにこれらの頂点が接続領域の中央部に向けて形成されており、厚みが0.3mm以下の前記半導体チップと配線基板とが接着剤11で接続されてなる半導体チップの接続構造。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の高速伝送、多層化対応を図り、半導体チップ設計の制約を減らす。

【解決手段】半導体装置は、少なくとも2つの積層された半導体チップ1,2と、半導体チップ1,2同士を電気的に接続する接続構造とを有している。接続構造は、第1の半導体チップ1に設けられた第1の電極11と、第2の半導体チップ2に設けられた第2の電極21と、第1、第2の半導体チップ1,2の間に挟まれた接合ボード5とを有している。接合ボード5は、第1の電極11と対向する第1の接続電極52と、第2の電極2と対向する第2の接続電極53と、接合ボード5を貫通するスルーホール54と、スルーホール54と第1、第2の接続電極52、53とを電気的に接続する配線55,56とを備えている。

(もっと読む)

所定領域上に密封構造を有する電子パッケージ及びその方法

光感知素子用電子パッケージが提供される。パッケージは、所定の波長周囲内の光に対して実質的に透明な物質の基板を含むように形成される。また、パッケージは、その前面側上に定義された光感知領域を有する1つ以上の光感知台を含むように形成される。該光感知台は、光感知領域の周囲に配置された複数の配線接合によって前記基板に実装され、それによって前記光感知台の前記前面側は、前記基板の前記前面の表面から間隙を置いて離隔される。密封構造が光感知台と基板との間で実質的に密封された方式で内部の空洞を連続的に捕獲するように、密封構造が形成されてその周囲の間隙の一部を満たすように配線接合の周囲から延長される。この内部の空洞は、光感知台の光感知領域と通じる。 (もっと読む)

配線端子を具備する電子装置

接続抵抗を低くし腐蝕防止を図ることのできる端子構造及びこれに基づく電子装置を提供することを目的とする。基板8に支持される透明導電層10と、透明導電層10上に延在し透明導電層10よりも抵抗率の低い材質の金属層20とを有し、透明導電層10は、金属層20よりも耐酸化性が高く、周辺回路(50)と接続するための端子10Tを形成する、電子装置。金属層20は、透明導電層10の端子10T外の延在部10L上、及び/又は透明導電層10の端子10Tの領域内において透明導電層10を外部へ露出させるべき結合領域11の周辺又は近傍に延在し、透明導電層10の端子10Tの少なくとも一部及び金属層20全体を被覆し透明導電層10の端子10Tの領域内において結合領域11を除く領域に延在する電気的絶縁層30が設けられている。

(もっと読む)

(もっと読む)

基板上に異方的導電性フィルムを形成するための方法

本発明は、電気絶縁材料層と導電性貫通インサートとを具備してなる異方的導電性フィルムを製造するための方法に関するものであって、本発明による方法においては、a)基板上に、複数の貫通穴を有した少なくとも1つの材料層を形成し、ここで、この少なくとも1つの材料層を「穴開き層」と称することとし、b)貫通穴を充填することによって、導電性インサートを形成する。本発明による方法においては、さらに、導電性インサートの第1端部を部分的に被覆するマスクを形成し、導電性インサートの第1端部のうちの、被覆されていない部分に対して、エッチングを施し、これにより、導電性インサートに、尖った先端を形成する。本発明は、大きな相互接続密度を有した各種素子(チップ、集積回路)の製造に適用される。  (もっと読む)

(もっと読む)

半導体装置および電子機器

【課題】 本発明では剥離技術を用いることにより様々な基板上に薄膜素子を形成し、従来の技術では不可能であると考えられていた部分に薄膜素子を形成することにより、省スペース化を図ると共に耐衝撃性やフレキシビリティに優れた半導体装置を提供する。

【解決手段】 本発明では、剥離技術を用いて一旦基板から剥離させた膜厚50μm以下の素子形成層を基板上に固着することにより、様々な基板上に薄膜素子を形成することを特徴とする。例えば、可撓性基板上に固着された薄膜素子をパネルの裏面に貼り付けたり、直接パネルの裏面に固着したり、さらには、パネルに貼り付けられたFPC上に薄膜素子を固着することにより、省スペース化を図ることができる。

(もっと読む)

半導体装置

【課題】 温度変化の大きい環境下に置かれても、異方導電性フィルムと半導体素子及び/または回路基板との接続界面に破壊が生じることなく、良好な導通特性が維持される半導体装置を提供する

【解決手段】 半導体素子30を異方導電性フィルム10を介して回路基板20と電気的に接続してなる半導体装置であって、異方導電性フィルムは、絶縁性樹脂からなるフィルム基板1中に複数の導通路2が、互いに絶縁されて、フィルム基板の厚み方向に貫通してなるものであり、当該異方導電性フィルムのフィルム基板の面1aと回路基板の基板面21aとの間に隙間Sが形成されている。

(もっと読む)

801 - 820 / 820

[ Back to top ]