Fターム[5F044QQ03]の内容

ボンディング (23,044) | ワイヤレスボンディング用半導体チップ (2,288) | バンプ電極 (1,821) | 材料 (382)

Fターム[5F044QQ03]に分類される特許

1 - 20 / 382

半導体パッケージの製造方法

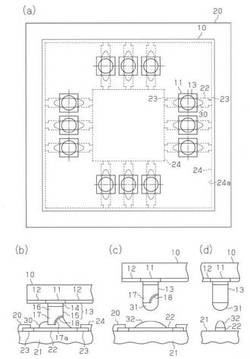

半導体装置、半導体素子、及び半導体装置の製造方法

【課題】はんだによる短絡不良を低減すること。

【解決手段】半導体素子10の一主面には複数の電極パッド11が、半導体素子10の外周に沿って矩形枠状に配列されている。各電極パッド11には、柱状の電極端子13が立設されている。電極端子13の基端部(金属端子部15の基端部16及びバリア層14)は電極パッド11に接続されている。電極端子13(金属端子部15)の先端部17は略半円柱状に形成されている。この略半円柱状の先端部17は、先端面の弧部分が半導体素子10の外側を向くように形成されている。配線基板20の接続パッド22は、配列方向と直交する方向、即ち半導体素子10の外周と直交する方向に沿って延びる矩形状に形成されている。電極端子13は接続パッド22にはんだ30により電気的に接続される。

(もっと読む)

圧電振動デバイスおよび圧電振動デバイスの製造方法

【課題】 金属バンプを介した容器と圧電振動素子や電子部品素子との接合信頼性を向上させた圧電振動デバイスと当該圧電振動デバイスの製造方法を提供することを目的とする。

【解決手段】 水晶発振器1は、水晶振動素子3と集積回路素子4を容器2に収容し、容器2に蓋5を接合することにより、水晶振動素子3および集積回路素子4を気密に封止した構成となっている。容器2の内底面22には凹部を有する電極パッド10が形成され、集積回路素子4の接続端子上には断面視凸状の金属バンプBが配され、金属バンプBの一部が前記凹部の壁面に対応するように埋入した状態で集積回路素子4と容器2とが接合されている。

(もっと読む)

半導体装置およびその製造方法

【課題】固相拡散接合により、プロセス温度が低温化され、プロセス時間が短縮化され、かつフリップチップ構造の半導体装置提供する。

【解決手段】絶縁基板8と、絶縁基板8上に配置された信号配線電極12と、絶縁基板8上に若しくは絶縁基板8を貫通して配置されたパワー配線電極16と、絶縁基板8上にフリップチップに配置され、半導体基板26と、半導体基板26の表面上に配置されたソースパッド電極SPおよびゲートパッド電極GPと、半導体基板26の裏面上に配置されたドレインパッド電極36とを有する半導体デバイス10と、ゲートパッド電極GP上に配置されたゲートコネクタ18と、ソースパッド電極SP上に配置されたソースコネクタ20とを備え、ゲートコネクタ18とゲートパッド電極GPおよび信号配線電極12、ソースコネクタ20とソースパッド電極SPおよびパワー配線電極16は、固相拡散接合される半導体装置1。

(もっと読む)

三次元実装装置

【課題】半導体デバイスの製造のスループットをさらに向上できるとともに、製造される半導体デバイスの品質の低下を防止できる三次元実装装置を提供する。

【解決手段】三次元実装装置11において、搬送トレイ16は配置面16aaを含む内側トレイ16aを有し、且つ該配置面16aaに配置された8つの積層チップ21を搬送し、チャンバ27は内側トレイ16aを収容し、下部ステージ28はチャンバ27内において内側トレイ16aを載置し、上部ステージ29は、下部ステージ28に載置された内側トレイ16aにおける配置面16aaと平行な押圧面29aを有し、下部ステージ28及び上部ステージ29はそれぞれヒータ33,39を内蔵し、下部ステージ28及び上部ステージ29が間を詰めるように移動する。

(もっと読む)

半導体素子の実装方法

【課題】薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制することを目的とする。

【解決手段】半導体素子を搭載する毎に加圧状態で加熱して仮接合を行い、全ての半導体素子を仮接合した後、一括して加圧状態で加熱して本接合を行うことにより、薄型化,狭ピッチ端子化された半導体素子であっても、生産性を維持しながら、はんだ接合の際の反りを抑制して積層することができる。

(もっと読む)

導電性ペースト、及び該導電性ペーストを焼成して得られる接合体

【課題】加熱・焼結する際に、突沸が発生するのを抑制可能な導電性ペーストを提供する。

【解決手段】金属微粒子(P)と分散媒(D)との割合(P/D)(質量%)が50〜90/50〜10の導電性ペーストであって、該分散媒(D)が有機溶媒、及び突沸抑制溶媒(T)からなる有機分散媒(D1)であり、有機溶媒が(i)常圧における沸点が100℃以上で、かつ分子中に1もしくは2以上のヒドロキシル基(−OH)を有するアルコール及び/もしくは多価アルコールからなる、又は(ii)少なくとも有機溶媒5〜95体積%、並びにアミド基を有する有機溶媒(SA)95〜5体積%からなり、突沸抑制溶媒(T)がヒドロキシル基、及びカルボニル基を有し、かつカルボキシル基を有さず、分子量が50以上で沸点が100℃以上の化合物であり、有機分散媒(D1)中の突沸抑制溶媒(T)の割合(T/D1)(質量%)が2〜25質量%である導電性ペースト。

(もっと読む)

接着剤組成物及びこれを用いた回路接続材料、並びに、回路部材の接続方法及び回路接続体

【課題】200℃程度の高温条件で回路部材同士の接続を行った場合でも、回路部材の反りを十分に抑制できる接着剤組成物及びこれを用いた回路接続材料を提供すること。

【解決手段】本発明の接着剤組成物は、回路部材同士を接着するとともにそれぞれの回路部材が有する回路電極同士を電気的に接続するために用いられるものであって、エポキシ樹脂、エポキシ樹脂硬化剤、及び、架橋反応性基を有し且つ重量平均分子量が30000〜80000であるアクリル系共重合体を含有する。当該接着剤組成物を温度200℃で1時間加熱して得られる硬化物は、−50℃における貯蔵弾性率が2.0〜3.0GPaであり且つ100℃における貯蔵弾性率が1.0〜2.0GPaであるとともに、−50〜100℃の範囲における貯蔵弾性率の最大値と最小値との差が2.0GPa以下である。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】接続信頼性の高い半導体装置を提供する。

【解決手段】半導体部材31と、半導体部材31上に形成されているCuスタッドバンプ41と、Cuスタッドバンプ41と電気的に接続するはんだバンプ44とを備える半導体装置30を構成する。半導体部材31は、受光面と同じ面にガラス基板32と接続される電極45が形成されている。そして、この電極上にフリップチップ接続用のCuスタッドバンプが形成されている。Cuスタッドバンプ41は、はんだバンプ44との接続面に合金層43が形成されている。また、Cuスタッドバンプ41ははんだバンプ44と接触していない表面にめっき層42を備える。

(もっと読む)

半導体装置およびその製造方法並びに電子装置

【課題】素子と基板との接合の際の熱処理に起因した熱応力の緩和をバンプの中央部で行なうこと。

【解決手段】素子10と、基板20と、第1導電体32と、前記第1導電体上に形成された第2導電体34と、前記第2導電体上に形成された第3導電体36と、前記第3導電体上に形成された第4導電体38と、を有し、前記第1導電体と前記第4導電体のいずれか一方が前記素子に接合され、前記第1導電体と前記第4導電体の他方が前記基板に接合され、前記素子と前記基板とを電気的に接続するバンプ30と、を具備し、前記第1導電体および前記第3導電体は、前記第2導電体および前記第4導電体より融点が高く、前記第4導電体は前記第2導電体より融点が高い半導体装置。

(もっと読む)

半導体装置、半導体装置の製造方法及び電子機器

【課題】低いリフロー温度で信頼性良く接合できる接合部を備えた半導体装置、半導体装置の製造方法及び電子機器を提供する。

【解決手段】素子11上に形成された第1電極12と、基板21上に形成された第2電極22との上に、それぞれSn-Bi又はSn-Inを含むはんだ層13、23を形成し、これらのはんだ層13、23の間にSn-Ga合金ボール14を、はんだ層13、23の融点よりも高く、且つSn-Ga合金ボール14の融点よりも低い温度でリフロー接合する。リフロー接合の際にはんだ層13、23とSn-Ga合金ボール14との界面にSn-Bi-Ga合金層15又はSn-In-Ga合金層が形成され、Sn-Ga合金ボール14からのGaを含む融液の拡散が阻止される。

(もっと読む)

半導体装置

【課題】アンダーバリアメタルに起因する応力集中を緩和し、トランジスタの特性の変動を抑制することができるパッド電極構造を備える半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成された電極パッド6と、電極パッド6の上に形成され、且つ、電極パッド6の一部が露出するような第1開口部を有する第1絶縁膜7と、第1絶縁膜の上に形成され、且つ、第1開口部における少なくとも一部が露出するような第2開口部を有する第2絶縁膜8と、第2絶縁膜8及び電極パッド6の上に形成されたアンダーバリアメタル10とを備えている。アンダーバリアメタル10は、第2絶縁膜8の表面における第2開口部の外側である第1領域と電極パッド6の表面における第2開口部の内側である第2領域とにより挟まれる第3領域により分離されている。

(もっと読む)

実装構造体及び実装構造体の製造方法

【課題】バンプ電極と端子との間において十分に高い接合強度を確保し、これによって電気的接続の信頼性を向上した実装構造体、及び実装構造体の製造方法を提供する。

【解決手段】バンプ電極12を有する実装体121を、端子11を有する基板111上に実装した実装構造体である。バンプ電極12は内部樹脂13上に導電膜14が覆われてなり、導電膜14は端子11に直接導電接触し、基板111と実装体121とには、内部樹脂13が弾性変形した状態でバンプ電極12が端子11に導電接触している状態を保持する圧着手段が備えられている。内部樹脂13は、その主断面の形状が底辺13aと外辺13bとによって囲まれており、底辺13aの両端を第1の点30とし、主断面の最大幅となる位置での外辺13b上の点を第2の点31とすると、第1の点30と第2の点31とを結ぶ直線Lと、実装体121の面Sとのなす角θが、鋭角に形成されている。

(もっと読む)

パッケージされたデバイス、パッケージング方法及びパッケージ材の製造方法

【解決課題】特殊な技術や装置を必要とせず、接合の際に電気的な接続を歩留まりよく確立可能な、パッケージされたデバイス及びパッケージング方法並びにそれに用いられるパッケージ材の製造方法を提供する。

【解決手段】電子回路、MEMSその他のデバイスを搭載したデバイス基板10と、ビア配線21を配設してかつキャビティ22を有するパッケージ材20とを接合して成る。ビア配線21と一体化した接続用バンプ24がキャビティ22内に突出しており、かつデバイスに接続された配線接続用パッド12が接続用バンプ24と対向して接続していることにより、接続用バンプ24を経由してデバイスがビア配線21に配線接続している。

(もっと読む)

積層フィルム及びその使用

【課題】3次元実装された半導体素子間の空間の充填を容易かつ確実に行うことができる積層フィルムを提供する。

【解決手段】積層フィルムは、接続用部材41bを介して電気的に接続された半導体素子間の空間を充填するための積層フィルムであって、基材1上に粘着剤層2が積層されたダイシングシートと、粘着剤層上に積層された硬化性フィルム3とを備え、硬化性フィルムの50〜200℃における最低溶融粘度は、1×102Pa・s以上1×104Pa・s以下である。

(もっと読む)

半導体装置の製造方法

【課題】チップ積層体の外部接続用電極として機能する第1のバンプ電極間がショートしないように、第1のバンプ電極に精度よくはんだを形成可能な半導体装置の製造方法を提供する。

【解決手段】ボンディングツール34によりはんだ搭載用基板50の他面を保持すると共に、第2のバンプ電極55に形成されたはんだ57を加熱により溶融させ、はんだ搭載用基板の第2のバンプ電極をチップ積層体40の第1のバンプ電極17と対向配置させる工程と、第2のバンプ電極に形成され、かつ溶融したはんだを、チップ積層体の第1のバンプ電極に接触させた後、チップ積層体からはんだ搭載用基板を離間させることで、第1のバンプ電極にはんだを転写させる工程と、を含む。

(もっと読む)

電子部品の実装方法

【課題】テープ材の電子部品裏面への転写を実質的に無くし、そのテープ材の転写に起因して起こり得る不都合を解消すること。

【解決手段】予めテープ材40(例えば、PTFE)を加熱しておき、さらにこのテープ材40を耐熱性プレート50に対し加圧した後、ツール36との間に加熱されたテープ材40を介在させて吸着保持した電子部品を、加熱圧着により、電子部品の電極端子が絶縁性接合材を通して基板の電極端子に接続されるよう実装を行う。

(もっと読む)

半導体封止用接着剤、半導体装置の製造方法及び半導体装置

【課題】半導体チップ及び基板間や2つの半導体チップ間の接続性を良好にでき、且つ、保存安定性を確保できる半導体封止用接着剤を提供すること。

【解決手段】半導体チップ10及び配線回路基板20のそれぞれの接続部15、32が互いに電気的に接続された半導体装置100、又は、複数の半導体チップのそれぞれの接続部が互いに電気的に接続された半導体装置において、接続部を封止する半導体封止用接着剤40であって、(a)第一級又は第二級窒素原子含有化合物と、(b)エステルと、(c)エポキシ樹脂と、を含有する、半導体封止用接着剤。

(もっと読む)

基板貼り合わせ方法

【課題】搬送中に、位置合わせされた基板と基板との相対位置がずれるといった課題がある。

【解決手段】基板貼り合せ方法は、仮接合部において、複数の基板を重ね合わせて複数の対向面および側面の少なくとも一方の一部を仮接合部材によって接合する仮接合段階と、前記仮接合段階で仮接合された前記複数の基板を、本接合部へ搬送する搬送段階と、前記本接合部において、前記仮接合段階で仮接合された前記複数の基板を本接合部材によって本接合する本接合段階とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】チップとプリント基板間の伝熱ロスの少ないフリップリップ実装を実現できる半導体装置及びその製造方法を提供する。

【解決手段】グラファイトからなる複数のスパイクが表面に形成された基板電極パッドが主面上に配置されたプリント基板と、スパイクの先端に接触する導電性樹脂膜が表面に配置されたチップ電極パッドが、基板電極パッドと対向する主面上に配置されたチップとを備える。

(もっと読む)

1 - 20 / 382

[ Back to top ]