Fターム[5F045AF04]の内容

気相成長(金属層を除く) (114,827) | 被成膜面の組成、基板の特徴、ダミー基板、マスク (7,328) | 被成膜面が半導体であるもの (4,466) | III−V族(GaAs、GaP、InP、GaN等)面への成膜 (1,371)

Fターム[5F045AF04]の下位に属するFターム

3元以上の混晶(GaAlAs等)面への成膜 (282)

Fターム[5F045AF04]に分類される特許

101 - 120 / 1,089

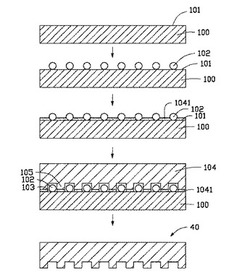

エピタキシャル構造体の製造方法

【課題】本発明は、エピタキシャル構造体の製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板を提供する第一ステップと、前記基板の結晶面に複数の空隙を含むカーボンナノチューブ層を配置し、前記基板の結晶面の一部を前記カーボンナノチューブ層の複数の空隙によって露出させる第二ステップと、前記基板の結晶面にエピタキシャル層を成長させ、前記カーボンナノチューブ層を覆う第三ステップと、前記基板及び前記カーボンナノチューブ層を除去する第四ステップと、を含む。

(もっと読む)

III族金属窒化物の加工された非極性面を有する基板およびその製造方法

【課題】III族金属窒化物の非極性面を有する基板を研磨加工することで極めて平坦な表面を形成しつつ、かつその表面の加工歪みを取り除くことによって、III族金属窒化物の無歪研磨加工面を得ることである。

【解決手段】本方法は、III族金属窒化物の非極性面を有する基板を研磨加工し、前記非極性面の平均表面粗さ(Ra)を1nm以下とする研磨加工工程、次いで基板を不活性雰囲気下で熱処理する熱処理工程、および基板の非極性面を、ハロゲン含有ガスを用いて反応性ドライエッチングするか、または化学機械研磨加工する加工工程を有する。

(もっと読む)

半導体素子の製造方法

【課題】 歩留まりを向上させることができる半導体素子の製造方法を提供する。

【解決手段】 半導体素子の製造方法は、(a)成長基板を準備する工程と、(b)前記成長基板上に半導体層を形成する工程と、(c)前記半導体層を複数の素子部に分割するとともに、各素子部間の半導体層の少なくとも一部を犠牲層として残す工程と、(d)前記半導体層上に金属層を形成する工程と、(e)前記半導体層に、前記金属層を介して支持基板を設ける工程と、(f)前記成長基板に、前記素子部の全部を覆い、かつ前記犠牲層の外縁内に収まるようにレーザーを照射することにより、前記成長基板を前記半導体層から剥離する工程とを含む。

(もっと読む)

半導体バルク結晶および半導体バルク結晶の製造方法

【課題】格子定数が下地基板と略等しい乃至同一の単結晶の化合物半導体結晶をエピタキシャル成長させるに当たり、当該化合物半導体結晶をクラックフリーのものとして大面積のエピタキシャル半導体基板を提供すること。

【解決手段】半導体バルク結晶の製造に際し、下地基板と化合物半導体単結晶との間に、下地基板と化合物半導体単結晶とが直接接する態様で空洞を形成したり、下地基板の主面に凹凸を形成し、さらに、化合物半導体単結晶のエピタキシャル成長方向に直交する結晶軸の下地基板の格子定数a1と化合物半導体単結晶の格子定数a2の差の比率である格子不整合度(2|a1−a2|/[a1+a2])を1×10-3以下とした。上記空洞や凹凸によりエピタキシャル成長途中におけるクラックの発生を抑制することができ、大面積のクラックフリーのエピタキシャル半導体バルク結晶を提供することができる。

(もっと読む)

III−V族発光デバイスを成長させるための基板

【課題】特性および信頼性を低下させることなくIII−V族発光デバイスを成長させるための基板を提供すること。

【解決手段】ホストおよび該ホストに接合されたシード層を含む基板が準備され、次いで、n型領域およびp型領域の間に配置された発光層を含む半導体構造が、前記シード層上に成長される。幾つかの実施形態では、接合層が、前記ホストを前記シード層に結合させる。シード層は、前記シード層に形成される転位によって、または前記シード層と前記接合層の間、即ちこれら二つの層間の界面での滑りによって半導体構造における歪みが解除されるように、前記半導体構造における歪みの緩和のための臨界圧力よりも薄くすることができる。幾つかの実施形態において、前記ホストは、前記接合層をエッチング除去することにより前記半導体構造およびシード層から分離されてよい。

(もっと読む)

複合GaN基板およびその製造方法、ならびにIII族窒化物半導体デバイスおよびその製造方法

【課題】高特性かつ手頃な価格の複合GaN基板およびその製造方法ならびにIII族窒化物半導体デバイスおよびその製造方法を提供する。

【解決手段】本複合GaN基板1は、比抵抗が1Ωcm未満の導電性GaN基板10と、導電性GaN基板10上に配置された比抵抗が1×104Ωcm以上で厚さが5μm以上の半絶縁性GaN層20と、を含む。本III族窒化物半導体デバイス2は、上記の複合GaN基板1と、複合GaN基板1の半絶縁性GaN層20上に配置された少なくとも1層のIII族窒化物半導体層30と、を含む。

(もっと読む)

半導体基板、電界効果トランジスタ、半導体基板の製造方法および電界効果トランジスタの製造方法

【課題】DWB法における貼り合わせ時にIII-V族化合物半導体層が受けるダメージを小さくするとともに、受けたダメージの影響および界面準位の影響を低く抑え、高いキャリアの移動度を有するIII-V族MISFETを提供する。

【解決手段】ベース基板102と第1絶縁体層104と半導体層106とを有し、ベース基板102、第1絶縁体層104および半導体層106が、ベース基板102、第1絶縁体層104、半導体層106の順に位置し、第1絶縁体層104が、アモルファス状金属酸化物またはアモルファス状金属窒化物からなり、半導体層が、第1結晶層108および第2結晶層110を含み、第1結晶層108および第2結晶層110が、ベース基板102の側から、第1結晶層108、第2結晶層110の順に位置し、第1結晶層108の電子親和力Ea1が、第2結晶層110の電子親和力Ea2より大きい半導体基板を提供する。

(もっと読む)

受光デバイス、半導体エピタキシャルウエハ、これらの製造方法、および検出装置

【課題】近赤外域〜遠赤外域にわたって高い受光感度を持ち、製造が容易であり、安定して高品質が得られる、受光デバイス、半導体エピタキシャルウエハ、これらの製造方法、および検出装置を提供する。

【解決手段】III−V族半導体基板と、III−V族半導体基板の上に位置し、(InAs/GaSb)が繰り返し積層された多重量子井戸構造の受光層3とを備え、III−V族半導体基板がInAs基板1であることを特徴とする。

(もっと読む)

窒化アルミニウム単結晶およびその製造方法

【課題】波長240〜300nmの領域における紫外光の透過性に優れた窒化アルミニウム単結晶、該単結晶からなる層を有する積層体、該積層体を製造する方法、および該積層体から紫外光の透過性に優れる窒化アルミニウム単結晶を製造する方法を提供することを目的とする。

【解決手段】

酸素原子、及び炭素原子を含む窒化アルミニウム単結晶であって、酸素原子の濃度を[O]cm−3、炭素原子の濃度を[C]cm−3としたときに、下記式(1)の条件を満足することを特徴とする窒化アルミニウム単結晶。

[O]−[C] > 0 (1)

(もっと読む)

半導体装置

【課題】バッファ層からキャリア層への不純物拡散による悪影響を排除することができる。

【解決手段】このバッファ層20における最下部には超格子層(第1の領域)21が配され、その上には拡散防止下部層22、拡散防止層(第2の領域)23、拡散防止上部層24が順次形成されている。基板11上に形成されたバッファ層20、キャリア層30中においては、バッファ層20中の超格子層21のみに意図的に不純物がドーピングされ、他の層はノンドープである。そのc軸方向が膜厚方向であり、a軸は成長層の面内方向(膜厚方向と垂直な方向)となる。a軸格子定数は膜厚方向にわたりほぼ一定となるのに対し、c軸格子定数は拡散防止層23で極大値をとる。

(もっと読む)

III/V族半導体材料を形成する方法及びそのような方法を用いて形成された半導体構造体

【課題】内部の欠陥数がより少なく且つ/又は減少したIII/V族半導体材料を形成する方法、並びに欠陥数がより少なく且つ/又は減少したそのようなIII/V族半導体材料を含む半導体構造体及び素子が必要である。

【解決手段】三元III族窒化物材料を形成する方法は、チャンバー内で基板上に三元III族窒化物材料をエピタキシャル成長させるステップを含む。エピタキシャル成長は、チャンバー中の窒素前駆体の分圧と1つ又は複数のIII族前駆体の分圧との比較的に高い比を含む前駆体ガス混合物をチャンバー内に準備するステップを含む。少なくとも一部は比較的に高い比のため、三元III族窒化物材料の層は、小さいVピット欠陥をその中に含む高い最終厚さに成長させることができる。そのような三元III族窒化物材料の層を含む半導体構造体をそのような方法を用いて作製する。

(もっと読む)

気相成長装置及び気相成長方法

【課題】 シリコン膜の結晶成長の速度を速くする技術を提供する。

【解決手段】 気相成長装置10は、気相成長室36と、加熱室8と、混合室38と、トリクロロシランガスを貯蔵する第1貯蔵庫42と、塩酸ガスと反応するシラン系ガスを貯蔵する第2貯蔵庫40を備えている。加熱室8は、第1貯蔵庫42と混合室38に連通しており、トリクロロシランガスを加熱した後に混合室38に供給している。混合室38は、第2貯蔵庫40と気相成長室36に連通しており、加熱室8から供給されたガスとシラン系ガスを混合させて、その混合ガス34を気相成長室36に供給している。加熱室8の室内温度は、混合室38の室内温度よりも高い。

(もっと読む)

窒化物半導体構造

【課題】原子レベルで平坦な表面またはヘテロ界面を有する窒化物半導体構造を提供する。

【解決手段】窒化物半導体基板101は、(11−20)面を主方位面とするGaNであり、らせん成分を含む貫通転位104の密度は1×105cm−2であった。該基板上に複数の開口部103(1辺が20ミクロンの正方形)を有するマスク材102(酸化シリコン薄膜、厚さ100nm)が形成されている。該開口部には、n型GaN層106a、アンドープAlN層106b、アンドープGaN層106c、アンドープAlN層106d、および、n型GaN層106eが順次形成されている。様々な条件下で貫通転位104の密度と開口部103の面積との関係を検討すると、貫通転位密度がNcm−2である場合、各開口部103の面積が1/Ncm2以下であれば各開口部103内に形成した窒化物半導体多層薄膜の少なくとも一つの界面が平坦になることを見出した。

(もっと読む)

窒化物半導体発光素子及びその製造方法、並びに、半導体光学装置

【課題】EL発光パターンを改善することにより、発光効率を向上させることが可能な窒化物半導体発光素子を提供する。

【解決手段】この窒化物半導体レーザ素子100(窒化物半導体発光素子)は、成長主面10aを有するGaN基板10と、このGaN基板10の成長主面10a上に成長された窒化物半導体各層11〜18とを備えている。そして、GaN基板10の成長主面10aが、m面に対して、a軸方向およびc軸方向の各方向にオフ角度を有する面からなり、a軸方向のオフ角度が、c軸方向のオフ角度より大きい角度となっている。

(もっと読む)

窒化物半導体薄膜およびその成長方法

【課題】従来よりも原子レベルで平坦な表面を有する窒化物半導体薄膜及びその成長方法を提供する。

【解決手段】ミスカットを有するGaN基板101のステップフロー成長(工程1)により制限領域内に形成されたテラス202に、工程1よりもキャリアガスに含まれる水素の組成を少なくして、トリメチルガリウム(TMG)又はトリエチルガリウム(TEG)を供給し、テラス202の上にGaNの2次元核301を1個以上100個以下発生させる(工程2)。次に、工程2よりもキャリアガスに含まれる水素の組成を多くする(工程3)。これにより、複数の2次元核301が横方向成長して1分子層の厚さの連続的なGaN薄膜302となる。工程2と工程3を交互に繰り返すことにより、2分子層以上の厚さのGaN薄膜303を成長させる。

(もっと読む)

半導体材料の選択堆積方法

【課題】シリコンやゲルマニウムのようなIV族半導体材料を、半導体表面上に、絶縁表面上への堆積無しに選択的に堆積する方法を提供する。

【解決手段】半導体プロセスで半導体材料の選択成長を行う方法が、第1領域11と第2領域12とを含むパターニングされた基板10を提供する工程を含み、第1領域11は露出した第1半導体材料を含み、第2領域12は露出した絶縁材料を含む。この方法は、更に、第2半導体材料の前駆体、Cl化合物とは応性しないキャリアガス、および錫テトラクロライド(SnCl4)を供給することにより、第1領域の第1半導体材料の上に第2半導体材料の膜を選択的に形成する工程を含む。錫テトラクロライドは、第2領域の絶縁材料上への第2半導体材料の堆積を阻害する。

(もっと読む)

積層基板及びその製造方法

【課題】結晶性の炭化アルミニウム層及び窒化ガリウム層を有する積層基板及びその製造方法を提供する。

【解決手段】基板1としてサファイア基板、炭化ケイ素基板または窒化アルミニウム基板の上に結晶性のGaN層10、結晶性のAlC層20を順次積層して配置した

積層基板100であって、炭化アルミニウムの結晶の成長条件としては、アルミニウムを含むガスとしてトリメチルアルミニウムと、炭素を含むガスとしてメタンを供給し、有機金属気相成長法により成長させる。成長温度としては700℃以上が好ましく、さらには1100℃以上が好ましい。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子を提供する。

【解決手段】3次元構造の表面形態を持ち、非極性窒化物半導体で形成された第1非平坦非極性窒化物半導体層;第1非平坦非極性窒化物半導体層の表面の少なくとも一部上に形成されたものであって、複数の固体粒子で形成された第1構造物層;第1非平坦非極性窒化物半導体層及び第1構造物層上に形成された第1非極性窒化物半導体層;を含む半導体素子。

(もっと読む)

窒化物半導体材料の表面処理方法および表面処理システム

【課題】GaNなどの窒化物半導体材料の酸化皮膜形成処理、エッチング処理を半導体材料にダメージを与えることなく効率よく行うことを可能にする。

【解決手段】硫酸濃度が56〜90質量%の硫酸溶液を電解して生成した過硫酸含有硫酸溶液を、窒化物半導体材料に接触させて、前記半導体表面に酸化皮膜を生成する。該処理は、表面処理部2と、電解装置3と、硫酸溶液を表面処理部と電解装置とを含む経路で循環させる循環路10,20,30,31と、表面処理部に供給される過硫酸を含む硫酸溶液を加熱する加熱部22と、電解装置に供給される硫酸溶液を冷却する冷却部32とを備える表面処理システム1で行う。半導体材料のダメージを抑えつつ、酸化が困難であった素材の半導体に安定した酸化膜を形成でき、酸化処理後に安定したエッチングを行うこともできる。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

101 - 120 / 1,089

[ Back to top ]