Fターム[5F045DA67]の内容

気相成長(金属層を除く) (114,827) | 半導体成長層の構造 (3,415) | 半導体成長層の物性 (649) | 結晶欠陥密度・エッチピット密度・表面の面粗さ (221)

Fターム[5F045DA67]に分類される特許

1 - 20 / 221

窒化物半導体構造の製造方法

【課題】平坦な表面を有し、結晶性の高い窒化物半導体下地層を、反りを抑えて、大きな成長速度で成長させることができる窒化物半導体構造の製造方法を提供する。

【解決手段】第3の窒化物半導体下地層を形成する工程において、第3の窒化物半導体下地層の成長時に単位時間当たりに供給されるV族原料ガスのモル量と単位時間当たりに供給されるIII族原料ガスのモル量との比であるV/III比を700以下とし、第3の窒化物半導体下地層の成長時の圧力を26.6kPa以上とし、第3の窒化物半導体下地層の成長速度を2.5μm/時以上とする、窒化物半導体構造の製造方法である。

(もっと読む)

高周波用半導体素子形成用のエピタキシャル基板および高周波用半導体素子形成用エピタキシャル基板の作製方法

【課題】コストメリットがあり、かつ、特性の優れた高周波動作用の半導体素子を実現できるエピタキシャル基板を提供する。

【解決手段】導電性を有するSiCまたはSiからなる基材の上に、絶縁性を有する第1のIII族窒化物からなる下地層をMOCVD法によって、表面に実質的に非周期的な凹凸構造を有するようにかつ、表面の平均粗さが0.5μm以上1μm以下となるように、エピタキシャル形成し、下地層の上に、GaNからなるチャネル層をエピタキシャル形成し、チャネル層の上に、AlxGa1−xN(0<x<1)からなる障壁層をエピタキシャル形成する。

(もっと読む)

ダイヤモンド複合体

【課題】単結晶ダイヤモンドと多結晶ダイヤモンドの双方の利点を活かしながら、更に板状の構造を可能にするために、多結晶ダイヤモンドの研磨の困難性も回避し、研磨が容易なダイヤモンド複合体を提供すること。

【解決手段】少なくとも2種類の結晶性の異なる結晶からなる構造の複合体であり、その内の第一の結晶は高圧合成法により合成した単結晶ダイヤモンドか、あるいは気相合成法により合成した単結晶ダイヤモンドであり、第二の結晶は欠陥を面内に周期的なパターン形状で含む気相合成法により合成したダイヤモンドであり、該第一の結晶及び第二の結晶はいずれも、主面が平行になるように層状に形成されていることを特徴とするダイヤモンド複合体。

(もっと読む)

SiCエピタキシャルウェハ及びその製造方法

【課題】積層欠陥の面密度が低減されたSiCエピタキシャルウェハ及びその製造方法を提供する。

【解決手段】本発明のSiCエピタキシャルウェハの製造方法は、オフ角を有するSiC単結晶基板の成長面に存在する基底面転位(BPD)のうち、SiC単結晶基板上に形成された、所定膜厚のSiCエピタキシャル膜において積層欠陥になる比率を決定する工程と、比率に基づいて、使用するSiC単結晶基板の成長面におけるBPDの面密度の上限を決定する工程と、上限以下のSiC単結晶基板を用いて、比率を決定する工程において用いたエピタキシャル膜の成長条件と同じ条件で、SiC単結晶基板上にSiCエピタキシャル膜を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体発光素子、及びその製造方法

【課題】転位密度の低減を図ることができる半導体発光素子、及びその製造方法を提供することである。

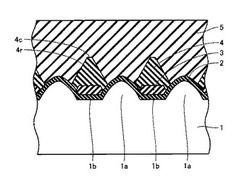

【解決手段】実施形態に係る半導体発光素子は、基板と、前記基板の第1の主面の側に設けられた第1の半導体層と、前記第1の半導体層の上に設けられた発光層と、前記発光層の上に設けられた第2の半導体層と、を備えている。そして、前記基板の第1の主面には、頂部に凹部を有する突起部が複数設けられている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因するクラック等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成されたGaN系化合物半導体積層構造3と、基板1とGaN系化合物半導体積層構造3との間に設けられたAlN系の応力緩和層2と、が設けられている。応力緩和層2のGaN系化合物半導体積層構造3と接する面に、深さが5nm以上の窪み2aが2×1010cm-2以上の個数密度で形成されている。

(もっと読む)

シリコン膜の形成方法およびその形成装置

【課題】ボイドやシームの発生を抑制することができるシリコン膜の形成方法およびその形成装置を提供する。

【解決手段】シリコン膜の形成方法は、第1成膜工程と、エッチング工程と、ドープ工程と第2成膜工程とを備えている。第1成膜工程では、被処理体の溝を埋め込むように不純物でドープされていないノンドープシリコン膜を成膜する。エッチング工程では、第1成膜工程で成膜されたノンドープシリコン膜をエッチングする。ドープ工程では、エッチング工程でエッチングされたノンドープシリコン膜を不純物でドープする。第2成膜工程では、ドープ工程でドープされたシリコン膜を埋め込むように、不純物がドープされたシリコン膜を成膜する。

(もっと読む)

ダイヤモンド基板

【課題】クラック等の欠陥がなく表面の平坦性に優れ、成長速度が速く低コスト化が可能な単結晶ダイヤモンド基板の製造方法及びそれにより得られる厚膜ダイヤモンド基板の提供を目的とする。

【解決手段】2°以上のオフ角を有する結晶構造{111}の母ダイヤモンド基板の上に化学気相成長法(CVD)を用いてラテラル成長が発現する条件下でダイヤモンドを成長させて得ることを特徴とする。

(もっと読む)

AlN層の製造方法およびAlN層

【課題】概ね1250℃未満が成長温度の限界である一般に市販されているMOCVD装置を用いて、低コストで品質の高い優れたAlN層を製造する。

【解決手段】AlN層の製造方法において、c面Al2O3基板をAlN成長に先んじてAlN成長を行う1000℃以上1200℃以下の成長温度にまで昇温する第1ステップと、第1ステップにより1000℃以上1200℃以下で加熱されているc面Al2O3基板上に、1000℃以上1200℃以下の成長温度でAlN層を成長する第2ステップと、第2ステップで形成したAlN層を、H2またはN2またはそれらが混入されたキャリアガス中、または該キャリアガスにNH3が混入されたプロセスガス中で1000℃以上1250℃未満の温度でアニールする第3ステップと、第3ステップでアニールされたAlN層上に1000℃以上1250℃未満の成長温度でAlN層を成長する第4ステップとを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18上に第1のGaN層20を形成する工程と、第1のGaN層20上に、InAlN電子供給層18および第1のGaN層20を形成した際の温度よりも高い温度で、第2のGaN層22を形成する工程と、InAlN電子供給層18上に、ゲート電極26と、ゲート電極26を挟むソース電極28およびドレイン電極30と、を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】高周波数動作が可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

窒化物半導体発光素子およびその製造方法

【課題】静電耐圧が高い窒化物半導体発光素子を歩留まりが高く製造する窒化物半導体発光素子の製造方法を提供する。

【解決手段】本発明の窒化物半導体発光素子は、成長用基板と、該成長用基板上に形成されたn型窒化物半導体層と、該n型窒化物半導体層上に形成された発光層と、該発光層上に形成されたp型窒化物半導体層とを有し、n型窒化物半導体層の発光層と接する側の表面から基板に向けて略垂直に延び、直径が2nm〜200nmであるパイプ穴を5000個/cm2以下有することを特徴とする。

(もっと読む)

半導体エピタキシャル基板、およびその製造方法

【課題】

高周波信号遮断後の回復が早く、素子分離特性のよい化合物半導体エピタキシャル基板を提供する。

【解決手段】

半導体エピタキシャル基板は、単結晶基板と、単結晶基板上にエピタキシャル成長されたAlN層と、AlN層の上にエピタキシャル成長された窒化物半導体層とを有し、単結晶基板とAlN層間界面より、AlN層と窒化物半導体層間界面の方が凹凸が大きい、ことを特徴とする。

(もっと読む)

半導体発光素子、窒化物半導体層、及び、窒化物半導体層の形成方法

【課題】低転位密度と良好な表面平坦性とを両立した、高効率な半導体発光素子、窒化物半導体層、及び、窒化物半導体層の形成方法を提供する。

【解決手段】実施形態によれば、下地層と、第1半導体層と、発光層と、第2半導体層と、を備えた半導体発光素子が提供される。発光層は下地層と第1半導体層との間に設けられる。第2半導体層は下地層と発光層との間に設けられる。下地層は、第2半導体層の側の第1主面と、第1主面とは反対側の第2主面と、を有する。下地層は、第2主面に設けられ、凹部と側部と凸部とを有する凹凸を有する。凸部に繋がる転位の少なくともいずれかは、側部に繋がる。凸部に繋がる転位のうちで第1主面に到達する転位の割合は、凹部に繋がる転位のうちで第1主面に到達する転位の割合よりも低い。第1主面のうちで凹部と重なる領域に繋がる転位は、凹部に繋がる転位よりも少ない。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つのエピタキシャル成長面を有する基板を提供する第一ステップと、前記基板のエピタキシャル成長面の上に複数の空隙を含むカーボンナノチューブ層を懸架するように配置する第二ステップと、前記基板のエピタキシャル成長面にエピタキシャル層を成長させて、前記カーボンナノチューブ層を包む第三ステップと、を含む。

(もっと読む)

材料層を堆積するための装置および方法

【課題】プロセスガスから発生する材料層を基板ウェハ上に堆積するための装置および方法を提供する。

【解決手段】プロセスガスから発生する材料層を基板ウェハ上に堆積するための装置は、上方ドームと下方ドームと側壁とによって画定されるリアクタチャンバと、材料層の堆積の際に基板ウェハを保持するためのサセプタと、サセプタを取囲む予熱リングと、ライナーとを備え、その上に、予熱リングが、均一幅の隙間が予熱リングとサセプタとの間に存在するように中央位置に支持され、さらにライナーと予熱リングとの間に作用するスペーサを備え、当該スペーサは、予熱リングを中央位置に保ち、かつ予熱リングとライナーとの間に距離Δを発生する。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つのエピタキシャル成長面を有する基板を提供する第一ステップと、前記基板のエピタキシャル成長面に複数の空隙を含むカーボンナノチューブ層を配置する第二ステップと、前記基板のエピタキシャル成長面に真性半導体エピタキシャル層を成長させる第三ステップと、前記真性半導体エピタキシャル層の上に、ドープされた半導体エピタキシャル層を成長させる第四ステップと、を含む。

(もっと読む)

窒化物半導体薄膜およびその成長方法

【課題】従来よりも原子レベルで平坦な表面を有する窒化物半導体薄膜及びその成長方法を提供する。

【解決手段】ミスカットを有するGaN基板101のステップフロー成長(工程1)により制限領域内に形成されたテラス202に、工程1よりもキャリアガスに含まれる水素の組成を少なくして、トリメチルガリウム(TMG)又はトリエチルガリウム(TEG)を供給し、テラス202の上にGaNの2次元核301を1個以上100個以下発生させる(工程2)。次に、工程2よりもキャリアガスに含まれる水素の組成を多くする(工程3)。これにより、複数の2次元核301が横方向成長して1分子層の厚さの連続的なGaN薄膜302となる。工程2と工程3を交互に繰り返すことにより、2分子層以上の厚さのGaN薄膜303を成長させる。

(もっと読む)

立方晶炭化珪素半導体基板の製造方法

【課題】結晶欠陥の少ない高品質な3C−SiC層を形成することが可能な立方晶炭化珪素半導体基板の製造方法を提供する。

【解決手段】シリコン基板11の上面11aに炭化層12を形成する第1の工程と、シリコン基板11の温度を第2の温度範囲の温度まで下降させる第2の工程と、シリコン基板11の温度が第2の温度範囲の温度となったところで、シリコン原料ガスを導入し、シリコン基板11と炭化層12の間の界面に形成された空孔11hにシリコンをエピタキシャル成長させて空孔11hを埋める第3の工程と、シリコン原料ガスの導入を止め、炭素原料ガスを導入しつつシリコン基板11の温度を第3の温度範囲の温度まで上昇させる第4の工程と、シリコン基板11の温度が第3の温度範囲の温度となったところで、シリコン原料ガス及び炭素原料ガスを導入し、炭化層12上に立方晶炭化珪素をエピタキシャル成長させる第5の工程と、を有する。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

1 - 20 / 221

[ Back to top ]