Fターム[5F045GB13]の内容

気相成長(金属層を除く) (114,827) | 測定・測定結果に基づく制御・制御一般 (1,937) | 成膜後の測定・測定結果に基づく制御 (226) | 膜厚を測定するもの (48)

Fターム[5F045GB13]に分類される特許

1 - 20 / 48

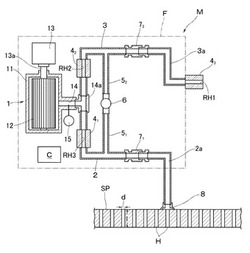

流量測定装置

【課題】高アスペクト比の細孔に対しても効率よくかつ精度よく当該細孔内を流れるガスの流量を測定することができる作業性のよい流量測定装置を提供する。

【解決手段】本発明の流量測定装置は、大気圧より低い所定圧力で吸引する吸引手段1と、この吸引手段に夫々接続される主吸気通路2、2a及び比較吸気通路3、3aとを備える。主吸気通路が細孔Hの一側に着脱自在に接続され、比較吸気通路が細孔に対応する第1の測定基準孔RH1に連通し、この比較吸気通路に細孔に対応する第2の測定基準孔RH2が介設されると共に主吸気通路に細孔に対応する第3の測定基準孔RH3が介在され、吸引手段を稼働して細孔及び第1の測定基準孔を通してガスを夫々吸引し、細孔及び第3の測定基準孔備の間、及び、第1及び第2の両測定基準孔の間における主吸気通路と比較吸気通路との圧力差を測定する測定手段15が設けられている。

(もっと読む)

熱フィラメントCVD装置及び成膜方法

【課題】熱フィラメントCVD法によって、有効成膜面積を大面積化することのできる熱フィラメントCVD装置及びその装置を用いた薄膜の形成方法を得る。

【解決手段】薄膜を形成するための熱フィラメントCVD装置であって、フィラメントを固定するための少なくとも一対のフィラメント固定部と、フィラメント固定部の間の距離を変えるためのフィラメント固定部移動機構と、フィラメントの伸縮状態の変化を検出するためのフィラメントの伸縮状態検出手段と、を含み、フィラメントの伸縮状態検出手段が、少なくとも一対のフィラメント固定部の間の略中央の検出位置において、フィラメントからの少なくとも一つの波長の電磁波の強度変化を測定するための、又はフィラメントからの電磁波の波長、強度若しくはそれらの組み合せを測定するための、電磁波測定機構を含む、熱フィラメントCVD装置である。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】シリコン基板上に形成される、低転位密度で結晶品質が優れた窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施形態によれば、下地層と、機能層と、を備えた窒化物半導体層が提供される。下地層は、シリコン基板の上に形成されたAl含有窒化物半導体層の上に形成され、不純物濃度が低く、GaNを含む。機能層は、下地層の上に設けられる。機能層は、下地層の不純物濃度よりも高い不純物濃度を有し第1導電形のGaNを含む第1半導体層を含む。Al含有窒化物半導体層は、多層構造体を含む。多層構造体は、Alを含む窒化物半導体を含む複数の第2層と、複数の第2層の間に設けられ第2層におけるAl組成比よりも低いAl組成比を有する窒化物半導体を含む第1層と、を含む。下地層の厚さは、第1層の厚さよりも厚く、第1半導体層の厚さよりも薄い。

(もっと読む)

気相成長装置及び気相成長方法、並びにエピタキシャルウェハ

【課題】膜厚分布の調整を容易、且つより均一な膜厚分布を実現できる気相成長装置を提供する。

【解決手段】反応炉11内に半導体原料ガスを供給し、反応炉11内の基板12上に化合物半導体膜を成長させる気相成長装置10において、反応炉11内に半導体原料ガスの供給口13を複数設け、複数の供給口13からそれぞれ半導体原料ガスを供給して反応炉11内の半導体原料ガス濃度を局所的に調整するものである。

(もっと読む)

半導体装置の製造方法、製造システムおよび調整装置

【課題】製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供すること。

【解決手段】実施形態にかかる半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

(もっと読む)

基板処理管理装置

【課題】基板の処理品質管理作業の負担を低減し、基板品質を継続して安定化させる。

【解決手段】基板処理装置及び測定器と通信回線を介して接続した自動品質管理装置によりレシピデータに基づいて基板処理を実行させ、測定器から得られた処理結果としての膜厚データに基づいて基板処理装置で処理される基板の品質を管理する。管理装置は、測定器から測定データを通信手段22で受信し、当該基板の処理を行ったレシピデータに対応付けてファイル42に蓄積する。複数の測定データからレシピデータと基板の膜厚との関係を回帰式決定手段31で算出し、入力手段51から入力した品質管理ルール及び目標値に基づき、統計解析手段32が受信した測定データが当該ルールから外れる場合には、当該目標値を用いて回帰式を逆算し、当該目標値を満たすレシピデータを算出し、このレシピデータを通信手段21からダウンロードして基板処理装置に処理を実行させる。

(もっと読む)

半導体素子用のエピタキシャル基板、および半導体素子用エピタキシャル基板の製造方法

【課題】高耐電圧性を有するとともにp型不純物の拡散による結晶品質の劣化が好適に抑制された、半導体素子用のエピタキシャル基板を提供する。

【解決手段】(111)方位の単結晶シリコンである下地基板1の上に、前記下地基板の基板面に対し(0001)結晶面が略平行となるようにIII族窒化物層群を形成してなる半導体素子用のエピタキシャル基板10が、組成の相異なる第1単位層31と第2単位層32とを繰り返し交互に積層してなる組成変調層3と、組成変調層の上に形成され、Alを含むIII族窒化物からなる中間層5と、を含む単位構造体を複数積層してなるバッファ層8と、バッファ層の直上に形成されたチャネル層9aと、チャネル層の上に形成されたバリア層9bと、を備え、バッファ層に含まれる複数の前記中間層のうちの少なくとも1つにp型不純物が意図的に導入されてなり、隣接層に第1の層から拡散したp型不純物が存在する、ようにする。

(もっと読む)

炭化珪素半導体素子の製造方法および炭化珪素層付ウェハ

【課題】炭化珪素ウェハの主面に平行な面内における素子特性のばらつきを抑えて、歩留まりを向上させる。

【解決手段】

本発明の炭化珪素半導体素子の製造方法は、(A)炭化珪素ウェハ101と、炭化珪素ウェハ101の主面上に配置され、第1導電型の不純物を含む複数の第1導電型不純物領域105を有する第1炭化珪素層110とを備えた炭化珪素層付ウェハ1を用意する工程と、(B)第1炭化珪素層110の表面に炭化珪素をエピタキシャル成長させることによって、第2炭化珪素層115を形成する工程とを包含し、工程(B)において、複数の第1導電型不純物領域105の表面における第1導電型の不純物の濃度分布に基づいて、炭化珪素ウェハ101の主面に平行な面内で、第2炭化珪素層115の厚さ、不純物濃度、またはその両方に分布をもたせるように、エピタキシャル成長させる条件を制御する。

(もっと読む)

基板処理装置

【課題】反応管内の異物汚染を抑制し、装置稼働率の低下を防止することができる基板処理装置を提供する。

【解決手段】複数の基板を積層して収容する石英製の反応管203と、前記反応管内に処理ガスを供給する処理ガス供給系と、前記反応管内にクリーニングガスを供給するクリーニングガス供給系と、前記反応管内の雰囲気を排気する排気系と、前記処理ガス供給系と前記クリーニングガス供給系と前記排気系とを制御する制御系と、を有し、前記反応管内に前記基板の積層方向に沿って延びる石英製の板状部材266aを設け、前記クリーニングガス供給後の前記反応管内に付着した膜の除去状態を確認する。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】製造装置の構造や稼働状態などに起因する加工ばらつきによる半導体装置の特性のばらつきを抑え、製造歩留りを向上させることが可能な半導体装置の製造方法と製造装置を提供する。

【解決手段】半導体装置の製造方法において、複数のウェハ処理する第1の処理装置において、第1の処理オーダーで、複数のウェハに第1の処理を行い、第1の処理における複数のウェハ毎の処理量を求め、第1の処理の後に、複数のウェハ処理する第2の処理装置における第2の処理による複数のウェハ毎の処理量を求め、第1の処理による複数のウェハ毎の処理量と第2の処理による複数のウェハ毎の処理量から第1の処理オーダーとは異なる第2の処理オーダーを決定し、第2の処理装置において、第2の処理オーダーで、複数のウェハに第2の処理を行う。

(もっと読む)

プラズマCVD成膜装置

【課題】真空チャンバ内で複数枚の基板を同時に成膜するプラズマCVD成膜装置において、基板配置部材上に配置される複数枚の基板について、基板品質を向上させる。

【解決手段】基板配置部材上に配置される複数枚の基板の2次元画像を取得し、この2次元画像を用いて、異なる波長の反射光強度によって各基板上の膜厚情報を取得し、この膜厚情報をフィードバックして成膜することによって、膜厚分布を均一化し、平均膜厚の再現性を良好なものとし、2次元画像の反射光強度の二次元分布によって基板上に付着するパーティクルによる基板上の配置位置情報を取得し、この配置位置情報をフィードバックして基板の配置位置を制御することによって、パーティクルによる不良基板の発生を低減する。

(もっと読む)

基板処理装置、その制御装置およびその制御方法

【課題】プロセス結果に悪影響を及ぼす処理ガス供給周期パターンを予め変更しておき、基板に対する適切な処理を行う。

【解決手段】設定値入力部41からの情報に基づいて、基板回転機構の回転周期、処理ガスの供給周期、処理ガスの供給時間及び処理ガスの供給回数を含む処理ガス供給周期パターン演算結果が、パターン演算部42において求められる。設定値入力部41からの情報に基づいて、基板上に供給される処理ガスの供給領域の形状がシミュレータ49によりシミュレーションされ、その結果がディスプレイ50に表示される。比較部43において、パターン演算部42からの処理ガス供給周期パターンの演算結果と、記憶部45からのプロセス結果に悪影響を与える処理ガス供給周期パターンの参照結果とが比較される。比較部43において、処理ガス供給周期パターンの演算結果と、プロセス結果に悪影響を与える参照結果が一致した場合、アラーム部44からアラームが発せられる。

(もっと読む)

半導体膜の改良された堆積方法

【課題】均一性の高いSi又はSiGeを基板表面上に堆積する方法を提供する。

【解決手段】化学気相成長プロセスにおいて、輸送量制限領域又はその近傍で、薄膜の堆積を行うことを可能にする化学前駆体を利用する。このプロセスによれば、堆積速度が大きく、さらに組成的にも厚み的にも、通常の化学前駆体を用いて調整した膜より均一な膜を生成することができる。好ましい実施の形態では、トリシランを使用して、トランジスタゲート電極などの様々な用途で半導体産業において有用なSi含有薄膜を堆積する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素半導体装置の製造方法において、アニール処理の際の珪素および炭素の蒸発を防止する保護膜の膜厚測定を精度良く、かつ、低コストで行うことが可能な製造方法を提供する。

【解決手段】基板保持具35にウエハWFを搭載して成膜炉32内に置き、成膜炉32内を真空ポンプによりガス排気部33を介して真空排気し、残存する酸素を極力除去した後、Arやヘリウム(He)などの不活性ガスをガス導入部31を介して導入しながら、減圧下で成膜炉32内の温度を800℃〜950℃の範囲に加熱する。この温度に達したら、不活性ガスの流入を停止し、成膜炉32内にソースガスとして気化したエタノールをガス導入部31を介して導入することで、ウエハWFの全表面にグラファイト膜を成膜する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】用いるシリコン単結晶基板の導電型や添加元素に関わらず、ミスフィット転位の発生を抑制したシリコンエピタキシャルウェーハおよびその製造方法を提供する。

【解決手段】少なくとも、シリコン単結晶基板2と、該シリコン単結晶基板2の主表面上に気相成長によって形成されたシリコン単結晶薄膜3とからなるシリコンエピタキシャルウェーハ1であって、前記シリコン単結晶基板2の格子歪み量εを((X線回析法で測定した前記シリコン単結晶基板2の格子定数―真性シリコンの格子定数)/真性シリコンの格子定数の絶対値)とし、前記シリコン単結晶薄膜3の厚さをtμmとした時、t<(5.0×10−4)×ε―1.1を満たすものであることを特徴とするシリコンエピタキシャルウェーハ。

(もっと読む)

エピタキシャル層の膜厚測定方法、エピタキシャルウェーハの製造方法およびエピタキシャルウェーハの製造工程管理方法

【課題】基板抵抗率によらず基板上にエピタキシャル層が形成され、エピタキシャル層形成後に研磨されたエピタキシャル層の厚さを測定することができる手段および上記手段により製品ウェーハのエピタキシャル層厚を保証したエピタキシャルウェーハを提供する。

【解決手段】半導体ウェーハをエピタキシャル成長工程に付すことにより、該半導体ウェーハの表面にエピタキシャル層を形成することを含むエピタキシャルウェーハの製造工程におけるエピタキシャル層の膜厚測定方法。エピタキシャル成長工程前に半導体ウェーハの厚みAを測定すること、エピタキシャル成長工程後に半導体ウェーハの表面に形成したエピタキシャル層を研磨すること、研磨後に得られたエピタキシャルウェーハの厚みBを測定すること、前記厚みBと厚みAとの差分(B−A)として、エピタキシャル層の厚みを算出することを含む。前記厚みAおよび厚みBを、非接触変位測定計により測定する。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】エピタキシャルシリコンウェーハの外周部の表面平坦性が高まるエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】シリコンウェーハの裏面デポジションのウェーハ周方向の平均値と、シリコンウェーハの外周部のSFQDのウェーハ周方向の平均値と、エピタキシャル膜のウェーハ周方向のロールオフの平均値とを合算した値が0となるように、エピタキシャル膜の成膜条件を決定し、エピタキシャル膜のロールオフを制御する。これにより、エピタキシャルシリコンウェーハの外周部の表面平坦性を高められる。その結果、平坦性適用領域が拡大し、デバイスの歩留まりが大きくなる。

(もっと読む)

製造制御装置及び製造制御方法

【課題】膜厚変動を抑制することにより、トランジスタ特性のばらつきを低減できる製造制御装置及び製造制御方法を提供する。

【解決手段】第1半導体ウェハ上に絶縁膜を堆積する成膜装置30を制御する制御パラメータ(堆積時間ttarget)を算出する製造制御装置20であって、第2半導体ウェハの第2ウェハ表面積L1が大きいほど、成膜装置30に絶縁膜を厚く堆積させる制御パラメータ(堆積時間ttarget)を算出する。また、製造制御装置20は、第2ウェハ表面積L1が大きいほど堆積時間ttargetが長くなるように堆積時間ttargetを算出する堆積時間算出部116を備えてもよい。

(もっと読む)

成膜反応装置及び成膜基板製造方法

【課題】基板の膜厚制御性能を向上させることのできる技術を提供する。

【解決手段】ガス流入口20Bの上流側で、ガス流の幅方向に独立してガス流量を制御可能な複数の部分制御範囲(LLゾーン、LRゾーン、Rゾーン)が構成されており、各部分制御範囲におけるガス流量を制御する制御装置66を備え、制御装置66は、ウェハ28を回転させつつ行われた回転成膜によりウェハ28上に形成された膜厚データに基づいて、ウェハ28上の種々の位置における膜成長速度と所定の目標膜成長速度との間の偏差を求め、部分制御範囲のそれぞれのガス流量の変化が、ウェハ28への回転成膜時において膜成長速度分布の変化に及ぼす感度を定義した回転時膜成長感度データ72を用いて、種々の位置における偏差を減らすように、部分制御範囲のそれぞれのガス流量を制御するように構成する。

(もっと読む)

半導体装置の製造装置および半導体装置の製造方法

【課題】効率的な製造工程を提供し、製造コストを低減することができる半導体装置の製造装置および半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造装置100は、ウェハカセット2,3,4と、ウェハの洗浄および表面改質を行う装置5と、ウェハの位置合わせを行う装置6と、ウェハ表面にパッシベーション膜となる材料を射出する装置7と、パッシベーション膜の外観検査を行う装置8と、パッシベーション膜に熱処理を行う装置9と、処理順にウェハを各装置に搬送する装置10を備えている。製造装置100では、インクジェット技術を用いて、洗浄後のウェハ表面に、選択的にパッシベーション膜のパターンを形成する。次いで、パッシベーション膜のパターンが、所望のパターン条件を有しているか否かを検査する。パッシベーション膜が所望のパターンで形成されている場合に、パッシベーション膜を硬化および焼成する熱処理を行う。

(もっと読む)

1 - 20 / 48

[ Back to top ]