Fターム[5F045HA03]の内容

気相成長(金属層を除く) (114,827) | 他プロセスとの組合せ (2,158) | 前処理(膜形成が後) (762) | エッチング (407) | ドライエッチ (245)

Fターム[5F045HA03]に分類される特許

1 - 20 / 245

加熱装置及びこれを用いた半導体気相成長装置

半導体ウェーハの製造方法及び半導体製造装置

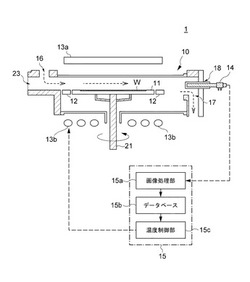

【課題】ウェーハ搬入時にウェーハのエッジが反って非接触搬送部材と接触し、スクラッチ傷が発生することを防止する。

【解決手段】反応炉10のカメラ取り付け穴18にカメラ14を取り付け、反応炉10内のウェーハを撮影可能な状態とする。次に、予め所定のウェーハ投入温度に設定された反応炉10内にウェーハWを搬入し、サセプタ11上に載置する。このとき、ウェーハWのエッジが一時的に反り上がるので、この状態をカメラ14で撮影する。そして撮影した画像からウェーハWの反り量を求め、さらにこの反り量に基づいて非接触搬送部材と接触することがない反り量となる適正なウェーハ投入温度を求める。その後、ウェーハWと同一品種を処理する場合に、反応炉10内をこの適正なウェーハ投入温度に設定する。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法

【課題】エピタキシャル成長の際の裏面クモリ及びピンハローを抑制して、高品質なシリコンエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】チャンバー内に配設されたサセプタのウェーハ載置面上にシリコン単結晶基板を載置して、該シリコン単結晶基板上にエピタキシャル成長させることによりシリコンエピタキシャルウェーハを製造する方法であって、前記シリコン単結晶基板を載置する前に、前記チャンバー内にシリコン原料ガスを流入させながら、50秒を超えて300秒以下の時間で、前記サセプタのウェーハ載置面上にポリシリコン膜を被覆し、その後前記サセプタのウェーハ載置面上に前記シリコン単結晶基板を載置してエピタキシャル成長させるシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

基板の製造方法

【課題】基板の製造方法の提供。

【解決手段】下地基板を反応炉内に搬入するステップと、下地基板の上にバッファー層を形成するステップと、バッファー層の上にセパレータ層を形成するステップと、セパレータ層の上に少なくとも二つの温度で半導体層を形成するステップと、下地基板を反応炉から搬出して自然冷却によってセパレータ層を中心に下地基板と半導体層を分離するステップとを含む基板の製造方法。

(もっと読む)

窒化物半導体成長用基板及びその製造方法、窒化物半導体エピタキシャル基板、並びに窒化物半導体素子

【課題】低転位密度の窒化物半導体を成長することが可能な窒化物半導体成長用基板及びその製造方法、並びに窒化物半導体成長用基板を用いて作製される窒化物半導体エピタキシャル基板及び窒化物半導体素子を提供する。

【解決手段】サファイア基板のC面である主面に、前記主面に対して90°未満で傾斜した側面を有する錐状または錐台状の凸部が格子状に配置して形成されており、前記主面からの前記凸部の高さが0.5μm以上3μm以下で、隣接する前記凸部間の距離が1μm

以上6μm以下であって、前記凸部の前記側面の表面粗さRMSが10nm以下である窒化物半導体成長用基板である。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaNを用いた縦型の電界効果トランジスタにおいて、素子の作製にコストの上昇を招くことなく、ドレイン電流密度を大きくできるようにする。

【解決手段】GaNからなるチャネル層101と、GaNより大きなバンドギャップエネルギーを有してアルミニウムを含む窒化物半導体から構成されてチャネル層101の一方の面に形成された障壁層102を備える。ここで、チャネル層101の一方の面は、N極性面とされ、他方の面はIII族極性面とされていればよい。また、チャネル層101の他方の面に形成されたドレイン電極103と、ドレイン電極103に対向して障壁層102の上に形成されたゲート電極104と、ゲート電極104と離間して障壁層102の上に形成されたソース電極105とを備える。

(もっと読む)

半導体装置の製造方法

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】GaNを用いた窒化物半導体装置において、電流が流れる経路に、再結晶成長などによる界面が存在することがない状態で、十分な耐圧が得られるようにする。

【解決手段】GaNからなるチャネル層(第2半導体層)101と、チャネル層101の一方の面であるN極性面に形成された第1障壁層(第1半導体層)102と、チャネル層101の他方の面であるIII族極性面に形成された第2障壁層(第3半導体層)103とを備える。第1障壁層102および第2障壁層103は、例えば、AlGaNから構成されている。また、ドレイン電極(第1電極)104が、第1障壁層102の上に形成され、ゲート電極105が、ドレイン電極104に対向して第2障壁層103の上に形成されている。ソース電極(第2電極)106は、ゲート電極105と離間して第2障壁層103の上に形成されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

エピタキシャルウェーハの製造方法及びエピタキシャルウェーハ

【課題】より急峻且つより安定したSRプロファイルを有するエピタキシャルウェーハを製造することのできる技術を提供する。

【解決手段】不純物を含有するシリコン単結晶の基板Sの直上に、基板Sよりも不純物濃度が低い第1層を気相成長させる第1成長工程(1st Growth工程)と、第1層よりも上に第2層を気相成長させる第2成長工程(2nd Growth工程)とを有するエピタキシャルウェーハの製造方法であって、第1成長工程において、強制的に排気を行って常圧AP以下の第1圧力RPの下で気相成長させ、第2成長工程において、第1圧力RPより高い第2圧力APの下で気相成長させるようにする。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

窒化物半導体基板及びその製造方法、並びにそれを用いた窒化物半導体発光素子

【課題】動作特性に優れた窒化物半導体発光素子を容易に得られる窒化物半導体基板を実現できるようにする。

【解決手段】窒化物半導体基板101は、基板110の主面上に形成された複数の成長阻害領域となるマスク膜120と、基板の主面におけるマスク膜から露出する領域の上に形成された複数の第1の窒化物半導体層111と、各第1の窒化物半導体層111の側面上にのみ成長により形成された複数の第2の窒化物半導体層112と、複数の第1の窒化物半導体層111及び複数の第2の窒化物半導体層112を覆うように成長により形成された第3の窒化物半導体層113とを有している。複数の第2の窒化物半導体層は、成長阻害領域の上において互いに隣り合う半導体層同士が接合しておらず、第3の窒化物半導体層は、第2の窒化物半導体層同士が互いに隣り合う領域において接合している。

(もっと読む)

半導体基板の製造方法

【課題】シリコンウェハ等のベース基板上方に窒化物半導体からなる半導体結晶層を形成する場合に、当該半導体結晶層の転位密度を低減する。

【解決手段】ベース基板をエピタキシャル結晶成長装置の成長室に設置した後、ベース基板の上に、接着層、バッファ層および活性層をエピタキシャル成長法により順次形成する層形成工程を有し、接着層形成工程が、第1結晶層を形成する工程と第2結晶層を形成する工程と、を有し、第1結晶層の形成後であって第2結晶層の形成前の第1の段階、および、第2結晶層の形成後であってバッファ層の形成前の第2の段階、からなる群から選択された少なくとも1つの段階において、3族原料ガスの供給を停止するとともに成長室の内部を、アンモニアを含むガスの雰囲気に一定時間だけ維持する雰囲気維持工程を有する半導体基板の製造方法を提供する。

(もっと読む)

エピタキシャル膜形成のためのクラスターツール

【課題】選択的エピタキシープロセス及びAGSプロセスの両者に対して、効率的に実施するための装置を提供する。

【解決手段】エピタキシャル膜を形成する方法において、エピタキシャル膜を形成する前に、第1のガスを使用して第1の処理チャンバー108内で基板を前クリーニングするステップと、上記第1の処理チャンバーから真空下で移送チャンバー102を通して第2の処理チャンバー110へ基板を移送するステップと、上記第1のガスを使用せずに上記第2の処理チャンバー110内で基板上にエピタキシャル層を形成するステップと、上記第1のガスは上記第2の処理チャンバー内で使用するには不適当である、を備えた方法。

(もっと読む)

ダイヤモンド複合体

【課題】単結晶ダイヤモンドと多結晶ダイヤモンドの双方の利点を活かしながら、更に板状の構造を可能にするために、多結晶ダイヤモンドの研磨の困難性も回避し、研磨が容易なダイヤモンド複合体を提供すること。

【解決手段】少なくとも2種類の結晶性の異なる結晶からなる構造の複合体であり、その内の第一の結晶は高圧合成法により合成した単結晶ダイヤモンドか、あるいは気相合成法により合成した単結晶ダイヤモンドであり、第二の結晶は欠陥を面内に周期的なパターン形状で含む気相合成法により合成したダイヤモンドであり、該第一の結晶及び第二の結晶はいずれも、主面が平行になるように層状に形成されていることを特徴とするダイヤモンド複合体。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】(0001)面に対して4°以下のオフ角θ1で傾斜したSi面が主面4とされたSiC基板2と、SiC基板2の主面4に形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、SiC基板2の主面4のオフ方向Dを、[11−20]軸方向および[01−10]軸方向に対して15°+/−10°の角度θ2で傾斜した方向にする。

(もっと読む)

シリコン膜の形成方法およびその形成装置

【課題】ボイドやシームの発生を抑制することができるシリコン膜の形成方法およびその形成装置を提供する。

【解決手段】シリコン膜の形成方法は、第1成膜工程と、エッチング工程と、ドープ工程と第2成膜工程とを備えている。第1成膜工程では、被処理体の溝を埋め込むように不純物でドープされていないノンドープシリコン膜を成膜する。エッチング工程では、第1成膜工程で成膜されたノンドープシリコン膜をエッチングする。ドープ工程では、エッチング工程でエッチングされたノンドープシリコン膜を不純物でドープする。第2成膜工程では、ドープ工程でドープされたシリコン膜を埋め込むように、不純物がドープされたシリコン膜を成膜する。

(もっと読む)

1 - 20 / 245

[ Back to top ]