Fターム[5F045HA15]の内容

気相成長(金属層を除く) (114,827) | 他プロセスとの組合せ (2,158) | 後処理(膜形成が先) (953) | イオン注入 (42)

Fターム[5F045HA15]に分類される特許

1 - 20 / 42

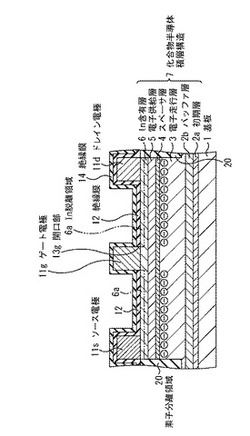

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

SiCバイポーラ型半導体素子

【課題】キャリア捕獲中心の少ないSiC半導体素子を提供する。

【解決手段】n型またはp型のSiC基板11と、n型またはp型の少なくとも1つのSiCエピタキシャル層12、あるいはn型またはp型の少なくとも1つのイオン注入層14と、を有し、pn接合界面付近および伝導度変調層(ベース層)内を除いた、SiC基板表面付近、SiC基板とSiCエピタキシャル層との界面付近、およびSiCエピタキシャル層の表面付近のうち少なくとも1つの領域100に、炭素注入層、珪素注入層、水素注入層、またはヘリウム注入層を有し、かつ、炭素原子、珪素原子、水素原子、またはヘリウム原子をイオン注入することで導入した格子間炭素原子をアニーリングにより伝導度変調層内へ拡散させるとともに格子間炭素原子と点欠陥とを結合させることで、電気的に活性な点欠陥が低減された領域を伝導度変調層内に有するSiCバイポーラ型半導体素子。

(もっと読む)

半導体装置およびその製造方法

【課題】大きなチャネル移動度を有する半導体装置及びその製造方法を提供する。

【解決手段】基板は、ポリタイプ4Hの六方晶の単結晶構造を有する半導体からなる表面SRを有する。基板の表面SRは、面方位(0−33−8)を有する第1の面S1と、第1の面S1につながりかつ第1の面S1の面方位と異なる面方位を有する第2の面S2とが交互に設けられることによって構成されている。ゲート絶縁膜は基板の表面SR上に設けられている。ゲート電極はゲート絶縁膜上に設けられている。

(もっと読む)

半導体装置

【課題】窒化物半導体を用いた半導体装置のオン抵抗を低減できるようにする。

【解決手段】半導体装置は、アンドープのAlGaN層104と、該AlGaN層104の上に形成され、AlGaN層104とオーミック接触するソース電極107及びドレイン電極108とを有している。AlGaN層104の上部における少なくとも各電極107、108と接触する部分には、不純物拡散層110が形成されている。不純物拡散層110は、AlGaN層104に対しアクセプタ性を示す不純物が拡散し、且つ、AlGaN層104における窒素空孔と不純物とが結合してなる不純物準位が、AlGaN層104の伝導帯端の近傍に形成される。

(もっと読む)

ナノ結晶を有する半導体デバイスを形成する方法

【課題】

ナノ結晶を有する半導体デバイスを形成する方法を提供する。

【解決手段】

ナノ結晶を有する半導体デバイス10を形成する方法は、基板12を設けるステップと、基板の表面の上方に第1絶縁層14を形成するステップと、第1絶縁層上に第1の複数のナノ結晶26(21、22)を形成するステップと、第1の複数のナノ結晶上に第2絶縁層28を形成するステップと、第2絶縁層に第1材料を注入するステップと、第1材料をアニールして第2絶縁層内に第2の複数のナノ結晶34(36、37)を形成するステップとを含む。この方法は、より高いナノ結晶密度を有する不揮発性メモリの電荷格納層を提供するために使用され得る。

(もっと読む)

半導体装置の製造方法、製造システムおよび調整装置

【課題】製品の歩留まりを向上させることができる半導体装置の製造方法、製造システムおよび調整装置を提供すること。

【解決手段】実施形態にかかる半導体装置の製造方法は、成膜工程と、加工工程と、イオン注入工程と、アニール工程と、調整工程とを含む。成膜工程では、基板上に半導体の薄膜を成膜する。加工工程では、薄膜を所定の形状に加工する。イオン注入工程では、所定の形状に加工された薄膜に対してイオン注入処理を行う。アニール工程では、イオン注入処理が行われた薄膜をアニール処理して抵抗素子を生成する。調整工程では、成膜工程における薄膜の成膜条件および成膜結果と加工工程における薄膜の加工結果とのうち、少なくともいずれか1つに基づき、イオン注入工程におけるイオン注入処理の処理条件およびアニール工程におけるアニール処理の処理条件の双方または一方を調整する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いゲート絶縁膜を備えたSiC半導体装置を提供する。

【解決手段】8度以下のオフ角度を有する炭化珪素基板(1)と、この基板上に形成された第1導電型の第1炭化珪素領域(2)と、この領域の表面に形成された第2導電型の第2炭化珪素領域(3)と、この領域の表面に形成され、不純物濃度が第2の炭化珪素領域と同程度に調整された第1導電型の第3炭化珪素領域(4)と、この領域の表面に選択的に形成された第1導電型の第4炭化珪素領域(5)と、第2炭化珪素領域の表面に形成された第2導電型の第5炭化珪素領域(6)と、第1炭化珪素領域から第3炭化珪素領域の少なくとも端部までを覆うように形成されたゲート絶縁膜(7)と、この上に形成されたゲート電極(8)とを具備し、第3炭化珪素領域の表面における、第3と第4炭化珪素領域の境界面は、オフ角度方向と90°以外の角度で交差するように形成されている。

(もっと読む)

シリコンエピタキシャルウェーハおよびシリコンエピタキシャルウェーハの製造方法

【課題】ゲッタリング能力が高く、かつシリコンエピタキシャル層の最表面部の酸素濃度が極めて低いシリコンエピタキシャルウェーハを提供する。

【解決手段】酸素濃度が7ppma(JEIDA)以上のシリコン単結晶基板の主表面上にエピタキシャル層が形成されたシリコンエピタキシャルウェーハであって、該シリコンエピタキシャルウェーハは2層以上の炭素イオン注入層を有し、かつ前記シリコンエピタキシャル層の最表面部は酸素濃度が5ppma(JEIDA)以下であることを特徴とするシリコンエピタキシャルウェーハ。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】 表面に金属膜が形成された基板を処理容器内に搬入する工程と、処理容器内に原料ガスと酸化源とを供給し排気することで、基板の表面に形成された金属膜上に所定膜厚の金属酸化膜を形成する処理を行う工程と、処理済基板を処理容器内から搬出する工程と、を有し、処理を行う工程では、酸化源としてオゾンガス、酸素ガスまたはプラズマにより活性化された酸素ガスを用い、所定膜厚の金属酸化膜を形成する過程において形成される金属酸化膜越しに、酸化源に含まれる酸素原子を、金属膜の表面に導入することで、金属膜の表面を酸化して導電性の金属酸化層に改質する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

III族窒化物半導体本体のインシチュドーパント注入及び成長

【課題】半導体材料の構造的及び化学量論的特性を保ったまま、窒化物本体を横方向及び縦方向で空間的に規定された選択ドーピングを達成しうるインシチュドーパント注入及び成長を提供する。

【解決手段】窒化物半導体本体の成長中にインシチュドーパント注入を可能にする方法は、ドーパント注入装置及び成長室を有する複合窒化物室中に、窒化物半導体本体に対する成長環境を確立するステップと、成長室内で窒化物半導体本体を成長させる成長ステップと、ドーパント注入装置を用いて成長室内で窒化物半導体本体にインシチュ状態でドーパント注入を行う注入ステップとを具える。この方法を用いて形成する半導体デバイスは、サポート基板上に形成した第1導電型の窒化物半導体本体と、窒化物半導体本体の成長中にこの窒化物半導体本体のインシチュドーパント注入により形成され、第2導電型を有する少なくとも1つのドープ領域とを具える。

(もっと読む)

半導体素子、および半導体素子の製造方法

【課題】高移動度と高耐圧を両立し、かつ大電流動作が可能なIII族窒化物半導体を用い

た半導体素子を提供する。

【解決手段】半導体素子は、III族窒化物系化合物半導体からなり、シートキャリア密度

が、1×1012cm−2以上5×1013cm−2以下である半導体動作層と、前記半

導体動作層上に形成された第1の電極及び第2の電極とを備え、前記半導体動作層におけ

る転位密度が1×108cm−2以上、5×108cm−2以下であることを特徴とする

。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】イオン注入したダイヤモンドの高温高圧アニールにより起こるダイヤモンド表面のエッチングを防ぎ、従来の方法では得られない高品質P型、N型ダイヤモンド半導体を得るダイヤモンド半導体の作製方法を提供すること。

【解決手段】ダイヤモンド基板5−11を用意し、そのダイヤモンド基板5−11上にマイクロ波プラズマCVD装置を用い、メタンを反応ガスとして基板温度700℃でダイヤモンド薄膜5−12を1μm積層する。上記ダイヤモンド薄膜5−12にイオン注入装置を用い、加速電圧60kV、ドーズ量1×1014cm−2でドーパントを打ち込む。その後、イオン注入ダイヤモンド薄膜5−13上に保護層(白金)5−14を形成する。表面に保護層5−14が形成されたイオン注入ダイヤモンド薄膜5−13を、超高温高圧焼成炉内に配置し、3.5GPa以上、600℃以上の圧力、温度下でアニールする。

(もっと読む)

パワー系半導体装置

【課題】パワーMOSFET等のドリフト領域等に関して、スーパジャンクション構造を導入する方法として、トレンチフィル方式におけるPカラム領域埋め込み用トレンチの埋め込みエピタキシプロセスを種々検討したところ、エピタキシャル成長時の高熱長時間処理により、埋め込みエピタキシャル層外へ拡散してしまうという問題があることが明らかとなった。

【解決手段】本願発明は、N型カラムとP型カラムが交互に繰り返されるスーパジャンクション構造を有するシリコン系パワー半導体装置において、前記P型カラムには、ボロン拡散抑制効果を有する元素が添加されている。

(もっと読む)

複合基板を形成し当該複合基板にIII−V発光装置を成長させる方法

本発明の実施例に従う方法は、ホスト基板部、及び、ホスト基板部へ接合されるシード層、を含む基板を提供するステップを含む。シード層は複数の領域を有する。n型領域及びp型領域との間に配置される発光層を含む半導体構造は基板において成長させられる。シード層に成長させられる半導体構造の上部表面は、複数のシード層領域のそれぞれよりも大きい横方向の拡がりの度合いを有する。  (もっと読む)

(もっと読む)

多段エピタキシャル方式による超接合半導体装置の製造方法

【課題】アライメントマーカーの形成後に行うシリコンエピタキシャルの成長速度を、通常の条件より遅くすることなく、アライメントマーカーのパターン形状精度の低下を防ぎ、超接合半導体装置を低オン抵抗にするために用いられる低抵抗砒素ドープシリコン基板からのオートドーピングを防止する多段エピタキシャル方式による超接合半導体装置の製造方法を提供すること。

【解決手段】低抵抗砒素ドープシリコン基板に多段エピタキシャル方式によるエピタキシャル成長とイオン注入を繰り返し実施する際にパターニングに用いられるアライメントマーカーを、前記エピタキシャル成長面とは反対側の裏面に設けた酸化膜の膜厚を選択的に減厚して形成した段差からなる凸部又は凹部として形成する。

(もっと読む)

半導体基板の製造方法

【課題】SiCを用いた半導体装置を効率よく製造するための半導体基板の製造方法を提供する。

【解決手段】第1の裏面B1を有する第1の炭化珪素基板11と、第2の裏面B2を有する第2の炭化珪素基板12とが準備される。第1および第2の裏面B1、B2の各々が一の方向に露出するように第1および第2の炭化珪素基板11、12が配置される。炭化珪素からなり、かつ第1および第2の裏面B1、B2を互いにつなぐ成長層30が化学気相成長法によって形成される。

(もっと読む)

半導体デバイス形成方法

基板ウェーハの裏側及び縁部断面をシールするためのシステム及び方法である。第1の方法の実施例によれば、第1導電型のシリコンウェーハにアクセスする。第1導電型のエピタキシャル層をシリコンウェーハの前面上で成長する。エピタキシャル層をインプラントし、逆の導電型の領域を形成する。成長及びインプラントを繰り返し、逆の導電型の垂直カラムを形成する。ウェーハに更にインプラントを行い、垂直カラムと垂直方向で整合した逆の導電型の領域を形成する。  (もっと読む)

(もっと読む)

圧力制御機器、圧力制御方法および基板処理装置

【課題】複数の処理工程(プロセス)を連続して行う基板処理装置において、チャンバー内の処理ガス流量や処理ガス圧力の大幅な変動に対して短時間で連続的に応答可能な圧力制御を行う圧力制御機器、圧力制御方法および該圧力制御機器を備える基板処理装置を提供する。

【解決手段】処理ガスが供給される減圧状態の処理室で複数の処理工程を行う基板処理装置であって、処理室に処理ガスを供給する処理ガス供給機構と、処理室の内部を排気する排気機構と、排気機構の排気量を調節する排気バルブと、複数の処理工程それぞれに最適な処理ガス圧力を算出するための演算テーブルを複数有し、演算テーブルに基づいて排気バルブの開度を制御する演算制御機構と、を備える基板処理装置が提供される。

(もっと読む)

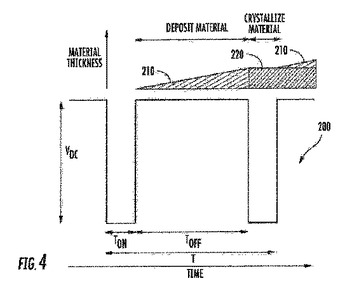

パルス堆積及び再結晶、並びに、結晶化/アモルファス材料を利用したタンデム太陽電池構造

基板上に材料を堆積及び結晶化する方法が開示され、特定の実施態様において、その方法は、堆積され、吹きつけられる種及びエネルギー輸送種を有するプラズマの生成を含んでもよい。第一の期間の間、基板にバイアス電圧は印加されず、プラズマ堆積を通じて種が基板上に堆積する。第二の期間の間、基板に電圧が印加され、堆積した種に向かって及び内部にイオンが引き付けられ、それにより堆積した層が結晶化する。このプロセスを十分な厚みが得られるまで繰り返すことができ、他の実施態様では、バイアス電圧又はバイアスパルス継続時間を変更して、生ずる結晶化の量を変えることができる。他の実施態様において、ドーパントを用いて、堆積した層をドープしてもよい。  (もっと読む)

(もっと読む)

1 - 20 / 42

[ Back to top ]