Fターム[5F048BA15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 素子形成領域、能動領域がSi以外の材料 (1,343) | III−V族半導体 (338)

Fターム[5F048BA15]に分類される特許

161 - 180 / 338

半導体装置の製造方法および半導体装置

【課題】電極の接触抵抗の低減によって高性能化した半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体基板上に第1の金属を堆積する工程と、第1の熱処理により第1の金属と半導体基板を反応させて、前記ゲート電極両側の前記半導体基板表面に金属半導体化合物層を形成する工程と、金属半導体化合物層中に、Siの原子量以上の質量を有するイオンをイオン注入する工程と、金属半導体化合物層上に第2の金属を堆積する工程と、第2の熱処理により、第2の金属を金属半導体化合物層中に拡散させることで、金属半導体化合物層と半導体基板の界面に、第2の金属を偏析させて界面層を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

MOSFETデバイスおよびその製造方法

【課題】フェルミレベルのピンニングの効果が、ポリシリコン(Poly−Si)/金属酸化物の界面で高い閾値電圧を招かないMOSFET(金属酸化物半導体電界効果トランジスタ)を含む半導体デバイスの製造方法を提供する。

【解決手段】半導体デバイスは、第1MOSFETトランジスタを含む。トランジスタは、基板、基板上の第1high−k誘電体層1、第1high−k誘電体層1上の第1誘電体キャップ層2、および第1誘電体キャップ層2上の、第1ドーピングレベルで第1導電型の半導体材料3からなる第1ゲート電極とを含む。第1誘電体キャップ層2は、スカンジウムを含む。

(もっと読む)

半導体装置の作製方法

【課題】必要とされる機能に応じてトランジスタの電気特性を制御し、半導体装置の高性能化、低消費電力化を図ることを目的の一とする。また、そのような半導体装置を、作製工程を複雑化することなく、高い歩留まりで生産性よく作製することを目的の一とする。

【解決手段】半導体装置に含まれるトランジスタのしきい値電圧を制御するための一導電型を付与する不純物元素の添加を、第1の半導体ウエハーよりトランジスタのチャネル形成領域として用いる単結晶半導体層を分離し、第2の半導体ウエハー上に転載する前に、第1の半導体ウエハーへ行う。

(もっと読む)

半導体装置

【課題】チャネル領域における高いキャリア移動度を有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成され、内部におけるキャリアの移動度がSi結晶よりも大きい第1の結晶からなる半導体層と、前記半導体層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層を挟んで形成され、前記半導体層に前記半導体層内のキャリアの移動度が上昇する方向に歪みを与える第2の結晶を含み、前記半導体層に接する深さの浅い領域であるソース・ドレインエクステンション領域を有するソース・ドレイン領域と、を有する。

(もっと読む)

CMOS素子及びその製造方法

【課題】CMOS素子及びその製造方法を提供する。

【解決手段】基板上に形成されたエピ層と、エピ層のそれぞれ異なる領域上に形成された第1及び第2半導体層と、第1及び第2半導体層上にそれぞれ形成されたPMOS及びNMOSトランジスタと、を備えるCMOS素子である。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極同士の間隔を短縮することができる半導体装置及びその製造方法を得る。

【解決手段】半導体基板13の表面にリセス溝14が形成されている。リセス溝14の底部に絶縁膜15が形成されている。絶縁膜15を覆うようにゲート電極16が形成されている。ゲート電極16は、絶縁膜15を挟んで両側においてリセス溝14の底部に接する。絶縁膜15を挟んで両側にデュアルゲートが自己整合的に形成されるため、ゲート電極同士の間隔を短縮することができる。

(もっと読む)

半導体装置

【課題】同一半導体基板に集積したMOSFETとショットキーダイオードのチップサイズを従来のものより大きくすることなく、高耐圧でしかも安価に作製できる半導体装置を提供すること。

【解決手段】MOSFETにショットキー接合を内蔵させるときに、ショットキー接合はMOSFETのpボディ領域6とゲート電極10と隔てられた場所に配置し、ショットキー接合の端部をp型の浅い接合によって囲まれるようにする。さらに、ショットキー接合の端部にある浅いp型接合20と、MOSFETのpボディ領域6との間がMOSゲートによって接続され、ゲートに負のバイアスが印加されると、MOSFETのpボディ領域6とショットキー接合の端部のp型領域20とが導電接続されるようにする。また、MOSFETのpボディ領域6内でソース領域と直接のコンタクトせず、前記ショットキー接合の端部のp型領域にMOSFETを介して電気的に接続される構造を有する。

(もっと読む)

窒化物系化合物半導体装置

【課題】リーク電流の増大、及び電流コラプス現象によるオン抵抗の増大を抑制できる窒化物系化合物半導体装置を提供する。

【解決手段】窒化物系化合物半導体からなるキャリア走行層3を有する半導体層10と、半導体層10の主面100上に配置され、キャリア走行層3を流れる主電流の電流経路の端部である第1の主電極21及び第2の主電極22と、第1の主電極21及び第2の主電極22を囲むように主面100上に配置され、主面100直下及びその近傍の半導体層10内の電荷を制御する外周電極30とを備える。

(もっと読む)

ED型インバータ回路および集積回路素子

【課題】特性の制御性および高温下での信頼性が高いED型インバータ回路および集積回路素子を提供すること。

【解決手段】基板上に形成された窒化物系化合物半導体からなる第1半導体層と、第1半導体層上に形成されるとともに、所定の位置に開口部を有し、第1半導体層よりもバンドギャップが大きい窒化物系化合物半導体からなる第2半導体層と、第2半導体層の開口部内に露出した第1半導体層の表面に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された第1ゲート電極と、第2半導体層上の第1ゲート電極を挟む位置に形成され、第2半導体層とオーミック接触する第1ソース電極および第1ドレイン電極と、第2半導体層上に形成され、第2半導体層とショットキー接触する第2ゲート電極と、第2半導体層上の第2ゲート電極を挟む位置に形成され、第2半導体層とオーミック接触する第2ソース電極および第2ドレイン電極と、を備える。

(もっと読む)

異なる高さの隣接シリコンフィンを製造する方法

異なる高さの隣接シリコンフィンを製造する方法は、上に分離層が堆積されたシリコン基板を供給し、分離層をパターニングして第1及び第2の分離構造を形成し、シリコン基板をパターニングして第1の分離構造の下の第1のシリコンフィンと第2の分離構造の下の第2のシリコンフィンとを形成し、基板上に絶縁層を堆積し、絶縁層を平坦化して第1及び第2の分離構造の頂面を露出させ、マスク層を堆積し且つパターニングして第2の分離構造をマスクせずに第1の分離構造をマスクし、ウェットエッチングを適用して第2の分離構造を除去し且つ第2のシリコンフィンを露出させ、第2のシリコンフィン上にシリコン層をエピタキシャル成長させ、そして、絶縁層を後退させて第1のシリコンフィンの少なくとも一部と第2のシリコンフィンの少なくとも一部とを露出させることを有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】保護ダイオードの熱抵抗を低減し、保護ダイオードの自己発熱を抑制することにより電流伝導度を増大させ、保護機能を向上させた半導体装置を提供する。

【解決手段】半導体基板と、前記半導体基板上に設けられた被保護素子と、前記半導体基板上に設けられた膜厚が30ナノメータ未満の酸化シリコンからなる絶縁膜と、前記絶縁膜の上に設けられ前記被保護素子と接続された保護ダイオードと、を備えたことを特徴とする半導体装置が提供される。または、半導体基板と、前記半導体基板上に設けられた被保護素子と、前記半導体基板上に設けられ、酸化シリコンよりも熱伝導率の高い材料からなる絶縁膜と、前記絶縁膜の上に設けられ前記被保護素子と接続された保護ダイオードと、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

デュアル仕事関数半導体デバイス

【課題】CMOSがFUSIゲートを含む場合、異なるシリサイド相を有する第1および第2の制御電極が形成され、ゲート形成後の熱工程等により各ゲートの異なったシリサイド相中のNi等の金属はゲート電極間を拡散しない半導体装置を提供する。

【解決手段】第1の制御電極17の金属半導体化合物から、第2の制御電極18の金属半導体化合物に、金属が拡散するのを防止するブロック領域23を形成する。ブロック領域23は、第1および第2の制御電極17、18の間の境界面に形成され、金属半導体化合物がそれから形成される金属中での溶解度より、金属半導体化合物中での溶解度が低いドーパント元素を注入することにより形成する。これにより、金属拡散が防止され、第1および第2の制御電極17、18の金属半導体化合物の構成が、例えば更なるデバイスの処理中の熱工程中に、実質的に変化せずに保たれる。

(もっと読む)

半導体装置

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファスシリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のトランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このようにして、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少しだけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

半導体装置の製造方法

【課題】ナノワイヤーのオープンにより生じるトランジスタの不良やリークにより生じる不良を低減させることのできる半導体装置を実現する。

【解決手段】基板10上の半導体素子の形成領域において、Siナノワイヤー13の配置不良があった箇所には、配置不良となっているSiナノワイヤー12を基板10上からアーム20を用いて除去し、新たなSiナノワイヤー13をアーム20を用いて再配置する。

(もっと読む)

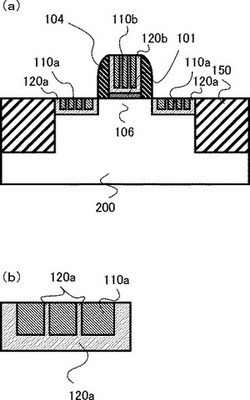

III−V族CMOSデバイスでのダマシンコンタクト

本発明は、第1および第2メインコンタクト(7)、例えば、ソースおよびドレインコンタクトと、制御コンタクト、例えば、ゲートコンタクト(10a)とを備えたIII−V族CMOSデバイスの製造方法に関する。該方法は、ダマシンプロセスを用いて制御コンタクト(10a)を設けることを少なくとも含む。こうして20nm〜5μmの長さおよびショットキー挙動を持つ制御コンタクト(10a)が得られる。Cuなどの低抵抗材料の使用によりゲート抵抗を減少させることができ、III−V族CMOSデバイスの高周波性能を改善できる。  (もっと読む)

(もっと読む)

半導体装置及びその作製方法

【課題】微細加工技術に依拠するのみでなく、半導体集積回路の高性能化を図ることを目的とする。また、半導体集積回路の低消費電力化を図ることを目的とする。

【解決手段】第1導電型のMISFETと第2導電型のMISFETとで単結晶半導体層の結晶方位又は結晶軸が異なる半導体装置を提供する。結晶方位又は結晶軸は、それぞれのMISFETにおいてチャネル長方向に走行するキャリアの移動度が高くなるように配設される。このような構成とすることで、MISFETのチャネルを流れるキャリアにとって移動度が高くなり、半導体集積回路の動作の高速化を図ることができる。また、低電圧で駆動することが可能となり、低消費電力化を図ることができる。

(もっと読む)

化合物半導体の熱処理方法及びその装置

【課題】化合物半導体を用いた半導体デバイスにおける界面準位や結晶欠陥等を低減することが可能な化合物半導体の熱処理方法を提供する。

【解決手段】被処理体Wの表面に電磁波を照射することにより化合物半導体に関する熱処理を施すようにする。これにより、化合物半導体を用いた半導体デバイスにおける界面準位や結晶欠陥等を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】対称フラットバンド電圧、同一ゲート電極材料かつ高誘電率誘電体層を有するCMISFETを提供する。

【解決手段】nMISFETは、半導体基板10の表面上に配置された第1ゲート絶縁膜16と、第1ゲート絶縁膜16上に配置されたM1xM2yO(M1=Y,La,Ce,Pr,Nd,Sm,Gd,Tb,Dy,Ho,Er,Tm,YbまたはLu,M2=Hf,Zr,Ta,x/(x+y)>0.12)で表される組成比を有する第1金属酸化物層20と、第2金属酸化物層24と、第2金属酸化物層24上に配置された第1導電層28とを備え、pMISFETは、半導体基板10表面上に配置された第2ゲート絶縁膜18と、第2ゲート絶縁膜18上に配置されたM3zM4wO(M3=Al,M4=Hf,Zr,Ta,z/(z+w)>0.14)で表される組成比を有する第3金属酸化物層22と、第4金属酸化物層26と、第4金属酸化物層26上に配置された第2導電層30とを備える半導体装置およびその製法。

(もっと読む)

半導体装置及びその作製方法

【課題】応答速度が高く、かつ、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】基板上に、接合層と、前記接合層上に、絶縁膜と、前記絶縁膜上に、単結晶半導体層と、前記単結晶半導体層中に、チャネル形成領域と、低濃度不純物領域と、シリサイド領域と、前記絶縁膜とシリサイド領域の間に、希ガス元素を含む非単結晶半導体膜と、前記単結晶半導体層上に、ゲート絶縁膜と、ゲート電極と、前記ゲート電極の側面に、サイドウォールとを有し、前記非単結晶半導体膜により、前記シリサイド領域中の金属元素が前記チャネル形成領域に拡散するのが抑制される半導体装置及びその作製方法に関する。

(もっと読む)

161 - 180 / 338

[ Back to top ]