Fターム[5F048BA15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 素子形成領域、能動領域がSi以外の材料 (1,343) | III−V族半導体 (338)

Fターム[5F048BA15]に分類される特許

81 - 100 / 338

集積半導体基板構造の製造方法

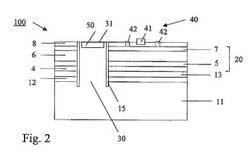

【課題】GaN素子およびCMOS素子の両方を備えた集積回路を製造するための改善した方法を提供する。

【解決手段】集積半導体基板構造100は、基板11と、GaNヘテロ構造20と、半導体基板層30とを備える。GaNヘテロ構造20は、第1素子エリアに存在し、少なくとも部分的に保護層8で覆われている。半導体基板層30は、CMOS素子の区画のための第2素子エリアに存在する。GaNヘテロ構造20および半導体基板層30の少なくとも1つが、基板11の少なくとも1つの溝内をエピタキシャル成長して形成され、GaNヘテロ構造20および半導体基板層30は横方向に並置される。

(もっと読む)

半導体デバイスおよび製造方法

【課題】Nチャネル型電界効果トランジスタとPチャネル型電界効果トランジスタとが同一基板上に形成された半導体デバイスにおいて、安定した電気的特性を得る

【解決手段】カーボンナノチューブCMOS1は、N型カーボンナノチューブFET2(以下、N型CN−FET2という)とP型カーボンナノチューブFET3(以下、P型CN−FET3という)とから構成される。N型CN−FET2は、カーボンナノチューブ14と、カーボンナノチューブ14上に形成されたゲート絶縁膜21を備え、ゲート絶縁膜21は酸化ハフニウムである。P型CN−FET3は、カーボンナノチューブ14と、カーボンナノチューブ14上に形成されたゲート絶縁膜31を備え、ゲート絶縁膜31は酸化アルミニウムである。これにより、N型CN−FET2のチャネル層近傍において、P型CN−FET3のチャネル層近傍よりも多くの正の固定電荷が導入される。

(もっと読む)

半導体デバイスの絶縁

【課題】半導体デバイスの絶縁構造の構造、および、形成方法を提供する。

【解決手段】当該絶縁構造は、底部が最上部よりも広くなっており、半導体デバイスの大きさを調整できる。第1のエッチングプロセスが、第1のトレンチ部分226を形成するために用いられ、第2のエッチングプロセスまたは酸化工程が、第1のトレンチ部分226の下に第2のトレンチ部分228を形成するために用いられる。第2のトレンチ部分は、第1のトレンチ部分よりも広い。一形態では、下地膜222が、第1のトレンチ部分の間、第1のトレンチ部分の側壁上に形成されてもよい(この第1のトレンチ部分は、第2のエッチングプロセスの間、第1のトレンチ部分の側壁を保護する)。あるいは、他の形態では、下地膜222が、第1のトレンチ部分の側壁上に堆積されていてもよい。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体装置を製作する方法

【課題】例えば大きな電荷キャリア移動度を有する半導体装置を製作する方法を提供する。

【解決手段】複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

半導体装置、半導体基板、及び半導体基板の処理方法

【課題】表面が(111)面以外であるシリコン層と、表面が(0001)面である窒化物半導体層とを基板に設け、かつシリコンと窒化物半導体の線膨張係数の違いに起因した応力を小さくする。

【解決手段】まずSOI(Silicon On Insulator)基板を準備する。SOI基板は、表面が(111)面であるシリコン基板100上に絶縁層120及びシリコン層200を積層した基板である。シリコン層200は、表面が(111)面以外の面方位である。次いで、絶縁層120及びシリコン層200に、底面にシリコン基板100が露出している開口部201を形成する。次いで、開口部201内にIII族の窒化物半導体層300を形成する。

(もっと読む)

半導体装置および電子機器

【課題】ノーマリーオフ動作を実現するとともに製造コストの増大を防ぐことが可能な半導体装置および電子機器を提供する。

【解決手段】半導体装置101は、第1の電界効果トランジスタF1の制御電極と第2電源ノードN2との間に接続され、第1の電界効果トランジスタF1の制御電極における電圧が所定値以上になると第1の電界効果トランジスタF1の制御電極から第2電源ノードN2への方向に導通するスイッチ素子ZDを備え、第1の電界効果トランジスタF1は、エピタキシャル成長用基板と、エピタキシャル成長用基板の主表面上に形成された半導体層とを含み、第1の電界効果トランジスタF1の第1導通電極、第2導通電極および制御電極は半導体層上に形成され、半導体層と電気的に接続され、第1の電界効果トランジスタF1の制御電極および半導体層によってショットキー接合が形成されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性を向上させる。

【解決手段】STI109と、STI109によって互いに分離されたp型ウェル102及びn型ウェル103と、p型ウェル102及びn型ウェル103上に形成されたSiGe膜108とを有するSi基板101を用意する工程と、n型ウェル103上に位置するSiGe膜108をSiO2膜116で被覆する工程と、SiO2膜116をマスクとして酸化処理を行うことによりp型ウェル102上に形成されたSiGe膜108を酸化し、SixGeyOz膜117を形成する工程((c))と、SixGeyOz膜117を除去する工程((d))と、を行い、半導体装置を製造する。

(もっと読む)

モノリシック垂直集積複合III−V族及びIV族半導体デバイス

【課題】3ー5族半導体デバイスを4族半導体デバイスと一緒に、単一のダイの上にモノリシック集積することができる半導体装置を提供する。

【解決手段】第1、第2の表面を有する両面仕上げ処理された半導体基板と、前記第1の表面上に形成され、一つの4族半導体デバイスを含む4族半導体層と、前記第2の表面上に形成され且つ前記少なくとも一つの4族半導体デバイスに電気的に結合された3−5族半導体デバイスを含む3−5族半導体本体130とを備える。さらに電気的結合のための基板ビア112及び/又はウェハ貫通ビア114を備える。4族半導体層はエピタキシャルシリコン層とすることができ、エピタキシャル層上に形成されたTFET及びショットキーダイオード(FETKY)とすることができる。また、3−5族半導体デバイスは高電子移動度トランジスタ(HEMT)170とすることができる。

(もっと読む)

ハイブリッド半導体基板の製造プロセス

【課題】ハイブリッド半導体基板及びその製造方法を提供する。

【解決手段】本発明は、(a)ベース基板3の上の絶縁層5と絶縁層の上のSeOI層7とを備えるセミコンダクタ−オン−インシュレータ(SeOI)領域13と、バルク半導体領域11とを具備するハイブリッド半導体基板1を提供するステップであって、SeOI領域とバルク半導体領域とは同じベース基板を共用するステップと、(b)SeOI領域の上にマスク層9を提供するステップと、(c)SeOI領域とバルク半導体領域を同時にドーピングすることにより、第1の不純物レベルを形成するステップであって、このドーピングは、SeOI領域の第1の不純物レベルがマスク内に含まれるように実行されるステップとを含む方法に関する。それによって、ハイブリッド半導体基板の製造プロセスに、より多くのプロセスステップが含まれることを防ぐ。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体デバイス及びその製造方法

【課題】 ワイドバンドギャップ半導体を用い、高い歩留まりを確保しつつ、低コストで製造することができる半導体デバイスを提供する。

【解決手段】 半導体モジュールは、SiC基板上に、個別に動作することが可能なセグメント1(半導体素子)を備えている。セグメント1は、SiC基板の主面側に設けられたソース電極パッド2及びゲート電極パッド3と、SiC基板の裏面側に設けられたドレイン電極パッドとを備えている。相隣接するセグメント1同士間を電気的に分離するためのトレンチ,ショットキーダイオード等の素子分離領域を備えている。検査で良品であることが確認されたセグメント1の電極パッド2,3のみが電極端子41,43に接続されている。

(もっと読む)

スレショルド電圧を有する電界効果トランジスタ、及びその製造方法

【課題】相異なるスレショルド電圧を有する電界効果トランジスタを提供する。

【解決手段】ドープ半導体ウエル上に、複数種のゲート・スタック(100〜600)が形成される。ドープ半導体ウエル(22、24)上に、高誘電率(high−k)ゲート誘電体(30L)が形成される。一つのデバイス領域中に金属ゲート層(42L)が形成され、他のデバイス領域(200、400、500、600)ではhigh−kゲート誘電体は露出される。該他のデバイス領域中に、相異なる厚さを有するスレショルド電圧調整酸化物層が形成される。次いで、スレショルド電圧調整酸化物層を覆って導電性ゲート材料層(72L)が形成される。電界効果トランジスタの一つの型は、high−kゲート誘電体部分を包含するゲート誘電体を包含する。電界効果トランジスタの他の型は、high−kゲート誘電体部分と、相異なる厚さを有する第一スレショルド電圧調整酸化物部分とを包含するゲート誘電体を包含する。相異なるゲート誘電体スタックと、同一のドーパント濃度を有するドープ半導体ウエルを用いることによって、相異なるスレショルド電圧を有する電界効果トランジスタが提供される。

(もっと読む)

半導体構造体およびその形成方法(内部応力を有する半導体ナノワイヤ)

【課題】高性能の相補型金属半導体(CMOS)回路の為の高いオン電流をもたらす半導体ナノワイヤ・デバイスを提供する。

【解決手段】両方の端部に半導体パッド33A、37Aを有する半導体ナノワイヤ32が、基板上にサスペンドされる。半導体ナノワイヤが応力発生ライナ部によって長手方向の応力を受けている間、半導体ナノワイヤの中間部の上にゲート誘電体36及びゲート電極38が形成される。ゲート誘電体及びゲート電極の形成によって半導体ナノワイヤの歪み状態が固定されるため、半導体ナノワイヤの中間部は、応力発生ライナの除去後に長手方向の固有の内部応力を受ける。半導体パッド内にソース及びドレイン領域33B,37Bが形成され、半導体ナノワイヤ・トランジスタが得られる。ソース及びドレイン・パッドの上に、中間工程(MOL)誘電体層を直接形成することができる。

(もっと読む)

半導体構造体およびその製造方法(移動度が最適化された方位を有する半導体ナノワイヤ)

【課題】高いオン電流、低いオフ電流を与えるp型半導体ナノワイヤ・デバイス、n型半導体ナノワイヤ・デバイスを提供する。

【解決手段】各々が半導体リンク部30C,50Cと2つの隣接するパット部30A,30B,50A,50Bを含む半導体構造体で、半導体リンク部の側壁は、第1の半導体構造体の場合には正孔の移動度を最大化するように、第2の半導体構造体の場合には電子の移動度を最大化するように方位を定める。半導体構造体の酸化による薄化で、半導体リンク部の幅は、異なる結晶方位ごとに異なる速度で小さくされる。異なる量の薄化の結果、薄化後に得られる半導体ナノワイヤが目標とするサブリソグラフィ寸法となるように、予め決定される。異なる結晶面に対する異なる薄化速度を補償することによって、過剰な薄化又は不十分な薄化がなされることなく、最適なサブリソグラフィ幅を有する半導体ナノワイヤを形成する。

(もっと読む)

金属High−kFETのためのデュアル金属およびデュアル誘電体集積

【課題】本発明は、一つの実施形態において半導体デバイスを形成する方法を提供する。

【解決手段】該方法は、第一導電型領域および第二導電型領域を包含する基板を用意するステップと、基板の第一導電型領域および第二導電型領域の上のゲート誘電体とHigh−kの該ゲート誘電体上を覆う第一金属ゲート導体を包含するゲート・スタックを形成するステップと、第一金属ゲート導体の第一導電型領域中に所在する部分を除去して、第一導電型領域中に所在するゲート誘電体を露出するステップと、基板に対し窒素ベース・プラズマを印加するステップであって、窒素ベース・プラズマは、第一導電型領域中に所在するゲート誘電体を窒化し、第二導電型領域中に所在する第一金属ゲート導体を窒化する、該印加するステップと、少なくとも第一導電型領域中に所在するゲート誘電体上を覆う第二金属ゲート導体を形成するステップと、を含む。

(もっと読む)

半導体デバイス及びその製造方法

【課題】絶縁層を介して基板同士を貼り合わせることで、一方の基板上に形成された半導体層を他方の基板に形成できると共に、半導体層の結晶構造を損傷させることなく高品質に維持できる半導体デバイス及びその製造方法を提案する。

【解決手段】ECRプラズマを用いてIII−V族化合物半導体層7及びSi基板4上に酸化膜6a,6bを形成するようにしたことで、当該III−V族化合物半導体層7及び酸化膜6a,6bへのダメージが低減され、酸化膜6a,6bを平坦に形成できると共に、III−V族化合物半導体層7の結晶構造も損傷させることなく高品質に維持できる。これにより酸化膜6a,6bを介しSi基板4及びInP基板12同士を貼り合わせることで、一方のInP基板12上に形成されたIII−V族化合物半導体層7を他方のSi基板4に形成できると共に、III−V族化合物半導体層7の結晶構造を損傷させることなく高品質に維持できた半導体デバイス1を提案できる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

81 - 100 / 338

[ Back to top ]