Fターム[5F048BA15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 素子形成領域、能動領域がSi以外の材料 (1,343) | III−V族半導体 (338)

Fターム[5F048BA15]に分類される特許

61 - 80 / 338

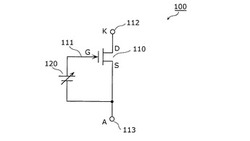

ダイオード回路

【課題】十分な逆方向耐圧を有し、順方向電圧が0Vに近い理想的なダイオード特性を有するダイオード回路を提供する。

【解決手段】アノード端子A及びカソード端子Kを有するアクティブダイオード100であって、ゲート端子111と、アノード端子A及びカソード端子Kの一方に接続されたドレイン端子112と、アノード端子A及びカソード端子Kの他方に接続されたソース端子113とを有するトランジスタ110と、トランジスタ110の閾値電圧に等しくなるように調整されたゲート電圧を、ゲート端子111に供給するゲート電圧発生回路120とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

垂直TFETの製造方法

【課題】ヘテロ構造ナノワイアを有するトンネル電界効果トランジスタと集積されたナノワイアを有する相補型トンネル電界効果トランジスタの製造方法を提供する。

【解決手段】犠牲材料21の層を有するチャネル材料34の層を含むスタック24を形成する工程と、チャネル材料34の層と犠牲材料21の層から、少なくとも1つのナノワイヤ30を形成するために、スタック24から材料を除去する工程と、第1ドーパント型の少なくとも1つのナノワイヤ30中の犠牲材料21を第1ドーパント型のヘテロ接合材料41で置き換えて、その後に、第2ドーパント型の少なくとも1つのナノワイア中の犠牲材料を、第2ドーパント材料のヘテロ接合材料52で置き換える工程を含み、相補型TFETの容易な製造が可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチング量を少なくしても素子分離膜の周辺にHigh−kゲート絶縁膜材料やゲート電極材料が残ることを抑制できるようにする。

【解決手段】素子分離膜102はSTI構造を有しており、基板101に埋め込まれており、かつトランジスタが形成される素子形成領域を分離している。素子分離膜102の側面の上端は、トランジスタのチャネル形成層よりも上に位置しており、かつチャネル形成層の表面から素子分離膜102の側面の最上部までの高さhが35nm以下である。また素子分離膜102のうちチャネル形成層よりも上に位置している部分の側面は、基板の表面に対する角度θが80度以下である。

(もっと読む)

半導体装置

【課題】破壊耐量が高い、2DEGを用いた半導体装置を提供する。

【解決手段】ソース・ドレイン間の耐圧よりも耐圧が低いSBDダイオード18のカソード電極がドレイン電極16に接続され、アノード電極がポリシリコンダイオード20を介してゲート電極14に接続されている。これにより、L負荷耐量試験回路によるL負荷耐量試験において、ゲート信号がターンオフされると、ドレイン電圧が印加され、SBDダイオード18にアバランシェ電流が流れ始め、電圧降下が発生し、ゲート電圧Vgが印加される。ゲートに閾値電圧Vthよりやや高い電圧(ゲートがオンする程度の電圧)が印加されると、ソース・ドレイン間が導通状態となる。これにより、ドレイン電圧がソース電極12とドレイン電極16との間の耐圧よりも低いSBDダイオード18の耐圧にクランプされた状態で、ドレイン電流が徐々に減少していく。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧の異なるトランジスタが同一半導体基板上に混載されている場合においても、それらのトランジスタの性能が向上するようにストレスライナ膜を構成することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に混載された低耐圧トランジスタおよび高耐圧トランジスタ上に形成するストレスライナ膜11、12は、互いに膜質を異ならせることができる。ここで、ストレスライナ膜11は、低耐圧トランジスタの性能が効果的に改善され、高耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。また、ストレスライナ膜11は、高耐圧トランジスタの性能が効果的に改善され、低耐圧トランジスタの性能があまり改善されないように膜質を設定することができる。

(もっと読む)

電界効果トランジスタおよび半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

保護素子及び半導体装置

【課題】半導体素子を保護する保護素子を備え、静電破壊が抑制され、信頼性の高い半導体装置を提供する。

【解決手段】半導体装置1は、チャネル層105とキャップ層112とを含む半導体積層体113と、半導体積層体113上に形成された下部電極213と上部電極216とを有する少なくとも1つの半導体素子1Xと、半導体素子1Xと共通の半導体積層体113を有し、半導体素子1Xを保護する少なくとも1つの保護素子1Yとを備えたものである。保護素子1Yは、キャップ層112を厚み方向に貫通するリセス部221と、リセス部221の底面221Bから半導体積層体113内に厚み方向に形成された絶縁領域218Yと、リセス部221を挟んで両側に形成されたキャップ層112に接続された一対のオーミック電極219、220とを備えたものである。

(もっと読む)

状態密度が設計された電界効果トランジスタ

【課題】nチャネルおよびp型チャネルトランジスタに用いられる層構造を提供する。

【解決手段】nチャネルトランジスタを製作するのに用いる層構造を含む。層構造は、伝導帯底EC1を有する第1の半導体層、離散正孔準位H0を有する第2の半導体層、第1と第2の半導体層との間に配置された広バンドギャップ半導体バリア層、第1の半導体層の上方に配置されたゲート誘電体層、およびゲート誘電体層の上方に配置されたゲート金属層を含み、離散正孔準位H0は、伝導帯底EC1の下方に位置され、ゲート金属層にゼロバイアスが供給される。

(もっと読む)

半導体装置

【課題】保護素子の素子面積を小さく抑え且つ製造工程を複雑にすることなくサージ耐性が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、第1の素子領域106Aに形成された第1のトランジスタ111と、第2の素子領域106Bに形成された第2のトランジスタ121を含む第1の保護素子とを備えている。第2の保護素子オーミック電極123Bは第1のゲート電極115と接続され、第1の保護素子オーミック電極123Aは第1のオーミック電極113Aと接続され、第1の保護素子ゲート電極115は、第1の保護素子オーミック電極123A及び第2の保護素子オーミック電極123Bの少なくとも一方と接続されている。第2の素子領域106Bの面積は、第1の素子領域106Aよりも小さい。

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

モノリシック集積複合III−V族及びIV族半導体デバイス、並びにその製造方法

【課題】単一のダイの上にIII−V族半導体デバイスをIV族半導体デバイスと共に集積する、複合デバイスの製造方法を提供する。

【解決手段】IV族半導体基板202上にIII−V族半導体本体274a,274bを形成するステップと、III−V族半導体本体にトレンチを形成し、トレンチ内にIV族半導体本体232を形成するステップとを有する。この方法は、IV族半導体本体内に少なくとも1つのIV族半導体デバイス272を製造するステップと、III−V族半導体本体内に少なくとも1つのIII−V族半導体デバイス274を製造するステップも含む。III−V族半導体本体の上面とIV族半導体本体の上面とを平坦化して、それぞれの上面をほぼ同一平面にするステップをさらに含む。一実施形態では、トレンチの側壁に隣接する、前記IV族半導体本体の欠陥領域に、少なくとも1つの受動デバイスを製造するステップをさらに含む。

(もっと読む)

共通基板上にカラムIII−VトランジスタとともにシリコンCMOSトランジスタを有する半導体構造

半導体構造は、ある結晶方位を有するシリコン基板(12)と、シリコン基板(12)の上方に配置された絶縁性層(18/22)と、絶縁性層の上方に配置され、基板の結晶方位とは異なる結晶方位を有するシリコン層(20)と、シリコン基板上に配置され、基板と同じ結晶方位を有するカラムIII−Vトランジスタデバイス(34)とを有する。一実施形態では、カラムIII−Vトランジスタデバイスが、基板と接触する。別の実施形態では、デバイスは、GaNデバイスである、または基板の結晶方位が<111>であり、シリコン層の結晶方位が<100>である。一実施形態では、CMOSトランジスタが、シリコン層内に配置される。一実施形態では、カラムIII−Vトランジスタデバイスが、カラムIII−Nデバイスである。一実施形態では、カラムIII−Asデバイス、カラムIII−Pデバイス、またはカラムIII−Sbデバイスが、<100>シリコン層の上面上に配置される。  (もっと読む)

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

半導体装置

【課題】待機電力の低減を実現する半導体装置の提供を、目的の一とする。

【解決手段】酸化物半導体を活性層として有するトランジスタをスイッチング素子として用い、該スイッチング素子で、集積回路を構成する回路への電源電圧の供給を制御する。具体的には、回路が動作状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を行い、回路が停止状態のときに上記スイッチング素子により、当該回路への電源電圧の供給を停止する。また、電源電圧が供給される回路は、半導体を用いて形成されるトランジスタ、ダイオード、容量素子、抵抗素子、インダクタンスなどの、集積回路を構成する最小単位の半導体素子を、単数または複数有する。そして、上記半導体素子が有する半導体は、結晶性を有するシリコン(結晶性シリコン)、具体的には、微結晶シリコン、多結晶シリコン、単結晶シリコンを含む。

(もっと読む)

半導体装置

【課題】半導体装置を構成するトランジスタを製造する際にトランジスタ能力のばらつきが発生しても、期待通りの性能を発揮することができる半導体装置を提供する。

【解決手段】半導体基板100上に、トランジスタ104A及び104Bと、電極パッド106とが形成されている。電極パッド106の上側領域を除く半導体基板100を覆うように、保護膜107が形成されている。トランジスタ104Aの上側領域を除く保護膜107を覆うように、凸方向に応力160を生じる保護膜108が形成されている。保護膜108によって、トランジスタ104Bの能力を基準として、トランジスタ104Aの能力が相対的に高く又は低く変動している。

(もっと読む)

61 - 80 / 338

[ Back to top ]