Fターム[5F048BA15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 素子形成領域、能動領域がSi以外の材料 (1,343) | III−V族半導体 (338)

Fターム[5F048BA15]に分類される特許

21 - 40 / 338

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

ネスト化複合スイッチ

【課題】高いスイッチング速度及び低いオン状態抵抗を有し、電圧降伏耐性を強化したネスト化複合スイッチを提供する。

【解決手段】ネスト化複合スイッチ240は、複合スイッチに結合されたノーマリオン・プライマリ・トランジスタを含む。複合スイッチは、中間型トランジスタ222とカスコード接続された低電圧(LV)トランジスタ224を含み、中間型トランジスタは、LVトランジスタよりは大きく、ノーマリオン・プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、ノーマリオン・プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVトランジスタはIV族LVトランジスタとすることができる。

(もっと読む)

ネスト化複合ダイオード

【課題】高いスイッチング速度を有し、電圧降伏耐性を強化したネスト化複合ダイオードを提供する。

【解決手段】ネスト化複合ダイオードの種々の実現を、本明細書に開示する。1つの実現では、ネスト化複合ダイオードが、複合ダイオードに結合されたプライマリ・トランジスタを含む。複合ダイオードは、中間型トランジスタとカスコード接続された低電圧(LV)ダイオードを含み、中間型トランジスタは、LVダイオードよりは大きく、プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVダイオードはIV族LVダイオードとすることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

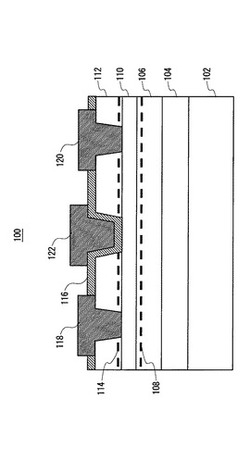

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層104に形成された第1チャネル型の第1MISFET120の第1ソース124および第1ドレイン126が、第1半導体結晶層104を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、またはニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層106に形成された第2チャネル型の第2MISFET130の第2ソース134および第2ドレイン136が、第2半導体結晶層106を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、または、ニッケル原子とコバルト原子との化合物からなる。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1及び第2のノードを有する論理回路と、第1のノードに接続された第1の記憶回路と、第2のノードに接続された第2の記憶回路と、第1のノード、第2のノード、第1の記憶回路、及び第2の記憶回路に接続されたプリチャージ回路と、を有し、読み出しの際に、プリチャージ回路は、プリチャージ電位を第1のノード及び第2のノードに出力し、第1の記憶回路及び第2の記憶回路は、チャネルが酸化物半導体膜に形成されるトランジスタを含む記憶装置である。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置

【課題】電源をオフしてもデータを保持することができ、退避動作と復帰動作が不要なレジスタ回路を提供する。

【解決手段】複数のレジスタ構成回路と、オフ電流が小さい第1のトランジスタと、オフ電流が小さい第2のトランジスタと、を有するレジスタ回路において、データ保持部を前記第1のトランジスタのソース及びドレインの一方に接続し、前記第2のトランジスタのソース及びドレインの一方に接続する。前記第1のトランジスタ及び前記第2のトランジスタはオフ電流が小さいので、データ保持部の電荷がリークせず、レジスタ回路の電源をオフしてもデータ保持部にデータが保持される。そのため、退避動作と復帰動作を行わなくてよい。

(もっと読む)

半導体装置

【課題】トランジスタが仮にディプレッション型である場合でも、安定して動作することができる半導体装置を提供する。

【解決手段】開示する発明の一態様の半導体装置は、第1の電位を第1の配線に供給する機能を有する第1のトランジスタと、第2の電位を第1の配線に供給する機能を有する第2のトランジスタと、第1のトランジスタのゲートに第1のトランジスタがオンをオンにするための第3の電位を供給した後、第3の電位の供給を止める機能を有する第3のトランジスタと、第2の電位を第1のトランジスタのゲートに供給する機能を有する第4のトランジスタと、第1の信号にオフセットを施した第2の信号を生成する機能を有する第1の回路と、を有し、第4のトランジスタのゲートには、第2の信号が入力され、第2の信号の最小値は、第2の電位未満の値である。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

半導体装置

【課題】周辺の回路構成を複雑にすることなく、繰り返しのデータの書き込みの際の劣化を低減することが可能な、不揮発性スイッチとして用いる半導体装置を提供する。

【解決手段】電源電圧が停止しても導通状態に関するデータの保持を、チャネル形成領域に酸化物半導体層を有する薄膜トランジスタに接続されたデータ保持部で行う構成とする。そしてデータ保持部は、ダーリントン接続された電界効果トランジスタ及びバイポーラトランジスタを有する電流増幅回路における、電界効果トランジスタのゲートに接続することでデータ保持部の電荷をリークすることなく、導通状態を制御する。

(もっと読む)

ハイブリッドMOSFETデバイスの製造方法およびそれにより得られるハイブリッドMOSFET

【課題】第1および第2のチャネル材料をそれぞれ有する第1MOSFETと第2MOSFETを含むハイブリッドMOSFETデバイスの製造方法を提供する。

【解決手段】III−Vオン絶縁体スタックは、続いて第1基板に接続される第2基板の上に形成される。III−V層103および絶縁体層は第1領域から選択的に除去されて、これにより第1基板の半導体層が露出する。第1MOSFETの第1ゲートスタック109は第1領域の露出した半導体層上に形成される。第2MOSFETの第2ゲートスタック109’は第2領域のIII−V層の上に形成される。

(もっと読む)

21 - 40 / 338

[ Back to top ]