Fターム[5F048BA15]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 基板 (9,458) | 素子形成領域、能動領域がSi以外の材料 (1,343) | III−V族半導体 (338)

Fターム[5F048BA15]に分類される特許

321 - 338 / 338

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

ナノワイヤによってコンタクトがとられる導電性材料の層を有する電子装置を製造する方法

本発明による電子装置(100)は、第1値と第2値との間で電気的にスイッチ可能な電気抵抗率を有するメモリ材料の層(107)を備える。メモリ材料は相変化材料でもよい。電子装置(100)は電子装置の第1端子(172)とメモリ材料の層(107)を電気的に接続する一組のナノワイヤ(NW)をさらに備え、それによって、第1端子からナノワイヤ(NW)及びメモリ材料の層(107)を介して電子装置の第2端子(272)への電流の伝導を可能にする。各ナノワイヤ(NW)は各々のコンタクト領域でメモリ材料の層(107)に電気的にコンタクトがとられる。全てのコンタクト領域ほぼ同一である。本発明による方法は、本発明による電子装置(100)を製造するのに適している。  (もっと読む)

(もっと読む)

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

本発明は、印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。本発明の方法、デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成することができる。また、本発明は、伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスも提供する。 (もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

SOI(semiconductoroninsulator)基板、およびこの基板から形成されるデバイス

レアアース・スカンデートのようなペロブスカイト格子構造を有する絶縁材料の層を含むSOI(semiconductor on insulator)デバイスである。この絶縁材料(52)は、この絶縁材料(52)のすぐ上にダイヤモンド格子を有する半導体材料(54)を成長させることができる、有効な格子定数を有するように選択される。レアアース・スカンデート絶縁体の例としては、ガドリニウム・スカンデート(GdScO3)、ジスプロシウム・スカンデート(DyScO3)、およびガドリニウムとジスプロシウム・スカンデートの合金(Gd1-xDyXScO3)が含まれる。  (もっと読む)

(もっと読む)

適切なソース、ドレイン及びチャネル材料を有する電界効果トランジスタとそれを有する集積回路

ノーマリーオンのトランジスタはソース(10)、ドレイン(11)及びチャネル(7)を備える。ソース、ドレイン及びチャネル材料は、NMOS型トランジスタではドレイン材料の電子親和力Xdがチャネル材料の電子親和力Xcより低く、ソース材料の電子親和力Xsがチャネル材料の電子親和力Xcより高くなるように(Xd<Xc<Xs)選択される。さらに、PMOS型トランジスタではドレイン材料の価電子帯の上限Edがチャネル材料の価電子帯の上限Ecより高く、ソース材料の価電子帯の上限Esがチャネル材料の価電子帯の上限Ecより低くなるように(Es<Ec<Ed)材料が選択される。  (もっと読む)

(もっと読む)

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ

ダイアモンド状のカーボンチャネルを有する電界効果トランジスタの製造方法、及び該製造方法により製造されるトランジスタ。

前記電界効果トランジスタは、ゲート絶縁膜(3)によりチャネル(7)から分離されたゲート電極(5)により制御されるチャネル(7)により接続されるソース(10)及びドレイン(11)を含む。前記チャネル(7)はダイアモンド状のカーボン層により形成される。前記トランジスタの製造方法は、続いて、ダイアモンド状のカーボン層を基板上(2)に堆積させ、ゲート絶縁層(3)を堆積させ、そして、少なくとも1つの導電層(4)を堆積させることを含む。前記導電層(4)は前記ゲート電極(5)からエッチングされる。次に、側面の絶縁膜(6)を形成するために、前記ゲート電極(5)の側面に絶縁材料が堆積される。次に、前記ゲート絶縁層(3)がエッチングされ、そして、前記ダイアモンド状のカーボン層がチャネル(7)の輪郭を描くようにエッチングされる。次に、前記ソース(10)を形成するための半導体材料、及び前記ドレイン(11)を形成するための半導体材料がチャネル(7)の両側に堆積される。  (もっと読む)

(もっと読む)

CMOSシリサイド金属ゲート集積化

本発明は、ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。本発明の集積化方式を用いて形成される各シリサイド金属ゲートは、シリサイド金属ゲートの寸法に関わりなく、同じシリサイド金属相および実質的に同じ高さを有する。本発明は、半導体構造物の表面全体にわたってポリSiゲート高さが実質的に同じであるシリサイド接点を有するCMOS構造物を形成するさまざまな方法も提供する。

(もっと読む)

(もっと読む)

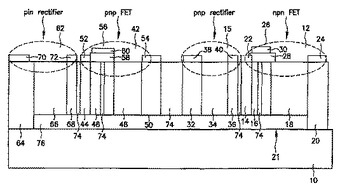

相補的窒化膜トランジスタの垂直およびコモンドレイン

【課題】少ない材料で、電流搬送能力に優れた半導体デバイスを提供する。

【解決手段】 異なる平面に、オーミック接点を含む半導体デバイス、およびそのデバイスを製造するための方法であって、連続したステップで、異なる導電タイプの半導体層の半導体スタックをエッチングし、第1半導体層内に、第1の幅の第1開口部を形成し、別の半導体層を露出させ、次に別の層内に、より狭い幅の第2開口部を形成し、オーミック接点を収容するための別の層の一部を、露出した状態で残すことを含む。

(もっと読む)

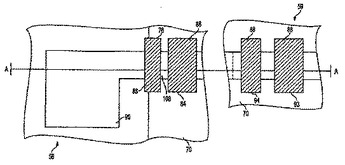

コンプリメンタリ横型窒化物トランジスタ

基板の支持表面上に形成された、横方向に隣接した導電性半導体領域により構成された横方向に延びているスタックを備える半導体デバイスおよびそのデバイスを作製する方法。  (もっと読む)

(もっと読む)

シャロウトレンチ分離プロセスおよび構造

集積回路(IC)を製造する方法は、シャロウトレンチ分離(STI)技術を利用する。シャロウトレンチ分離技術は歪みシリコン(SMOS)プロセス中において使用される。トレンチ(34)を形成した後、歪み材料(36)を形成する。このプロセスは、埋込酸化膜(BOX)層(14)上の化合物半導体層16上で利用される。  (もっと読む)

(もっと読む)

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

イメージャ用デュアルコンデンサ構造及びその製造方法

異なる画素内コンデンサ及び周辺コンデンサを含むCMOS及びCCD撮像装置とその製造方法を開示する。周辺回路において使用されるコンデンサと、画素自体の中で使用されるコンデンサの必要条件は異なる。2つの誘電体層を含むデュアルスタックコンデンサを提供することで、漏れが低減されると共に、静電容量を大きくすることができる。一回のマスキング工程を行って、1つの領域にはデュアル誘電体コンデンサを、そして第2の領域にはシングル誘電体コンデンサを存在させる。領域毎に異なる誘電体層が提供されるが、電極間絶縁体は両領域において単一の誘電体を含む。  (もっと読む)

(もっと読む)

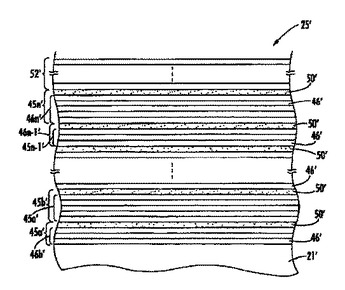

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。また装置は、電荷キャリアが積層された層群と平行な方向に超格子を通って輸送される領域を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。

(もっと読む)

(もっと読む)

格子不整合エピタキシャル拡張領域ならびにソースおよびドレイン領域を有するひずみチャネルCMOSトランジスタ構造体およびその製造方法

【課題】n型電界効果トランジスタ(NFET)およびp型電界効果トランジスタ(PFET)がそれぞれ、第1の半導体の単結晶層内に配置されたチャネル領域を有し、PFETのチャネル領域には第1の大きさの応力が加えられているが、NFETのチャネル領域にはその大きさの応力が加えられていない構造体およびその製造方法を提供すること。

【解決手段】この応力は、第1の半導体とは格子不整合の第2の半導体の層によって加えられる。この第2の半導体の層は、PFETのソースおよびドレイン領域ならびに拡張領域の上の、PFETのチャネル領域から第1の距離のところに形成されており、この第2の半導体の層は、NFETのソースおよびドレイン領域の上の、NFETのチャネル領域からより大きな第2の距離のところにも形成されており、またはNFETには全く形成されていない。

(もっと読む)

バンド設計超格子を有する半導体装置を製作する方法

複数の積層された層群を有する超格子を形成するステップによって、半導体装置を製作する方法である。また当該方法は、前記超格子を通って、前記積層された層群と平行な方向に、電荷キャリアの輸送が生じる領域を形成するステップを有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。前記エネルギーバンド調整層は、基本半導体部分に隣接する結晶格子内に取りこまれた、少なくとも一つの非半導体分子層を有し、前記超格子は、超格子が存在しない場合に比べて、前記平行な方向において大きな電荷キャリア移動度を有する。また前記超格子は、共通のエネルギーバンド構造を有しても良い。

(もっと読む)

(もっと読む)

バンド設計超格子を有する半導体装置

半導体装置は、複数の積層された層群を有する超格子を有する。超格子の各層群は、基本半導体部分を定形する複数の積層された基本半導体分子層と、該基本半導体部分上のエネルギーバンド調整層と、を有する。さらにエネルギーバンド調整層は、少なくとも一つの非半導体分子層を有し、この層は、連接する基本半導体部分の結晶格子内に閉じ込められる。従って超格子は、平行な方向において、エネルギーバンド調整層がない場合に比べて大きな電荷キャリア移動度を有する。  (もっと読む)

(もっと読む)

321 - 338 / 338

[ Back to top ]