Fターム[5F048BC03]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 非対称構造 (1,107)

Fターム[5F048BC03]に分類される特許

161 - 180 / 1,107

半導体装置

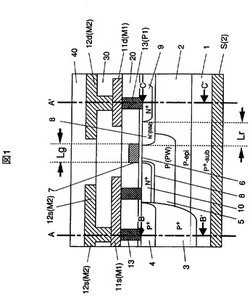

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

半導体装置

【課題】半導体基板へのリーク電流が少ないMOS構造をダイオードとして用いる半導体装置を提供する。

【解決手段】電界効果トランジスタと、抵抗素子20と、を備える。前記抵抗素子は、前記電界効果トランジスタのバックゲート電極24と一方のソース・ドレイン領域16との接続点23と、前記電界効果トランジスタのゲート電極19との間に接続されている。そして、前記電界効果トランジスタの他方のソース・ドレイン領域15と前記ゲート電極19との間に電圧が印加される。

(もっと読む)

半導体装置及びその製造方法

【課題】IGBT形成領域とその制御回路等形成領域とをPN接合分離法で分離し、且つIGBTからの漏れ電流が発生せず、制御回路等のCMOSトランジスタがラッチアップ等することのない高品質の半導体装置を実現する。

【解決手段】P型半導体基板1上に多層からなるN型エピタキシャル層3等を形成する。該N型エピタキシャル層3等をP+型分離層13等によりIGBT形成領域50と制御回路等形成領域40に分離する。該IGBT形成領域50の最下層の前記N型エピタキシャル層3と前記P型半導体基板1の双方に延在するN+型埋め込みガード層2を形成する。また該N+型埋め込みガード層2の端部と接続し前記エピタキシャル層3等の表面まで延在するN+型ガードリング9等を形成する。前記N+型埋め込みガード層2と該N+型ガードリング9等に囲まれた前記エピタキシャル層3等にIGBTを形成する。

(もっと読む)

静電気保護用のMOS型半導体装置

【課題】ESD素子のESD耐量を向上させる。

【解決手段】ESD素子21は半導体基板1表面に形成したP型ウェル領域2上にゲート絶縁膜を介して、一方向に延びた複数本のゲート電極3が相互に平行に設けられており、P型ウェル領域2の表面におけるゲート電極3の直下域がチャネル領域9になっている。そして、チャネル領域9間の領域がN+ソース領域5又はN+ドレイン領域4となっており、N+ソース領域5とN+ドレイン領域4とは交互に配列されている。そして、並列して隣接するゲート電極3間に位置するN+ドレイン領域4を分割し、かつ隣接するゲート電極3を接続するようにゲート電極接合領域10を設ける。なお、ゲート電極接合領域10の直下域にはチャネル領域9と同一の不純物濃度を有する領域11が設けられている。

(もっと読む)

半導体装置

【課題】占有面積を増大させずに、電源投入開始後のチップ動作時にESD保護素子で発生するリーク電流を低減することができるESD保護素子を提供する。

【解決手段】電源ライン及び接地ラインを含む電子回路が形成された半導体基板10と、半導体基板10において電源ライン(Vdd)及び接地ライン(Vss)間に設けられ、サイリスタSCR及びサイリスタを駆動するトリガーダイオードTDを含む静電気放電保護素子とを有し、トリガーダイオードは、半導体基板10に形成されたアノード拡散層22と、アノード拡散層22から離間して半導体基板10に形成されたカソード拡散層21と、アノード拡散層22及びカソード拡散層21間において半導体基板10上にゲート絶縁膜16を介して形成されたゲート電極17とを有し、外部電源に接続された外部端子(パッド電極27)がゲート電極17に電気的に接続されている構成とする。

(もっと読む)

半導体装置及び駆動方法

【課題】絶縁層上に形成された部分空乏型のトランジスターにおいて、ヒストリー効果を低減し、なおかつ高いON/OFF比、及び急峻なサブスレッショルド特性を実現する。

【解決手段】絶縁層上の半導体層に形成された第1導電型のソース領域、第1導電型のドレイン領域、及び、第2導電型のボディ領域と、第1ゲート絶縁膜と、第1ゲート電極と、を含む部分空乏型の第1トランジスターと、絶縁層上の半導体層に形成された第2導電型のソース領域、第2導電型のドレイン領域、及び、第1導電型のボディ領域と、第2ゲート絶縁膜と、第2ゲート電極と、を含む第2トランジスターと、を具備し、第1トランジスターの第2導電型のボディ領域は、第2トランジスターの第2導電型のソース領域及び第2導電型のドレイン領域の内の一方に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル層および高濃度埋め込み拡散領域を有することなく、順バイアス動作時の基板リーク電流を効果的に抑制する。

【解決手段】P型半導体基板1内にN型拡散領域2を備え、N型拡散領域2内に、P型拡散領域3と、P型拡散領域3とは平面的に離間した位置に形成された高濃度N型拡散領域4とを備えている。P型拡散領域3内には、高濃度N型拡散領域5と高濃度P型拡散領域6が形成され、P型拡散領域3の上で高濃度N型拡散領域5と高濃度N型拡散領域4の間には、ゲート酸化膜を介してゲート電極7が形成され、ゲート電極7の一方端部が高濃度N型拡散領域5上にオーバーラップして形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体装置とその製造方法

【課題】良好な特性を有し且つ微細化を実現した半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、平面状シリコン層212上の柱状シリコン層208、柱状シリコン層208の底部領域に形成された第1のn+型シリコン層113、柱状シリコン層208の上部領域に形成された第2のn+型シリコン層144、第1及び第2のn+型シリコン層113,144の間のチャネル領域の周囲に形成されたゲート絶縁膜140、ゲート絶縁膜140の周囲に形成され第1の金属シリコン化合物層159aを有するゲート電極210、ゲート電極210と平面状シリコン層212の間に形成された絶縁膜129a、柱状シリコン層208の上部側壁に形成された絶縁膜サイドウォール223、平面状シリコン層212に形成された第2の金属シリコン化合物層160、及び第2のn+型シリコン層144上に形成されたコンタクト216を備える。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

交流スイッチ

【課題】高耐圧の用途に適用可能な交流スイッチ(半導体リレー)を提供する。

【解決手段】交流スイッチ1は、ソース(S)同士を接続した第1化合物半導体MOSFET11および第2化合物半導体MOSFET12と、第1化合物半導体MOSFET11のドレイン(D)に接続された第1出力端子13と、第2化合物半導体MOSFET12のドレイン(D)に接続された第2出力端子14とを含む。交流スイッチ1は、オフ時の第1出力端子13および第2出力端子14の間の耐圧が400V以上(より好ましくは600V以上)であり、オン時の第1出力端子13および第2出力端子14の間の抵抗が20mΩ以下(より好ましくは10mΩ以下)である。

(もっと読む)

半導体装置およびこれを用いた半導体リレー

【課題】高電圧印加時にリーク電流が流れるのを低減する。

【解決手段】第1導電型のSiC(シリコンカーバイド)基板1表面に形成したエピタキシャル成長層2内に、少なくとも一つのトランジスタセルを備え、このトランジスタセルは、エピタキシャル成長層2内に形成された第2導電型のウェル領域3と、このウェル領域3内に形成された第1導電型の領域からなるソース領域4と、ゲート絶縁膜6を介して形成されたゲート電極7と、前記ソース領域4にコンタクトするように形成されたソース電極5と、SiC基板1の第2の面側に形成されたドレイン電極9とを具備しており、このトランジスタセルのうちの最外セルの外側に、隣接してこのウェル領域を囲み、ゲート電極7およびソース電極5のいずれに対しても絶縁されたp型耐圧保持領域3pを具備している。

(もっと読む)

半導体装置の製造方法

【課題】 接着剤を用いることなく、かつ、容易にマスク部材を着脱することが可能な技術を提供する。

【解決手段】 第1吸着口112aと第2吸着口114aを有するステージ110とマスク部材120を使用する半導体装置の製造方法であって、第1吸着口112aが塞がれるようにステージ110上に半導体ウエハ100を載置するとともに、第1吸着口112aにより半導体ウエハ100を吸着固定する工程と、吸着固定されている半導体ウエハ100の上方にマスク部122が位置し、かつ、第2吸着口114aが塞がれるようにステージ110上にマスク部材120を載置するとともに、第2吸着口114aによりマスク部材120を吸着固定する工程と、吸着固定されているマスク部材120のマスク部122を通して吸着固定されている半導体ウエハ100に荷電粒子を注入する工程を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOS型トランジスタなどの半導体装置が動作中に生ずる経時的な特性変動を抑制すると共に、高耐圧かつ低オン抵抗が実現される半導体装置およびその製造方法を提供する。

【解決手段】 N型半導体層102に、深さが1μmより小さいP型の第1ドレインオフセット領域103と、深さが第1ドレインオフセット領域103より小さく、不純物濃度が第1ドレインオフセット領域103より大きいP型の第2ドレインオフセット領域105と、第1ドレインオフセット領域103より深いN型のボディ領域106と、N型のソース領域107およびドレイン領域104とを設ける。またLOCOS酸化膜からなる絶縁膜110と、ゲート絶縁膜108を介して形成されたゲート電極109とをN型半導体層102上に備える構造とする。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

半導体装置

【課題】出力用素子から半導体基板の内部に進入する電子により、被保護素子が誤動作を起こすことを抑制する半導体装置を提供する。

【解決手段】半導体基板と、出力用素子と、被保護素子TRSと、タップ部ATDと、第1のアクティブバリア構造ABRとを備える。第1のアクティブバリア構造ABRは、被保護素子TRSとタップ部ATDとの間に配置される。第1のアクティブバリア構造ABRは、p型不純物領域PSRに接続されたn型領域と、n型領域とオーミック接続されたp型領域とを含む。

(もっと読む)

半導体装置

【課題】キャリアのライフタイム制御に関わらず、寄生バイポーラトランジスタの動作を抑制し、耐量を向上させることができる構造の半導体装置を提供する。

【解決手段】ダイオード構造が形成された領域において、n-型ドリフト層1の裏面側に、p+型不純物領域2だけでなく部分的にn+型不純物領域3を形成する。これにより、p+型不純物領域2の幅が狭くなり、その結果、p+型不純物領域2のうちn+型不純物領域3との境界部から最も離れる場所までの距離が短くなる。したがって、n-型ドリフト層1の内部抵抗が小さくなることでバイアス電圧が小さくなり、寄生バイポーラトランジスタの動作を抑制することが可能となる。よって、キャリアのライフタイム制御に関わらず、寄生バイポーラトランジスタの動作を抑制し、耐量を向上させることが可能となる。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

161 - 180 / 1,107

[ Back to top ]