Fターム[5F048BC16]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 材料 (764) | 多結晶Si(SOI) (345)

Fターム[5F048BC16]に分類される特許

81 - 100 / 345

貼り合わせウェーハの製造方法

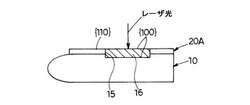

【課題】貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成可能な貼り合わせウェーハの製造方法を提供する。

【解決手段】高エネルギ光を、活性層用ウェーハの素材は溶融しないが、吸光係数が高いアモルファスシリコンは溶融する条件で貼り合わせ基板の活性層用ウェーハ側の面に照射し、この窓部内のシリコンを溶融させて固化させる。このとき、アモルファスシリコンを単結晶シリコンに液相エピタキシーにより変質させれば、貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成できる。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうる単結晶半導体層を備えた半導体基板の製造方法を提供する。

【解決手段】単結晶半導体基板上に酸化膜を形成し、酸化膜を介して半導体基板に加速されたイオンを照射することにより、半導体基板中に脆化領域を形成し、酸化膜を間に挟んで単結晶半導体基板と向かい合うように支持基板を貼り合わせ、単結晶半導体基板を加熱することにより、脆化領域において、単結晶半導体層が貼り合わされた支持基板と単結晶半導体基板の一部とに分離し、支持基板に貼り合わされた単結晶半導体層の表面に対して、基板バイアスを印加して第1のエッチングを行い、単結晶半導体層に対してレーザビームを照射して、単結晶半導体層の少なくとも表面の一部を溶融した後、凝固させ、単結晶半導体層の表面に対して、基板バイアスを印加することなく第2のエッチングを行う。

(もっと読む)

高次無線周波数高調波抑制領域を含む半導体オン・インシュレータ基板及び構造体

【課題】 抑制された高次無線周波数高調波を有する無線周波数デバイス及び無線周波数回路の製造を可能にする、半導体オン・インシュレータ基板及び関連した半導体構造体、並びに、半導体オン・インシュレータ基板及び関連した半導体構造体を製造する方法を提供する。

【解決手段】 半導体オン・インシュレータ基板及び関連した半導体構造体、並びに、半導体オン・インシュレータ基板及び関連した半導体構造体を製造するための方法が、半導体オン・インシュレータ基板内のベース半導体基板と埋込み誘電体層との界面の下方の位置において、ベース半導体基板内に配置及び形成された高次無線周波数高調波抑制領域をもたらす。高次無線周波数高調波抑制領域は、これに限定するものではないが、希ガス原子などのイオン注入原子を含むことができ、これに限定するものではないが、半導体構造体内の表面半導体層内及びその上に配置及び形成された無線周波数相補型金属酸化膜半導体デバイス(又は代替的には受動デバイス)などの無線周波数デバイスに電力供給するとき、抑制された高次無線周波数高調波をもたらす。

(もっと読む)

半導体装置

【課題】短チャネル効果および閾値の変動の双方を抑制することの可能な半導体装置を提供する。

【解決手段】p型MOSトランジスタ11が形成された第1領域10と、n型MOSトランジスタ21が形成された第2領域20との間に分離部37が形成されている。分離部37は、第1領域10と第2領域20との境界に沿って延在しており、第1領域10と第2領域20とを互いに分離している。分離部37は、さらに、p型MOSトランジスタ11のバックゲートおよびn型MOSトランジスタ21のバックゲートを、少なくとも双方のバックゲート間に電流が流れるのを阻害する程度に互いに電気的に分離している。

(もっと読む)

半導体装置及びその作製方法

【課題】大型の半導体装置で、高速に動作する半導体装置を提供することを目的する。

【解決手段】単結晶の半導体層を有するトップゲート型のトランジスタと、アモルファス

シリコン(またはマイクロクリスタルシリコン)の半導体層を有するボトムゲート型のト

ランジスタとを同一基板に形成する。そして、各々のトランジスタが有するゲート電極を

同じレイヤーで形成し、ソース及びドレイン電極も同じレイヤーで形成する。このように

して、製造工程を削減する。つまり、ボトムゲート型のトランジスタの製造工程に、少し

だけ工程を追加するだけで、2つのタイプのトランジスタを製造することが出来る。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

半導体装置の作製方法

【課題】複数の半導体集積回路を接続する配線の位置を容易に決定することを課題にする。

【解決手段】第1の基板上に第1の分離層と第1の半導体素子層を形成し、第1の半導体素子層に第1のレーザビームを照射することにより第1の開口部を形成し、第1の開口部に第1の半導体素子層と接続する第1の配線を形成し、第1の半導体素子層上に第1の保護材を形成し、第1の保護材に第1の配線に接続する第1の電極を形成し、第1の分離層に沿って第1の基板と第1の半導体素子層を分離し、上述の作製工程により第2の基板上に、第2の分離層、第2の半導体素子層、第2の配線、第2の保護材、第2の電極を作製し、第2の電極と第1の配線を接続するように第2の保護材上に第1の半導体素子層を貼り合わせ、第2の分離層に沿って第2の基板と第2の半導体素子層を含む積層構造を分離する半導体装置の作製方法に関する。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

半導体装置

【課題】歪みシリコン技術を用いて効果的に駆動力を向上させた半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板上に形成された半導体層と、前記半導体層内にソース・ドレイン領域およびチャネル領域を有するトランジスタと、前記半導体基板と前記半導体層の間の、前記チャネル領域の下方に形成され、前記チャネル領域に歪みを発生させる応力を内包した絶縁膜と、を備える。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】スイッチ部またはバッファ部と、論理回路部と、画素部と、を有する表示装置において、画素部は、第1の逆スタガ型薄膜トランジスタと、第1の逆スタガ型薄膜トランジスタの配線に接続する画素電極と、を有し、スイッチ部またはバッファ部は、第1の絶縁層、半導体層、及び第2の絶縁層を挟む第1のゲート電極及び第2のゲート電極を有する第2の逆スタガ型薄膜トランジスタを有し、論理回路部は、第3の逆スタガ型薄膜トランジスタ及び第4の逆スタガ型薄膜トランジスタにより構成されるインバータ回路を有し、第1の逆スタガ型薄膜トランジスタ乃至第4の逆スタガ型薄膜トランジスタは、同じ極性とする。インバータ回路はEDMOS回路である。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】スイッチ部またはバッファ部と、論理回路部と、画素部と、を有する表示装置において、画素部は、第1の逆スタガ型薄膜トランジスタと、第1の逆スタガ型薄膜トランジスタの配線に接続する画素電極と、を有し、スイッチ部またはバッファ部は、第1の絶縁層、半導体層、及び第2の絶縁層を挟む第1のゲート電極及び第2のゲート電極を有する第2の逆スタガ型薄膜トランジスタを有し、論理回路部は、第3の逆スタガ型薄膜トランジスタ及び第4の逆スタガ型薄膜トランジスタにより構成されるインバータ回路を有し、第1の逆スタガ型薄膜トランジスタ乃至第4の逆スタガ型薄膜トランジスタは、同じ極性とする。インバータ回路はEDMOS回路である。

(もっと読む)

SOI基板の作製方法

【課題】SOI基板の作製方法において、非質量分離型のイオン照射方法を用いる場合であっても、単結晶半導体基板の分離を良好に行い、分離後の単結晶半導体層の表面の平坦性を向上させることを目的の一とする。又は、SOI基板の作製方法において、スループットを向上させると共に分離後の単結晶半導体層の表面の平坦性を向上させることを目的の一とする。

【解決手段】単結晶半導体基板に加速されたイオンを照射することにより単結晶半導体基板中に脆化領域を形成する工程と、絶縁層を介して単結晶半導体基板とベース基板とを貼り合わせる工程と、脆化領域において単結晶半導体基板を分離して、ベース基板上に絶縁層を介して単結晶半導体層を形成する工程とを有し、単結晶半導体基板へのイオンの照射は、イオンドーピング法を用い且つ単結晶半導体基板を冷却しながら行う。

(もっと読む)

発振回路及び半導体装置

【課題】特別な回路を付加することなく、消費電力を十分に低減できるようにした発振回路及び半導体装置を提供する。

【解決手段】信号反転増幅器10と、フィードバック回路とを備え、信号反転増幅器10は、SOI基板10にそれぞれ形成されたpチャネル型のPD−SOI−MOSFET11及びnチャネル型のPD−SOI−MOSFET12を有し、フィードバック回路は、信号反転増幅器10の出力側と入力側との間に接続された水晶振動子21を有する。信号反転増幅器10では、MOSFET11、12が直列に接続されると共に、直列に接続されたMOSFET11、12の両端に電圧が印加される。また、フィードバック回路は、信号反転増幅器10から出力された信号を当該信号反転増幅器10にフィードバック入力する。

(もっと読む)

半導体装置の作製方法

【課題】 電気光学装置の製造コストを低減する技術を提供する。

【解決手段】 電気光学装置を形成するTFTの作製方法において、必要とするパターニング回数を極力低減することにより、製造コストの低減を図る。具体的には、ゲート配線をマスクとして活性層に不純物元素を添加した後、該ゲート配線の線幅をパターニング工程を施すことなく狭め、再度不純物元素を添加する。これによりパターニング回数を増やすことなくLDD領域を形成できる。

(もっと読む)

表示装置およびその製造方法

【課題】マスク工程の増大なく、薄膜トランジスタのゲート絶縁膜、および配線交差部における層間絶縁膜において、それぞれ適切な厚さを有して形成できる表示装置の提供。

【解決手段】絶縁基板上に、第1第2の薄膜トランジスタを形成する工程と、前記第1薄膜トランジスタのゲート電極、前記第2薄膜トランジスタのゲート電極、前記ゲート信号線をも被って絶縁膜を形成する工程と、前記絶縁膜上に脱水素化した第1非晶質シリコン半導体層を形成する工程と、前記第1薄膜トランジスタの形成領域における前記第1非晶質シリコン半導体層を多結晶シリコン半導体層に変質させる工程と、前記第2薄膜トランジスタの形成領域における前記非晶質シリコン半導体層、前記絶縁膜の表面からの一部を順次エッチングする工程と、前記多結晶シリコン半導体層および前記第1非晶質シリコン半導体層をも被って前記絶縁膜上に第2非晶質シリコン半導体層を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】バックゲート電極を有するTFTの製造方法として裏面露光を用いて露光して後、イオン注入法を用いて高濃度ドレイン領域を形成し、ゲート電極をマスクとして低濃度ドレイン領域を形成すると、低濃度ドレイン領域中にはバックゲート電極端を配置することができず、低濃度ドレイン領域中での電界集中の緩和が困難になるという課題がある。

【解決手段】絶縁基板10Subの表面側にフォトレジスト層11Prを塗布し、乾燥させる。そして、絶縁基板10Subの裏面から、88°程度に傾けて露光し、続けて現像工程を行う。この工程を用いることでバックゲート電極10Bgn端部は低濃度ドレイン領域中に配置される。そのため、ゲート電極端とバックゲート電極10Bgn端で電界が分散されて吸収される。そのためホットキャリアの発生が抑えられ、信頼性が高いTFTを得る工程を提供することが可能となる。

(もっと読む)

薄膜半導体装置

【課題】 高移動度及び閾値電圧のばらつきの少ない大粒径多結晶半導体を用いた薄膜半導体装置を提供すること。

【解決手段】 絶縁基板上に成膜された多結晶半導体薄膜に形成された薄膜半導体素子を具備する薄膜半導体装置であって、前記薄膜半導体素子は、ソース領域、ドレイン領域、及びこれらの間に介在するチャネル領域を具備し、前記チャネル領域に存在する多結晶半導体の結晶粒の主要な面方位は、半導体結晶の逆極点図において、{100}、{310}、及び{311}により囲まれた領域内の面方位であることを特徴とする。

(もっと読む)

半導体装置

【課題】 LDD形成工程に於けるプラズマプロセスが原因となり生じる素子の

損傷を極力低減した半導体装置の作製方法を提供すること。

【解決手段】 基板全面を覆うように導電性膜を形成した状態で、ハードマスク

を利用した半導体装置の作製方法でLDD構造の素子を形成することにより、L

DD形成工程におけるプラズマプロセスによる素子への損傷を極力低減する。導

電性膜が全面に形成されていることにより、異方性エッチング等のプラズマによ

る処理(プラズマプロセス)においてゲート電極に蓄積される電荷密度を低減で

き、プラズマプロセスによる損傷を低減できる。

(もっと読む)

半導体装置とその製造方法

【課題】 エミッタ注入効率が大きく、差動増幅回路の入力トランジスタとして利用可能で、かつBi−CMOSプロセスにおいてMOSトランジスタと同一基板上に搭載することが可能なバイポーラトランジスタの構造とその製造方法を提供する。

【解決手段】 半導体基板1上に第二導電型の深いウェル層2が形成され、深いウェル層2よりは浅い所定の深さで第一導電型の埋め込み層3が形成され、バイポーラトランジスタのエミッタ領域が、第一導電型の埋め込み層3の上に、第二導電型のウェル層4、及びMOSトランジスタのソース・ドレイン領域と同時形成される高濃度の第二導電型の不純物層15の2層構造として形成されている。

(もっと読む)

半導体装置、TFT基板、表示装置、携帯機器

【課題】同一絶縁基板上に形成された2つのトランジスタの拡散層の抵抗値を同じにすることのできる新構造のトランジスタを搭載した半導体装置を提供する。

【解決手段】第1のトランジスタ(図中左側のトランジスタ)は、第1のゲート電極304a下部に形成された第1の絶縁膜303aと、拡散層領域302a2,302a3上に形成された第2の絶縁膜303bとを備え、これら第1の絶縁膜303a及び第2の絶縁膜303bより上層に第1のゲート電極304aが配置されており、かつ、第1の絶縁膜303aが第2の絶縁膜303bよりも薄く形成され、第1のトランジスタの第2の絶縁膜303bは、第1のゲート電極304aの下面縁部から内側まで入り込んで形成され、拡散層領域302a2,302a3は、第1の絶縁膜303aの下までオーバーラップして形成された構造となっている。

(もっと読む)

81 - 100 / 345

[ Back to top ]