Fターム[5F048BC16]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ソース・ドレイン (8,322) | 材料 (764) | 多結晶Si(SOI) (345)

Fターム[5F048BC16]に分類される特許

41 - 60 / 345

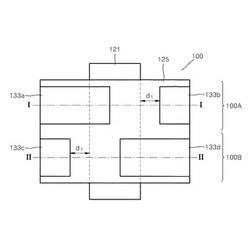

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

SOI基板の作製方法

【課題】エアボイドなどの貼り合わせに起因する欠陥を十分に抑制できるSOI基板の作製方法を提案することを目的の一とする。

【解決手段】ボンド基板とベース基板を対向させ、ボンド基板またはベース基板の端部に圧力をかけてボンド基板とベース基板の貼り合わせを開始させる時、または前に、ボンド基板表面、または、ベース基板表面の貼り合わせの開始地点における接平面に対して、ボンド基板における貼り合わせの終了地点がベース基板から離れるようにボンド基板を反らせ、および/または、ベース基板における貼り合わせの終了地点がボンド基板から離れるようにベース基板を反らせ、貼り合わせを開始させた後に、ボンド基板の反り量、および/または、ベース基板の反り量を制御することにより、ボンド基板とベース基板の貼り合わせに係る速度を制御する、SOI基板の作製方法である。

(もっと読む)

半導体基板の保持用トレイ、並びに半導体基板および半導体装置の作製方法

【課題】複数枚の絶縁層被覆単結晶半導体基板に対して効率よくイオン注入を行い、大面積の単結晶半導体層を備えた半導体基板の作製方法を提供することを課題の一とする。

【解決手段】半導体基板の作製工程において、表面のファンデルワールス力を調整した保持用トレイに表面に絶縁層が形成された複数枚の単結晶半導体基板を貼り合わせ、複数枚の単結晶半導体基板にイオン照射工程を行うことで複数枚の単結晶半導体基板の所定の深さに脆化層を形成し、複数枚の単結晶半導体基板にファンデルワールス力を調整したベース基板を貼り合わせることでファンデルワールス力の差を利用して保持用トレイを選択的に分離し、剥離加熱処理を行い劈開面を形成して単結晶半導体基板をベース基板から分離することにより、絶縁層を介して単結晶半導体基板をベース基板に転載する。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体装置及び電子機器

【課題】逆スタガ型TFTにおいて、薄膜の応力を用いてしきい値電圧を制御する。

【解決手段】基板上に形成された電極上に設けられた第1の絶縁層の応力と膜厚の積と、前記第1の絶縁層上に設けられた引張り応力を有する結晶質半導体膜からなる活性層の応力と膜厚の積と、前記活性層上に設けられた第2の絶縁層の応力と膜厚の積を適当な大きさに設定することでしきい値電圧を制御する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法、半導体基板の再生に適した方法を用いた再生半導体基板の作製方法、及び当該再生半導体基板を用いたSOI基板の作製方法の提供を目的とする。

【解決手段】損傷した半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層が除去されるエッチング処理と、半導体基板を構成する半導体材料を酸化する物質、酸化された半導体材料を溶解する物質、及び、半導体材料の酸化の速度及び酸化された半導体材料の溶解の速度を制御する物質、を含む混合液を用いて、未損傷の半導体領域に対して損傷半導体領域が優先的に除去されるエッチング処理と、レーザ光照射工程と、を行うことで半導体基板を再生する。

(もっと読む)

半導体装置およびその製造方法

【課題】オフトラ型ESD保護素子のESD耐量を増加する。

【解決手段】第2導電型ドレイン高濃度拡散層となる領域にトレンチを備え、トレンチ内に第2導電型の多結晶シリコン膜を埋め込むことで、第2導電型ドレイン高濃度拡散層の実効的な体積を増加することを実現する。これより、ゲート電極からドレインコンタクト孔の距離を大きくしたことと同じ効果が得られ、本発明の半導体装置はオフトラ型ESD保護素子として、素子サイズを変更しなくてもESD耐量の増加が可能となる。

(もっと読む)

電気光学装置及び電子機器、並びに電気光学装置の製造方法

【課題】液晶装置等の電気光学装置において、TFTで発生する光リーク電流を低減させ

る。

【解決手段】電気光学装置は、表示領域(10a)に設けられた複数の画素電極(9a)

と、画素電極に画像信号を供給するデータ線(6a)と、画素電極に電気的に接続された

画素電極側ソースドレイン領域(1e)、データ線に電気的に接続されたデータ線側ソー

スドレイン領域(1d)、並びに画素電極側ソースドレイン領域及びデータ線側ソースド

レイン領域間に位置するチャネル領域(1a’)を有する半導体層(1a)と、半導体層

のチャネル領域にゲート絶縁膜(2a,2b)を介して対向配置されたゲート電極(3b

)とを備える。半導体層は、チャネル領域の膜厚が、画素電極側ソースドレイン領域及び

データ線側ソースドレイン領域の膜厚より薄くなるように形成されている。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便な製造方法によって製造された良好なTFT特性を有する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、絶縁基板11と、絶縁基板11に支持されたチャネル領域33A、ソース領域34Aおよびドレイン領域35Aを含む半導体層30Aと、チャネル領域33Aの導電性を制御するゲート電極51とを有する。半導体層30Aは、チャネル領域33Aとソース領域34Aとの間に形成された第1低濃度領域31A、および、チャネル領域33Aとドレイン領域35Aとの間に形成された第2低濃度領域32Aとを有する。チャネル領域33A、第1および第2低濃度領域31Aおよび32Aは、ソースおよびドレイン領域34Aおよび35Aの不純物濃度より低い第1不純物濃度を有する。ゲート電極51は、第1および第2低濃度領域31Aおよび32Aの全部を覆うように形成されている。

(もっと読む)

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

半導体装置

【課題】高周波動作向けの半導体装置を高性能化させる。

【解決手段】シリコン基板S1上に形成された抵抗素子TDR1および不揮発性メモリNVM1を有する半導体装置であって、不揮発性メモリNVM1は、シリコン基板S1上に埋め込み酸化層BOX1を介して配置されたシリコン層SOI1に形成されている。特に、抵抗素子TDR1と不揮発性メモリNVM1とは互いに電気的に接続され、不揮発性メモリNVM1のオン状態またはオフ状態により、抵抗素子TDR1の導通状態または非導通状態が切り替わる。

(もっと読む)

薄膜回路構造及びその製造方法並びに有機EL装置

【課題】回路構造のスペースを小さくして画素の微細化を達成できる、薄膜回路構造及びその製造方法を提供する。

【解決手段】基材1上の面内方向Xに、ゲート電極2、ゲート絶縁膜3、酸化物半導体膜4、ソース電極5s及びドレイン電極5dで少なくとも構成された隣り合う2以上の薄膜トランジスタ10A,10Bを有する薄膜回路装置12であって、前記2以上の薄膜トランジスタ10A,10Bは、共通するゲート絶縁膜3を有するとともに、ゲート絶縁膜3の下に第1の酸化物半導体膜4Aが設けられた第1の薄膜トランジスタ10Aと、ゲート絶縁膜3の上に第2の酸化物半導体膜Aが設けられた第2の薄膜トランジスタ10Bとを有するようにして、上記課題を解決した。

(もっと読む)

表示装置の作製方法

【課題】液滴吐出法により吐出する液滴の着弾精度を飛躍的に向上させ、微細でかつ精度の高いパターンを基板上に直接形成することを可能にする。もって、基板の大型化に対応できる配線、導電層及び表示装置の作製方法を提供することを課題とする。また、スループットや材料の利用効率を向上させた配線、導電層及び表示装置の作製方法を提供することを課題とする。

【解決手段】液滴吐出法による液滴の吐出直前に、所望のパターンに従い基板表面上の液滴着弾位置に荷電ビームを走査し、そのすぐ後に該荷電ビームと逆符号の電荷を液滴に帯電させて吐出することによって、液滴の着弾位置の制御性を格段に向上させる。

(もっと読む)

半導体装置、三次元集積回路およびその製造方法

【課題】回路動作時の基板での損失を低減し、表面および裏面の両面において多層配線を形成することで配線の自由度を向上させ、なおかつ貫通配線の配線長を短縮して信号の伝達を高速化する。

【解決手段】薄膜半導体素子2はSOIウェーハを用いて形成し、そのシリコン基板から取り外されているため、素子厚さは埋め込み酸化膜を含めても、例えば2μm以下である。また、貫通配線6は、装置の表面と裏面を貫通するのではなく、薄膜半導体素子に隣接して、コンタクトビア形成時に一括で形成するため、その直径が薄膜半導体素子のコンタクトビアと同程度で、長さが薄膜半導体素子の厚さと同程度である。

(もっと読む)

平板表示装置及びその製造方法

【課題】薄膜トランジスタ及びMOS(Metal−Oxide−Semiconductor)構造のキャパシタを備える平板表示装置及びその製造方法を提供する。

【解決手段】第1領域の基板上に半導体で形成された活性層と、第2領域の基板上に半導体で形成された下部電極と、活性層及び下部電極を含む上部に形成された第1絶縁層と、活性層上の第1絶縁層上に第1導電層及び第2導電層で形成されたゲート電極と、下部電極上の第1絶縁層上に第1導電層で形成された上部電極と、ゲート電極及び上部電極を含む上部に形成され、活性層及び上部電極が露出するようにパターニングされた第2絶縁層と、露出した活性層に接続されるソース電極及びドレイン電極とを備える。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置およびその作製方法

【課題】特性の良い光電変換素子を有する半導体装置を提供することを目的の一とする。または、簡単な工程で、特性の良い光センサ光電変換装置を有する半導体装置を提供することを目的の一とする。

【解決手段】光透過性を有する基板と、光透過性を有する基板上の絶縁層と、絶縁層上の、光電変換を奏する半導体領域、第1の導電型を示す半導体領域、および、第2の導電型を示す半導体領域を有する単結晶半導体層と、第1の導電型を示す半導体領域と電気的に接続された第1の電極と、第2の導電型を示す半導体領域と電気的に接続された第2の電極とを有する光電変換素子とを備える半導体装置を提供する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、および、SOI基板の作製方法

【課題】良好な平坦性を有する半導体基板の再生に適した方法を提供することを課題の一つとし、良好な平坦性を有する半導体基板の再生に適した方法を用いて再生半導体基板を作製することを課題の一つとし、当該再生半導体基板を用いてSOI基板を作製することを課題の一つとする。

【解決手段】イオンの照射等により損傷した半導体領域を選択的に除去することが可能な方法を用いて半導体基板の凸部を除去し、さらに、CMP法をはじめとする研磨処理によって、半導体基板の平坦化を行う際に、半導体基板表面に酸化膜を形成することにより、半導体基板の研磨レートを均一にして、一様に研磨処理を行う。または、上記方法を用いて再生半導体基板を作製し、当該再生半導体基板を用いてSOI基板を作製する。

(もっと読む)

半導体装置

【課題】4個の島状半導体を用いてSRAMを構成することにより、高集積なSGTを用いたSRAMからなる半導体装置を提供することを目的とする。

【解決手段】第1の島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲む第1のゲート電極と、第1のゲート電極の周囲を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲を取り囲む第1の筒状半導体層と、第1の島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、第1の島状半導体層の下部に配置された第2の第1導電型高濃度半導体層と、第1の筒状半導体層の上部に配置された第1の第2導電型高濃度半導体層と、第1の筒状半導体層の下部に配置された第2の第2導電型高濃度半導体層と、を有するインバータを用いたSRAMにより、上記課題を解決する。

(もっと読む)

41 - 60 / 345

[ Back to top ]