Fターム[5F048BD07]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | 電流方向 (824) | 垂直チャネル (460)

Fターム[5F048BD07]に分類される特許

1 - 20 / 460

半導体装置の製造方法

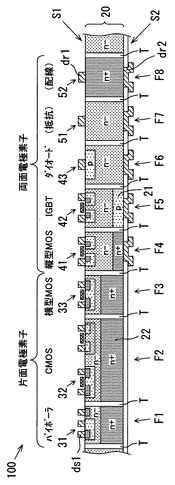

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

CMOS垂直置換ゲート(VRG)トランジスタ

【課題】本発明は、CMOS垂直置換ゲート(VRG)トランジスタを提供する。

【解決手段】集積回路構造は平面に沿って形成された主表面を有する半導体領域及び表面中に形成された第1及び第2のソース/ドレインドープ領域を含む。絶縁トレンチが第1及び第2のソース/ドレイン領域間に形成される。第1のソース/ドレイン領域とは異なる伝導形のチャネルを形成する第3のドープ領域が、第1のソース/ドレイン領域上に配置される。第4のドープ領域が第2のソース/ドレイン領域上に形成され、第2のソース/ドレイン領域とは相対する伝導形をもち、チャネル領域を形成する。第5及び第6のソース/ドレイン領域が、それぞれ第3及び第4のドープ領域上に形成される。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

半導体装置

【課題】IGBT終端部でのリカバリ破壊を防ぎ、ダイオードのスナップバックを抑制することができる半導体装置を提供する。

【解決手段】N−型のドリフト層30の上に形成されたP型のチャネル層31を含む半導体基板32のうちチャネル層31側の一面33とは反対側の他面34側に、P++型のコレクタ層53とN++型のカソード層54とが同じ階層に形成されている。そして、P++型のコレクタ層53がトレンチ35の延設方向における表面IGBT専用領域10および表面ダイオード専用領域20の周辺部25にそれぞれ設けられていることによりN++型のカソード層54は四角形状にレイアウトされている。また、P++型のコレクタ層53がエミッタ領域39の終端部39aから距離aを半径とする円形状に設けられていることにより当該四角形状の角部が窪んだ形状にレイアウトされている。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

半導体装置

【課題】オフリーク電流の抑制および駆動電流の増大を図ることが可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置において、ゲート電極は、第1および第2のソース・ドレイン領域の間に設けられた第1リセス内に少なくとも一部がゲート絶縁膜を介して埋め込まれて第1および第2のソース・ドレイン領域よりも深い位置まで形成される。チャネルは、素子領域においてゲート絶縁膜に隣接して第1および第2のソース・ドレイン領域の間に形成される。一対の応力付与部は、素子分離領域において、ゲート電極のゲート幅方向に垂直な面内において第1および第2のソース・ドレイン領域の下部のチャネルと重複する領域に設けられ、素子分離領域の構成材料と異なる絶縁材料からなりチャネルに対してゲート幅方向の両側から応力を付与する。

(もっと読む)

半導体装置

【課題】抵抗値が制御されることができる抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、絶縁膜14bと、半導体素子と、抵抗素子4tとを有する。絶縁膜14bは半導体基板101の少なくとも一部を被覆している。半導体素子は、半導体基板101の一部からなるチャネル領域と、電極とを有する。抵抗素子4tは、電極を流れる電流に対する抵抗となるように電極と電気的に接続され、かつ絶縁膜14bを介して半導体基板101上に設けられている。抵抗素子4tは半導体領域を含む。半導体基板101と抵抗素子4tとの間の電位差により半導体領域に空乏層が生じる。

(もっと読む)

半導体装置

【課題】高集積なCMOS SRAMを提供する。

【解決手段】第1の第1導電型半導体137と、第1の第1導電型半導体とは極性が異なる第1の第2導電型半導体104と、第1の第1導電型半導体と第1の第2導電型半導体との間に配置される第1の絶縁物112が一体となり基板に対して垂直に延びる1本の第1の柱と、

第1の第1導電型半導体の上に配置される第1の第2導電型高濃度半導体182と、第1の第1導電型半導体の下に配置される第2の第2導電型高濃度半導体141と、第1の第2導電型半導体の上に配置される第1の第1導電型高濃度半導体186と、第1の第2導電型半導体の下に配置される第2の第1導電型高濃度半導体143と、第1の柱を取り囲む第1のゲート絶縁物176と、第1のゲート絶縁物を取り囲む第1のゲート導電体167と、を有するインバータ501を用いてSRAMを構成する。

(もっと読む)

ダイオード、半導体装置およびMOSFET

【課題】 発熱による半導体基板の温度上昇の影響を受けにくい構造で、ダイオードにおけるスイッチング損失の低減を実現することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、アノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域を備えている。そのダイオードでは、前記バリア領域が、外部の整流素子を介して、前記アノード電極と電気的に接続している。そのダイオードでは、前記整流素子の順方向電圧降下が、前記アノード領域と前記バリア領域の間のpn接合のビルトイン電圧よりも小さい。

(もっと読む)

ダイオード、半導体装置およびMOSFET

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を開示する。

【解決手段】 本明細書で開示するダイオードは、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、金属からなるアノード電極を備えている。そのダイオードは、前記ドリフト領域と前記アノード領域の間に形成された、前記ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、前記バリア領域と前記アノード電極を接続するように形成された、前記バリア領域よりも濃度が高い第1導電型の半導体からなるピラー領域を備えている。そのダイオードでは、前記ピラー領域と前記アノード電極がショットキー接合している。

(もっと読む)

半導体装置

【課題】トンネル型FETのオン電流とオフ電流との比と、単位基板面積あたりのオン電流を増大させる。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に絶縁膜を介して形成されたゲート電極と、前記ゲート電極の側面に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記半導体基板上に順に積層された第1導電型の下部主端子層と、中間層と、第2導電型の上部主端子層とを有し、前記ゲート絶縁膜を介して前記ゲート電極の側面に形成された積層体とを備える。さらに、前記上部主端子層は、前記ゲート電極の側面に、前記ゲート絶縁膜と半導体層を介して形成されている。

(もっと読む)

トレンチポリシリコンダイオード

【課題】シリコン内にダイオード構造を位置させた半導体製造方法を提供する。

【解決手段】トレンチポリシリコンダイオードを製造する方法は、N+(P+)型基板上にN−(P−)型エピタキシャル領域を形成すること、エピタキシャル領域内にトレンチを形成すること、さらに、前記トレンチ内に絶縁層を形成し、前記トレンチをポリシリコンで充填する。さらに、P+(N+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのP+(N+)型領域を、N+(P+)型ドーパントをインプラントして、前記トレンチ内に前記ポリシリコンのN+(P+)型領域を形成しトレンチ内にポリシリコンダイオードを形成することを含み、ダイオードの一部は、トレンチの上面より低い。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

ダイオードおよび半導体装置

【課題】 ダイオードにおけるスイッチング時の損失を低減することが可能な技術を提供する。

【解決手段】 本明細書は、カソード電極と、第1導電型の半導体からなるカソード領域と、低濃度の第1導電型の半導体からなるドリフト領域と、第2導電型の半導体からなるアノード領域と、アノード電極を備えるダイオードを開示する。そのダイオードは、ドリフト領域とアノード領域の間に形成された、ドリフト領域よりも濃度が高い第1導電型の半導体からなるバリア領域と、アノード電極と接触するように形成された、第1導電型の半導体からなるコンタクト領域と、コンタクト領域とバリア領域の間のアノード領域に対して絶縁膜を挟んで対向する制御電極を備えている。そのダイオードでは、制御電極に電圧が印加されると、コンタクト領域とバリア領域の間のアノード領域に第1導電型のチャネルが形成される。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁ゲート型電界効果トランジスタの導通時および還流ダイオードの導通時のいずれにおいても良好なオン電圧を得ることのできる半導体装置およびその製造方法を提供する。

【解決手段】IGBTのp型コレクタ領域9と還流ダイオードのn型カソード領域10は、半導体基板20の第2主面20bに交互に形成されている。裏面電極14は、p型コレクタ領域9およびn型カソード領域10との双方に接するように第2主面20b上に形成され、かつ第2主面20b側から順に積層されたチタン層11、ニッケル層12および金層13を有している。チタン層11はp型コレクタ領域9およびn型カソード領域10の双方にオーミック接触している。

(もっと読む)

1 - 20 / 460

[ Back to top ]