Fターム[5F048BD09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | チャネル領域をエピ成長によって別個に形成 (376)

Fターム[5F048BD09]に分類される特許

61 - 80 / 376

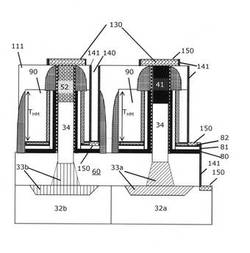

垂直TFETの製造方法

【課題】ヘテロ構造ナノワイアを有するトンネル電界効果トランジスタと集積されたナノワイアを有する相補型トンネル電界効果トランジスタの製造方法を提供する。

【解決手段】犠牲材料21の層を有するチャネル材料34の層を含むスタック24を形成する工程と、チャネル材料34の層と犠牲材料21の層から、少なくとも1つのナノワイヤ30を形成するために、スタック24から材料を除去する工程と、第1ドーパント型の少なくとも1つのナノワイヤ30中の犠牲材料21を第1ドーパント型のヘテロ接合材料41で置き換えて、その後に、第2ドーパント型の少なくとも1つのナノワイア中の犠牲材料を、第2ドーパント材料のヘテロ接合材料52で置き換える工程を含み、相補型TFETの容易な製造が可能となる。

(もっと読む)

シリコン・オン・インシュレータ構造において電界効果トランジスタを備える半導体デバイス

【課題】シリコン・オン・インシュレータ構造において複数電界効果トランジスタを備える新規な半導体デバイスを提供する。

【解決手段】基板200と、基板上の酸化物層190と、酸化物層上の半導体層230を備えるSOI構造の電解効果トランジスタと、半導体・オン・インシュレータ構造(SeOI構造)のFETであって、基板内にチャンネル領域200を備え、前記FET構造のBOX構造酸化物層190の少なくとも一部である誘電体をゲート誘電体とし、基板200をチヤネルとする半導体デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エッチング量を少なくしても素子分離膜の周辺にHigh−kゲート絶縁膜材料やゲート電極材料が残ることを抑制できるようにする。

【解決手段】素子分離膜102はSTI構造を有しており、基板101に埋め込まれており、かつトランジスタが形成される素子形成領域を分離している。素子分離膜102の側面の上端は、トランジスタのチャネル形成層よりも上に位置しており、かつチャネル形成層の表面から素子分離膜102の側面の最上部までの高さhが35nm以下である。また素子分離膜102のうちチャネル形成層よりも上に位置している部分の側面は、基板の表面に対する角度θが80度以下である。

(もっと読む)

フィン型電界効果トランジスタおよびその製造方法

【課題】フィン型電界効果トランジスタおよびその製造方法を提供する。

【解決手段】半導体基板より上に延伸したfinFETの第1および第2のフィン206を、その間にシャロートレンチアイソレーション(STI)領域202、およびSTI領域の上面と第1および第2のフィンの上面との間の距離を有して、形成するステップ、STI領域の上面より上の第1および第2のフィンの上面および側面に第1および第2のフィン延伸部を提供するステップ、STI領域から材料を除去し、STI領域の上面と第1および第2のフィンの上面との間の距離を増加させるステップ、フィンおよびSTI領域上に共形のストレッサ誘電材料214を堆積するステップ、および共形のストレッサ誘電材料をSTI領域の上面より上の第1および第2のフィンの間の空間内に流入するようにリフローし、finFETのチャネルに応力を加えるステップを含む方法。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値電圧が低く、かつ、ゲート絶縁膜のリーク電流を抑制可能な半導体装置およびその製造方法を提供する。

【解決手段】メタルゲート電極103,203の材料として、Ta3N5を含むTaxNy膜18,38を用いる。TaxNy膜18,38中には多くの窒素が含まれており、その窒素の一部がゲート絶縁膜102,202中に拡散することにより、TiNに比べてフラットバンド電圧Vfbが高くなり、NMOSFET100およびPMOSFET200の閾値電圧Vthを低くすることができる。また、TaxNy膜18,38中の窒素がHfSiON膜17,37中に拡散することにより、ゲート絶縁膜の絶縁性を高くすることができ、ゲートリーク電流Jgを抑制できる。

(もっと読む)

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

トランジスタ及びその製造方法

【課題】Siチヤネルを有するNMOSとSiGeチャネルを有するPMOSで、NMOSには引張り歪みを与える、PMOSには、表面のダングリングボンドを減少させることができる半導体装置を提供する。

【解決手段】単結晶シリコン基板50の一部領域にシリコンゲルマニウムチャネル膜54aを形成し、PMOSトランジスタを、シリコン膜60aを形成し、NMOSトランジスタを形成する。単結晶シリコン基板、シリコンゲルマニウムチャネル膜、PMOSトランジスタ、NMOSトランジスタの表面上に、反応ガス、雰囲気ガス及び水素ガスを含む蒸着ガスを用いて、シリコン窒化膜82を形成し、PMOSトランジスタは、シリコンゲルマニウムチャネル膜表面のダングリングボンドの除去により、ホールスキャタリングが抑制され、NMOSトランジスタには引張り歪みを与えることにより動作特性の改善ができる。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。様々な効果を達成するようDDCを構成する手法が数多く存在し得るとともに、ここに提示される更なる構造及び方法は、更なる利益を生み出すように単独あるいはDDCとともに使用され得る。  (もっと読む)

(もっと読む)

状態密度が設計された電界効果トランジスタ

【課題】nチャネルおよびp型チャネルトランジスタに用いられる層構造を提供する。

【解決手段】nチャネルトランジスタを製作するのに用いる層構造を含む。層構造は、伝導帯底EC1を有する第1の半導体層、離散正孔準位H0を有する第2の半導体層、第1と第2の半導体層との間に配置された広バンドギャップ半導体バリア層、第1の半導体層の上方に配置されたゲート誘電体層、およびゲート誘電体層の上方に配置されたゲート金属層を含み、離散正孔準位H0は、伝導帯底EC1の下方に位置され、ゲート金属層にゼロバイアスが供給される。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタ

【課題】伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタを提供する。

【解決手段】本発明は、単一端子トランジスタ装置に関する。一具体例において、nチャネルトランジスタは、離散正孔準位H0を有する第一半導体層と、伝導帯底EC2を有する第二半導体層と、第一半導体層と第二半導体層の間に配置される広バンドギャップ半導体バリア層と、第一半導体層の上方のゲート誘電層と、ゲート誘電層の上方にあり、ゼロバイアスを加え、n端子特徴を得るために、離散正孔準位H0が伝導帯底Ec2の下方に位置するように選択された有効仕事関数を有するゲート金属層と、からなる。

(もっと読む)

二種類の仕事関数メタルを備える半導体装置

【課題】高誘電率ゲート絶縁膜を備える半導体装置の閾値電圧を適切に制御すること。

【解決手段】半導体装置の形成方法は、仕事関数メタルを含むダミーメタルゲート層をベース絶縁膜の直上に形成することと、アニーリングによって仕事関数メタルをベース絶縁膜中に拡散させることと、ウェットエッチングによってダミーメタルゲート層を除去することと、ベース絶縁膜211、212上に高誘電率ゲート絶縁膜213、213を形成することと、高誘電率ゲート絶縁膜213上にメタルゲート214、215を形成することと、を含む。

(もっと読む)

集積回路およびその形成方法

【課題】製造コストを良好に減少できる集積回路およびその形成方法を提供する。

【解決手段】集積回路は、第1のメモリアレイ、および第1のメモリアレイに接続された論理回路を含み、第1のメモリアレイの全てのメモリセルの全ての活性トランジスタおよび論理回路の全ての活性トランジスタは、フィン電界効果トランジスタ(FinFET)であり、第1の縦方向に沿って配置されたゲート電極を有する。FinFETs300a〜300cは、基板301上に配置され得る。基板301は、複数の活性領域305a〜305cを含み得る。活性領域305a〜305cは、基板301の表面301a上の非平面活性領域であり得る。

(もっと読む)

半導体装置及びその製造方法

【課題】側面に(110)面が形成されたGe若しくはSiGeのフィン構造を実現することができ、FinFET等の素子特性の向上に寄与する。

【解決手段】Ge若しくはSiGeのフィン構造部を有する半導体装置であって、Si基板10の表面部に、一方向に長いストライプ領域を挟むように埋め込み形成され且つ基板表面よりも高い位置まで形成された素子分離絶縁膜12と、ストライプ領域上に形成され、且つ最上面が前記素子分離絶縁膜の最上面よりも低い位置にあるSiGeバッファ層14と、バッファ層14上に形成され、該層14よりも一方向と直交する方向の幅が狭く基板面と垂直な(110)面を有するGeフィン構造16と、を備えた。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

最適化されたチャンネル領域を有するMOSトランジスタを具備する半導体素子

【課題】 MOSトランジスタを備える半導体素子を提供する。

【解決手段】 半導体素子は、半導体基板の所定領域に形成されて活性領域を区画する素子分離膜を有する。第1活性領域9a及び第2活性領域9bは(100)面の中心上面9t及び中心上面9tから素子分離膜14に向けて延びる傾斜エッジ面9eを有する。第1活性領域9a及び第2活性領域9bの中心上面9t及び傾斜エッジ面9eは第1半導体パターン15a及び第2半導体パターン15bで覆われる。第1半導体パターン15a及び第2半導体パターン15bは中心上面9tに平行な(100)面の平坦な上面15t及び平坦な上面に実質的に垂直な側壁15sを有する。第1半導体パターン15a及び第2半導体パターン15bの上部を通って側壁に交差する方向に第1ゲートパターン26a及び第2ゲートパターン26bが配置される。

(もっと読む)

CMOS用歪トランジスタの集積化

【課題】n型MOSデバイス(NMOS)の電子の移動度の向上、およびp型MOSデバイス(PMOS)のホールの移動度の向上した半導体装置および製造方法の提供。

【解決手段】(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】Geを含む半導体で構成されるチャネル領域を有するP型FETにおいて、逆短チャネル特性の発生を抑制しつつ、短チャネル特性を改善する。

【解決手段】半導体装置は、半導体基板100上に形成されたP型FETを備えている。P型FETは、半導体基板100上に形成され、Geを含有する第1の半導体層103と、第1の半導体層103上に形成され、第1の半導体層103よりも低濃度のGeを含有する第2の半導体層104と、第2の半導体層104上にゲート絶縁膜107aを間に挟んで形成されたゲート電極110aと、第2の半導体層104のうちゲート電極110aの両側方に位置する部分に形成されたp型エクステンション領域111aと、第1の半導体層103内に設けられ、且つp型エクステンション領域111aの下に形成されたn型不純物領域152とを有している。

(もっと読む)

61 - 80 / 376

[ Back to top ]