Fターム[5F048BD09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | チャネル領域をエピ成長によって別個に形成 (376)

Fターム[5F048BD09]に分類される特許

101 - 120 / 376

半導体装置およびその製造方法

【課題】 厚さが異なるゲート電極を含む、互いにチャネルタイプの異なるMISFETの対を形成する際におけるリソグラフィのプロセスマージンの低下を抑制できる半導体装置を提供すること。

【解決手段】 半導体装置は、第1の主面を有する半導体領域を含む第1の領域Pと、第2の主面を有する半導体領域を含む第2の領域Nとを備え、前記第1の主面が前記第2の主面よりも低い、半導体基板100と、第1の領域P内に設けられ、第1のゲート電極108,109を含む第1導電型MISFETと、第2の領域N内に設けられ、第2のゲート電極109を含む第2導電型MISFETであって、第2のゲート電極109の上面と第1のゲート電極108,109の上面とが同じ高さになるように、第2のゲート電極109の厚さは第1のゲート電極108,109の厚さよりも薄くなっている前記第2導電型MISFETとを具備してなることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デバイス特性の制御性に優れた半導体装置および半導体装置の製造方法を提供する。

【解決手段】本実施の形態の半導体装置は、シリコン基板101上にMOSトランジスタを備える半導体装置であって、MOSトランジスタは、シリコン基板101上にゲート絶縁膜203を介して設けられたゲート電極(メタル電極206)と、ゲート電極(メタル電極206)の両脇の前記シリコン基板の表面近傍に設けられソース領域106およびドレイン領域109と、ソース領域106およびドレイン領域109に接するように、ゲート電極直下のシリコン基板101中に設けられた、チャネル領域(ゲルマニウム・カーボン単結晶膜202)と、を備え、チャネル領域が、シリコンと異なる異種半導体(ゲルマニウム)を含むものである。

(もっと読む)

保護用ダイオードを備えるトレンチゲート形パワーMOSFET

【課題】トレンチ底部におけるブレークダウンの発生を防ぎ、MOSFETの損傷を避けると共に、オン抵抗特性が改善されたトレンチゲート形MOSFETを提供する。

【解決手段】パワーMOSFETは複数のMOSFETセルを画定するトレンチゲートを備える。各MOSFET内のチャネル領域に並列に接続されるダイオードを形成するように、保護拡散部が、好ましくは非アクティブセル内に生成される。保護拡散部は衝撃イオン化及びその結果生じるゲートトレンチの角部付近におけるキャリアの発生を防ぎ、ゲート酸化物層の損傷を防ぐ。さらに、ダイオードはブレークダウン電圧を有するように設計され、ブレークダウン電圧がゲート酸化物層を横切る電界の強さを制限することができる。深い中央拡散部を削除することによりセル密度が増加し、かつMOSFETのオン抵抗を改善することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体装置及びその製造方法

【課題】過電圧に伴う破壊を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の一態様には、互いに並列に接続され、ゲート電極10、ソース電極9及びドレイン電極15を備えた複数の縦型トランジスタ32と、前記複数の縦型トランジスタ32を個別に取り囲むダイオード31と、が設けられている。前記ソース電極9に前記ダイオード31のアノード11が接続され、前記ドレイン電極15に前記ダイオードのカソード1が接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極7作製後にチャネル部12を作製する縦型MISFETの製造方法において、ゲート絶縁膜10に損傷を与えたり移動度を劣化させたりすることなく、孔底面に形成された絶縁膜や、自然酸化膜を除去する。

【解決手段】単結晶半導体基板1または単結晶半導体層に形成された不純物領域8の上に、第一絶縁層4、5と、ゲート電極層7と、第二絶縁層5、4と、をこの順に積層した積層体を形成し、前記積層体に不純物領域8が露出する孔を形成し、少なくとも前記孔の側壁に露出しているゲート電極層7、および、前記孔の底面に露出している不純物領域8の上に絶縁膜10を形成し、ゲート電極層7の露出部分の上に形成された絶縁膜10の上に半導体膜を重ねて形成し、不純物領域8の上に形成された絶縁膜を除去し、孔の底面に露出している不純物領域8に接し、孔底面から孔の開口部までつながる半導体部を形成する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタ特性を向上させる。

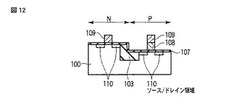

【解決手段】STI109と、STI109によって互いに分離されたp型ウェル102及びn型ウェル103と、p型ウェル102及びn型ウェル103上に形成されたSiGe膜108とを有するSi基板101を用意する工程と、n型ウェル103上に位置するSiGe膜108をSiO2膜116で被覆する工程と、SiO2膜116をマスクとして酸化処理を行うことによりp型ウェル102上に形成されたSiGe膜108を酸化し、SixGeyOz膜117を形成する工程((c))と、SixGeyOz膜117を除去する工程((d))と、を行い、半導体装置を製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】簡易な手順で、高誘電率ゲート絶縁膜とメタルゲート電極とのゲートスタック構造を有する相補型トランジスタの閾値を調整する。

【解決手段】相補型トランジスタの第1導電型のトランジスタ(162)の閾値電圧を変化させる第1の調整用金属を第1導電型のトランジスタ(162)および第2導電型のトランジスタ(160)に同時に添加し、第2導電型のトランジスタ(160)のメタルゲート電極(110a)上から第1の調整用金属の拡散を抑制する拡散抑制元素を添加する。

(もっと読む)

電界効果トランジスタ(FET)インバータとその製造方法(単一ゲート・インバータのナノワイヤ・メッシュ)

【課題】単一ゲート・インバータのナノワイヤ・メッシュ及びその製造方法を提供する。

【解決手段】電界効果トランジスタ(FET)インバータは、スタック内で垂直方向に配置された複数のデバイス層を含み、各デバイス層は、ソース領域、ドレイン領域、及びソース領域とドレイン領域を接続する複数のナノワイヤ・チャネル110を有し、ここで1つ又は複数のデバイス層のソース及びドレイン領域はn型ドーパント、又はp型ドーパントでドープされる。FETインバータはさらに、複数のナノワイヤ・チャネルを取り囲む共通のゲート150と、n型ドーパントでドープされた1つ又は複数のデバイス層のソース領域への第1のコンタクト156と、p型ドーパントでドープされた1つ又は複数のデバイス層のソース領域への第2のコンタクト158と、デバイス層の各々のドレイン領域への共通の第3のコンタクト152とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

ハイブリッド半導体基板の製造プロセス

【課題】ハイブリッド半導体基板及びその製造方法を提供する。

【解決手段】本発明は、(a)ベース基板3の上の絶縁層5と絶縁層の上のSeOI層7とを備えるセミコンダクタ−オン−インシュレータ(SeOI)領域13と、バルク半導体領域11とを具備するハイブリッド半導体基板1を提供するステップであって、SeOI領域とバルク半導体領域とは同じベース基板を共用するステップと、(b)SeOI領域の上にマスク層9を提供するステップと、(c)SeOI領域とバルク半導体領域を同時にドーピングすることにより、第1の不純物レベルを形成するステップであって、このドーピングは、SeOI領域の第1の不純物レベルがマスク内に含まれるように実行されるステップとを含む方法に関する。それによって、ハイブリッド半導体基板の製造プロセスに、より多くのプロセスステップが含まれることを防ぐ。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置全体としてみたとき、微細化によるチップ面積の減少を図りつつ、各素子に必要とされる特性を維持・向上させる。

【解決手段】半導体装置は、FinFET10と、FinFET10と同一のチップ上に設けられたPlanarFET20とを具備する。PlanarFETの第2ゲート絶縁層24は、FinFET10の第1ゲート絶縁層14よりも厚い。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

SOI基板の作製方法

【課題】結晶性に優れた結晶質半導体層を有するSOI基板を提供する。

【解決手段】支持基板上に、バッファ層を介して単結晶半導体基板から分離させた単結晶半導体を部分的に形成する。単結晶半導体基板は、加速されたイオンの照射とそれに伴う脆化層の形成、及び熱処理により、単結晶半導体を分離する。単結晶半導体上に非単結晶半導体層を形成し、レーザビームを照射することにより、非単結晶半導体層を結晶化させて、SOI基板を作製する。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置が有する集積回路の多機能化を図ること、又は、炭化シリコン基板を用いて集積回路を形成する場合であっても集積回路の大面積化を図ることを目的とする。

【解決手段】基板上に第1の絶縁層を介して設けられた島状の炭化シリコン層と、炭化シリコン層上に設けられた第1のゲート絶縁層と、第1のゲート絶縁層上に設けられ且つ炭化シリコン層と重畳する第1の導電層とを有する第1のトランジスタと、基板上に第2の絶縁層を介して設けられた島状の単結晶シリコン層と、単結晶シリコン層上に設けられた第2のゲート絶縁層と、第2のゲート絶縁層上に設けられ且つ単結晶シリコン層と重畳する第2の導電層とを有する第2のトランジスタを設ける。

(もっと読む)

半導体デバイス及びその製造方法

【課題】絶縁層を介して基板同士を貼り合わせることで、一方の基板上に形成された半導体層を他方の基板に形成できると共に、半導体層の結晶構造を損傷させることなく高品質に維持できる半導体デバイス及びその製造方法を提案する。

【解決手段】ECRプラズマを用いてIII−V族化合物半導体層7及びSi基板4上に酸化膜6a,6bを形成するようにしたことで、当該III−V族化合物半導体層7及び酸化膜6a,6bへのダメージが低減され、酸化膜6a,6bを平坦に形成できると共に、III−V族化合物半導体層7の結晶構造も損傷させることなく高品質に維持できる。これにより酸化膜6a,6bを介しSi基板4及びInP基板12同士を貼り合わせることで、一方のInP基板12上に形成されたIII−V族化合物半導体層7を他方のSi基板4に形成できると共に、III−V族化合物半導体層7の結晶構造を損傷させることなく高品質に維持できた半導体デバイス1を提案できる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

101 - 120 / 376

[ Back to top ]