Fターム[5F048BD09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | チャネル (4,415) | チャネル領域をエピ成長によって別個に形成 (376)

Fターム[5F048BD09]に分類される特許

121 - 140 / 376

ソース/ドレイン延長部又は/及びハローポケットと組み合わせて空のウエルを使用した電界効果トランジスタの構成及び製造

【課題】 混合信号適用例を含むアナログ及びデジタル適用例用のIGFETを与える半導体製造プラットフォームに適した対称的及び非対称的の両方の絶縁ゲート電界効果トランジスタ(「IGFET」)が、高性能を達成する上で空のウエル領域を使用する。

【解決手段】 各空のウエルの上部近くにおいては半導体ウエルドーパントが比較的少量である。各IGFET(100,102,112,114,124又は236)は、空のウエル(180,182,192,194,204又は206)のボディ物質のチャンネルゾーンによって横方向に分離された一対のソース/ドレインゾーンを有している。ゲート電極が該チャンネルゾーン上方でゲート誘電体層の上側に位置している。各ソース/ドレインゾーン(240,242,280,282,520,522,550,552,720.722、752又は752)が主要部分(240M,242M,280M,282M,520M,522M,550M,552M,720M,722M,752M又は752M)及び一層軽度にドープした横方向延長部(240E,242E,280E,282E,520E,522E,550E,552E,720E,722E,752E又は752E)を有している。代替的に又は付加的に、該ボディ物質の一層高度にドープしたポケット部分(250又は290)が該ソース/ドレインゾーンの内の一方に沿って延在する。存在する場合には、該ポケット部分は典型的に該IGFETを非対称的装置とさせる。

(もっと読む)

半導体素子及び半導体装置

【課題】高い電流駆動力を有するn型半導体素子を提供する。

【解決手段】第1の主面を有し、III族の不純物を含み、1.2<N<10を満たすNを用いて(11N)面と表される、ないしはそれと結晶学的に等価な第1の面方位のみを前記第1の主面に有する、シリコンとゲルマニウムとの混晶層と、前記第1の主面上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記混晶層の[110]方向ないしそれと結晶学的に等価な方向に、前記ゲート電極を挟む様に形成され、V族の不純物を含む半導体よりなるソース・ドレイン領域と、を有し、前記混晶層は面内方向に圧縮歪みが印加されていることを特徴とする。

(もっと読む)

縦型論理素子

【課題】狭い面積で高速応答性の縦型半導体装置を提供する。

【解決手段】基板上に形成された第1の電極と、絶縁膜と、絶縁膜を介し第1の電極の側面の一方に形成された第1の導電型の第1の半導体層と、絶縁膜を介し第1の電極の側面の他方に形成された第2の導電型の第2の半導体層と、一部領域における第1の半導体層上に形成された第2の電極と、他の一部領域における第2の半導体層上に形成された第3の電極と、第1の電極の上層の第1の半導体層及び第2の半導体層上に形成された第4の電極とを有し、第2の電極と前記第4の電極間における第1の半導体層に第1のチャネル領域が形成され、第3の電極と前記第4の電極間における第2の半導体層に第2のチャネル領域が形成されるものであることを特徴とする縦型半導体装置を提供することにより上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】N型トランジスタ、P型トランジスタともに低い閾値電圧が得られる半導体装置及びその製造方法を提供する。

【解決手段】基板上の第1領域201にN型トランジスタが形成され、前記基板上の第2領域202にP型トランジスタが形成された半導体装置101であって、前記基板111と、シリコンを含有する第1のゲート絶縁膜121と、第1の金属と酸素とを含有する第2のゲート絶縁膜122と、前記第1の金属と異なる第2の金属と酸素とを含有する第3のゲート絶縁膜123と、ハフニウムを含有する第4のゲート絶縁膜124と、金属と窒素とを含有するゲート電極層131とを備え、前記第2領域に形成された前記ゲート電極層の厚さは、前記第1領域に形成された前記ゲート電極層の厚さよりも厚くなっている。

(もっと読む)

半導体装置およびその製造方法

【課題】NMISFETにおいて、最も高移動度化可能である(111)面をチャネル面に持ち、同時に、<110>方向を電流方向に持つ半導体装置およびその製造方法を提供すること。

【解決手段】チャネル電流が流れる方向に対して垂直方向の断面が三角形状をしており、その2面が(111)面で、残りの1面が(100)面であるGOI層6またはGe層8と、前記(100)面上に形成されたSi層7と、を備えたNMISFET領域3を備えたこと、を特徴とする半導体装置1。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域のエクステンション領域の不純物濃度プロファイルが急峻なp型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、半導体基板2上に形成された結晶層13と、結晶層13上にゲート絶縁膜14を介して形成されたゲート電極15と、半導体基板2と結晶層13との間に形成された、ゲート電極15の下方の領域において第1の不純物を含むC含有Si系結晶からなる不純物拡散抑制層12と、半導体基板2、不純物拡散抑制層12、および結晶層13内のゲート電極15の両側に形成され、結晶層13内にエクステンション領域を有する、p導電型を有する第2の不純物を含むp型ソース・ドレイン領域17と、を有し、C含有Si系結晶は第2の不純物の拡散を抑制する機能を有し、第1の不純物は、C含有Si系結晶内の固定電荷の発生を抑制する機能を有する。

(もっと読む)

スレッショルド調節半導体合金を堆積させるのに先立ちパターニング不均一性を低減することによる前記半導体合金の厚みばらつきの低減

【解決手段】

シリコン/ゲルマニウム合金のようなスレッショルド調節半導体合金を堆積させるための選択的エピタキシャル成長プロセスにおける成長速度は、選択的エピタキシャル成長プロセスを実行するのに先立ちプラズマ支援エッチングプロセスを実行することによって、高められ得る。例えば、プラズマ支援エッチンプロセスに基いてマスク層がパターニングされてよく、それにより後続の成長プロセスの間に優れたデバイストポグラフィを同時にもたらすことができる。従って、スレッショルド調節材質を高い厚み均一性で堆積させることができ、全体的なスレッショルドばらつきを低減することができる。

(もっと読む)

SiGeチャネルを有するデュアル高K酸化物

PMOSデバイス領域112、113内にシリコンゲルマニウムチャネル層21を有する単一基板15にデュアルゲート酸化物(DGO)トランジスタデバイス50、52およびコアトランジスタデバイス51、53を集積するための方法および装置を記載する。各DGOトランジスタデバイス50、52は、金属ゲート25と、第2の相対的により高い高K金属酸化物層24から形成された上部ゲート酸化物領域60、86と、第1の相対的により低い高K誘電体層22から形成された下部ゲート酸化領域58、84とを含む。また、各コアトランジスタデバイス51、53は、金属ゲートと、第2の相対的により高い高K金属酸化物層24から形成されたコアゲート誘電層72、98とを含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】面方位が(110)面あるいはこれと等価な面であるシリコン層上に形成する酸化膜厚の制御を行うことのできる半導体装置の製造方法を提供すること。

【解決手段】面方位が(110)面あるいはこれと等価な面であるシリコン基板1表面の一部に、リンのイオン注入を行って、端部の不純物濃度が連続的に変化した第1の不純物領域2Aを形成する工程と、熱酸化を行って、シリコン基板1上に端部の厚さが連続的に変化したシリコン酸化膜3を形成する工程と、を含むこと、を特徴とする。

(もっと読む)

BiCDMOS構造及びその製造方法

【課題】DMOS電力回路、CMOSデジタル論理回路、及びコンプリメンタリバイポーラアナログ回路の全てを単一の集積化された回路チップ上に実現するBiCDMOS構造及びその製造方法を提供する。

【解決手段】基層10内に下向きに延出し、且つ基層の上に配置されたエピタキシャル層40内に上向きに延出し、かつエピタキシャル層の上側主面の下に配置された埋め込み絶縁領域21Bと、エピタキシャル層内のみに配置され、かつ埋め込み絶縁領域の上側主面から上向きに延出した埋め込みウェル領域44Bと、エピタキシャル層内に配置され、かつエピタキシャル層の上側主面からエピタキシャル層内に下向きに延出し、かつ埋め込みウェル領域の上側主面に接触する下側主面を備えたウェル領域51Bとを有し、バイポーラトランジスタがウェル領域内に形成され、MOSトランジスタがウェル領域外のエピタキシャル層の上側主面に形成される。

(もっと読む)

半導体装置の製造方法

【課題】マルチ酸化プロセスにおいて、p型MOSFETの閾値電圧を、可及的に高精度に制御可能な半導体装置の製造方法を提供する。

【解決手段】LV領域、MV領域及びHV領域にSiGe膜5をそれぞれ形成し、

LV領域、MV領域及びHV領域におけるSiGe膜5の上に第1のゲート絶縁膜6を形成し、

MV領域における第1のゲート絶縁膜6を除去し、

LV領域とHV領域における第1のゲート絶縁膜6、及びMV領域におけるSiGe膜5の上に第2のゲート絶縁膜8を形成し、

LV領域における第1のゲート絶縁膜6及び第2のゲート絶縁膜8を除去し、

LV領域におけるSiGe膜5の上にシリコン膜10を形成し、

LV領域におけるシリコン膜10、及びMV領域とHV領域とにおける第2のゲート絶縁膜8の上に、High−k膜からなる第3のゲート絶縁膜12及びメタル層13を順次形成する。

(もっと読む)

基板ドレイン接続を有する横型MOSFET

1つの形式として、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているアクティブゲートを含み、当該ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、横型MOSFETは、ドレイン領域の上に配されている非アクティブゲートをさらに含む。他の形式において、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているゲートを含み、ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、ソース領域及びドレイン領域は第1の導電タイプであって、横型MOSFETは、ソース領域に接しておりかつソース領域の下方にある第2の導電タイプのヘビーボディ領域をさらに含み、ドレイン領域は、ゲートのエッジに近接しているライトドープドレイン(LDD)領域及び単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張しているシンカーを含んでいる。  (もっと読む)

(もっと読む)

垂直置換ゲートトランジスタと集積可能な容量の構造及び作製法

【課題】垂直MOSFETデバイス及び容量に関連したプロセス及び構成を提供する。

【解決手段】半導体デバイスは半導体材料の第1の層と、第1の層中に形成された第1のソース/ドレイン領域を有する電界効果トランジスタを含む。チャネル領域は、第1の層上に形成され、第2のソース/ドレイン領域235はチャネル領域上に形成される。集積回路構造は底部プレート266、誘電体層258及び最上部容量プレート259を有する容量を更に含む。作製方法において、電界効果トランジスタのソース領域及びドレイン領域から成るグループから選択された第1のデバイス領域が、半導体層上に形成される。第1の電界効果トランジスタゲート領域265が、第1のデバイス領域上に形成される。間にはさまれた誘電体層を有する最上部及び底部層も、半導体層上に形成される。別の実施例において、容量層は半導体層中に形成された溝又は窓内に形成される。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体デバイスとその製造方法、および集積回路

【課題】 バンド端を制御されたVtオフセット・デバイスを提供する。

【解決手段】 バンド端を制御されたVtオフセット・デバイス、バンド端を制御されたVtオフセット・デバイスの設計構造体、及びその構造体の製造方法を開示する。構造体は、第1のバンド構造及び第1の型をもたらす第1の原子比の第1の化合物半導体のチャネルを有する第1のFETを含む。この構造体はさらに、第2のバンド構造及び第1の型をもたらす第2の原子比の第2の化合物半導体のチャネルを有する第2のFETを含む。第1の化合物半導体は第2の化合物半導体とは異なり、その結果、第1のFETは第2のバンド構造とは異なる第1のバンド構造を有し、第2のFETの閾値電圧とは異なる閾値電圧を生じる。

(もっと読む)

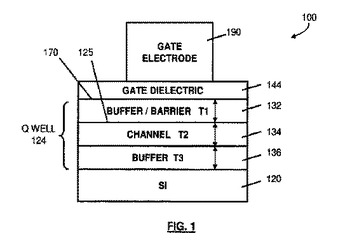

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】複数の半導体素子における界面特性及び信頼性の劣化を抑制する。

【解決手段】半導体装置の製造方法は、第1半導体素子を有する第1領域と前記第1半導体素子と異なる第2半導体素子を有する第2領域とを備えた半導体装置の製造方法であって、前記第1領域及び前記第2領域における半導体基板10表面にシリコンゲルマニウム膜11を形成する工程と、前記第1領域及び前記第2領域における前記シリコンゲルマニウム膜表面を窒化処理する工程と、前記第1領域及び前記第2領域における窒化処理された前記シリコンゲルマニウム膜上にシリコンと酸素とを主成分とする第1絶縁膜13を形成する工程と、前記第2領域における前記第1絶縁膜を除去する工程と、前記第1領域における前記第1絶縁膜上及び前記第2領域における窒化処理された前記シリコンゲルマニウム膜上に金属と酸素とを主成分とする第2絶縁膜15を形成する工程と、を具備する。

(もっと読む)

半導体製造方法と装置

【課題】部分的に絶縁膜が形成されているシリコン基板上を単結晶で覆うことができる半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】部分的に絶縁膜が形成されたSi基板10上に、a−Si膜14を成膜する(図1(b))。このSi基板10を熱処理すると、基板のSi結晶を種としてa−Siが固相Epi化される(図1(c))。基板の厚さ方向に対して充分にEpi結晶化された範囲を保護するようにレジスト膜18を形成し(図1(d))、エッチング処理を行い(図1(e))、その後、アッシング処理によってレジスト膜18を剥離し、このSi基板10上に再度a−Si膜を成膜する(図1(f))。再度、上記熱処理を行うことで、a−Siが固相Epi化される(図1(g))。

(もっと読む)

121 - 140 / 376

[ Back to top ]