Fターム[5F048BF06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 配線・電極・コンタクト (11,486) | 材料 (4,535) | シリサイド (1,808)

Fターム[5F048BF06]に分類される特許

261 - 280 / 1,808

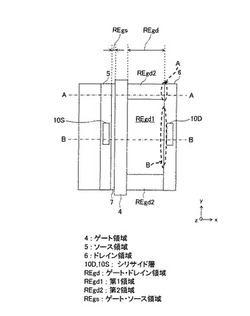

保護トランジスタおよび半導体集積回路

【課題】占有面積が小さく、所望の耐圧と熱破壊の防止を両立した保護トランジスタを提供する。

【解決手段】ゲート長方向の一方の側でゲート直下の領域に隣接しているゲート・ドレイン間領域REgdが、ゲート幅方向に互いに隣接する領域として、第1領域REgd1と第2領域REgd2とを有する。第1領域は、ドレイン耐圧が相対的に大きく、第2領域は、ドレイン電極(ドレインコンタクト部に設けられているシリサイド層10D)からの距離が平面視で第1領域より遠く、ドレイン耐圧が相対的に小さい。このため、耐圧が低いゲート・ドレイン間領域REgd2の加熱部分Aからドレインコンタクト部が遠いが、面積は小さく(または拡大しない)構造となっている。

(もっと読む)

静電気放電保護素子

【課題】耐ESD保護性能及び耐ラッチアップ性能の双方が優れ、レイアウト面積が小さい静電気放電保護素子を提供する。

【解決手段】静電気放電保護素子は、半導体基板の表面に形成され前記半導体基板の表面に垂直な方向から見て矩形である第1の第1導電型ウエルと、半導体基板の表面に第1の第1導電型ウエルを囲むように形成され第1の第1導電型ウエルにおける第1方向に直交する第2方向に延びる端縁に接し第1方向に延びる端縁には接しておらず基準電位が印加される第2の第1導電型ウエルと、を有する。前記第1の第1導電型ウエルの前記第1方向に延びる端縁と前記第2の第1導電型ウエルとの間の領域の抵抗率は、前記第1及び第2の第1導電型ウエルの抵抗率よりも高い。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】注入マスクの低減が図られる半導体装置の製造方法と、そのような半導体装置を提供する。

【解決手段】レジストマスク31と他のレジストマスクを注入マスクとして、NMOS領域RNにボロンを注入することにより、アクセストランジスタおよびドライブトランジスタのハロ領域となるp型不純物領域が形成される。さらに他のレジストマスクを注入マスクとして、PMOS領域RPにリンまたは砒素を注入することにより、ロードトランジスタのハロ領域となるn型不純物領域が形成される。

(もっと読む)

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体集積回路及びデータ処理システム

【課題】意図的に誤動作を生じさせるための局所的な光照射を検出するための構成を小さなチップ占有面積で実現し、検出感度を高くする。

【解決手段】ロジック回路(6)が形成された領域に分散され初段の入力が一定論理値にされて直列的に接続された複数個の検出インバータ(100)を検出素子として採用し、単数又は複数のインバータに光が照射されて各々に出力が反転することによって直列的に接続された複数個の検出インバータの最終出力が判定され、これにより局所的な光照射を検出することができる。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタに適当なしきい値電圧が与えられる一方、抵抗素子はシリコン膜からなる抵抗体層の異常成長を抑制して、シリコン膜の膜厚を安定化する。

【解決手段】半導体装置は、半導体基板10の上部に形成された素子分離領域12によって囲まれた第1の活性領域10a、第1の活性領域の上に形成された第1の高誘電体膜14aを有する第1のゲート絶縁膜27a、及び第1のゲート絶縁膜の上に形成された第1のゲート電極28aとを有する第1導電型の第1のMISトランジスタ1aと、素子分離領域の上に形成された第2の高誘電体膜14x、及び該第2の高誘電体膜の上に形成されたシリコンからなる抵抗体層20xを有する抵抗素子1xとを備えている。第1の高誘電体膜と第2の高誘電体膜とは、互いに同一の高誘電体材料からなり、第1の高誘電体膜は第1の調整用金属を含み、第2の高誘電体膜は第1の調整用金属を含まない。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】1メモリセルが6トランジスタを有するSRAMにおいて、コンタクトの微細化をするとリークの発生を回避できる半導体記憶装置及びその製造方法を提供する。

【解決手段】1メモリセルが第1及び第2ドライバトランジスタ(DTr1、DTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)並びに第1及び第2ロードトランジスタ(LTR1,LTr2)の6トランジスタを有するSRAMにおいて第1ドライバトランジスタと第2ドライバトランジスタのソースドレイン領域に基準電位を印加するための接地コンタクトCgと、第1ロードトランジスタと第2ロードトランジスタのソースドレイン領域に電源電位を印加するための電源電位コンタクトCcの径が、共通コンタクトCsを除く他のコンタクト(Cb,Cn,Cw)の径より大きく形成された構成とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】MISトランジスタにおけるシリコン混晶層からなるソースドレイン領域を、不純物の拡散による不具合を防止しながらチャネル領域に近づけることができるようにする。

【解決手段】半導体装置は、半導体基板10からなるn型の活性領域の上に、ゲート絶縁膜12を介在させて形成されたゲート電極13と、活性領域におけるゲート電極13の両側方の領域に形成されたp型ソースドレイン領域20と、活性領域における各p型ソースドレイン領域20の側面からそれぞれゲート電極13の下側に向かって形成されたn型ポケット領域18とを有している。p型ソースドレイン領域20は、シリコンとIV族元素との混晶層からなり、混晶層は、ゲート長方向におけるゲート電極側の側面がゲート電極側に突き出す凸部20aを有している。凸部20aの先端は、ポケット領域18によって覆われている。

(もっと読む)

半導体装置の製造方法

【課題】NMOSトランジスタおよびPMOSトランジスタを有する半導体装置において、ショートチャネル効果を抑制するとともに、ゲート−ドレイン間での電流リークを低減し、また、ゲートオーバーラップに起因する寄生容量を低減して、回路動作速度の低下を低減した半導体装置を提供する。

【解決手段】低電圧NMOS領域LNRにおけるシリコン基板1の表面内に、N型不純物、例えばヒ素をイオン注入により比較的低濃度に導入して、エクステンション層61を形成する。そして、シリコン基板1の全面を覆うように、シリコン酸化膜OX2を形成し、ゲート電極51〜54の側面においてはシリコン酸化膜OX2をオフセットサイドウォールとして使用し、低電圧PMOS領域LPRにおけるシリコン基板1の表面内に、ボロンをイオン注入により比較的低濃度に導入して、エクステンション層62となるP型不純物層621を形成する。

(もっと読む)

半導体素子及びその製造方法、並びに固体撮像装置

【課題】工数の増加を招くことなく、更には、特性劣化を抑止して高品質の製品を供給することができる半導体素子の製造方法を提供する。

【解決手段】画素2に形成されたトランジスタのゲート電極305〜307の周辺にイオン注入を行うことでソース領域及びドレイン領域として機能するn+領域426、427を形成し、その後に、ブロック膜として機能する第1の絶縁膜35及び第2の絶縁膜36を成膜し、エッチバックによって第1の絶縁膜35及び第2の絶縁膜36をその一部としたゲート電極のサイドウォールを形成する。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチの数が1個のトレンチゲート構造のトランジスタをトレンチの数が2個以上のトレンチゲート構造のトランジスタとともに基板上に形成する際の特性の差異を低減する。

【解決手段】半導体装置100は、ゲート幅方向に断続的に深さが変化するように形成されたn個のトレンチ162を有するトランジスタであって、n=1の第1のトランジスタ200とn=2以上の第2のトランジスタ202と、各トランジスタが形成された領域の周囲に形成されて当該トランジスタが形成された領域を区分けする素子分離絶縁膜110と、を含む。ここで、第1のトランジスタ200のゲート幅方向における一つのトレンチ162と素子分離絶縁膜110との間の間隔cxが、第2のトランジスタ202のゲート幅方向におけるトレンチ162間の間隔axよりも狭い。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】ゲート電極構造の垂直方向の抵抗を低減する。

【解決手段】半導体基板1と、半導体基板1の上に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成された仕事関数制御層3と、仕事関数制御層3の上に形成された第1のシリサイド層4と、第1のシリサイド層4の上に形成されたポリシリコンゲート電極5と、ポリシリコンゲート電極5の下の半導体基板1中の領域を挟んで半導体基板1中に形成されるソース領域6およびドレイン領域7と、を有する半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極抵抗の増大や工程数の増加を招くことなく、シリコン混晶層を用いた歪技術により、半導体装置の高性能化を実現する。

【解決手段】半導体基板100における第1のゲート電極106Aから見て第1の絶縁性サイドウォールスペーサ111Aの外側に第1のソースドレイン領域114Aを形成する。その後、半導体基板100における第2のゲート電極106Bから見て第2の絶縁性サイドウォールスペーサ111Bの外側にリセス部119を形成すると共に、第2のゲート電極106Bを部分的に除去する。その後、リセス部109内に、第2のソースドレイン領域114Bとなるシリコン混晶層120を形成する。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、まず支持基板SSと、埋め込み絶縁膜BOXと半導体層SLとがこの順で積層された構成を有する半導体基板SUBが準備される。半導体層SLの主表面に、導電部分を有する素子が完成される。上記素子を平面視において取り囲む溝DTRが、半導体層SLの主表面から埋め込み絶縁膜BOXに達するように形成される。上記素子上を覆うように、かつ溝DTR内に中空を形成するように素子上および溝DTR内に第1の絶縁膜(層間絶縁膜II)が形成される。上記第1の絶縁膜に素子の導電部分に達する孔であるコンタクトホールCHが形成される。

(もっと読む)

261 - 280 / 1,808

[ Back to top ]