Fターム[5F048CA12]の内容

MOSIC、バイポーラ・MOSIC (97,815) | バイポーラトランジスタの構造 (853) | ウェルコレクタ (55)

Fターム[5F048CA12]に分類される特許

1 - 20 / 55

半導体装置の製造方法

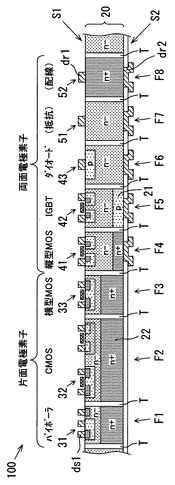

【課題】能動素子または受動素子が一つの半導体基板に複数個形成されてなる半導体装置およびその製造方法であって、両面電極素子についても絶縁分離と集積化が可能であり、安価に製造することのできる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板20が、当該半導体基板20を貫通する絶縁分離トレンチTに取り囲まれて、複数のフィールド領域F1〜F8に分割されてなり、複数個の能動素子31〜33,41〜43または受動素子51,52が、それぞれ異なるフィールド領域F1〜F8に分散して配置されてなり、二個以上の素子が、当該素子に通電するための一組の電極dr1,dr2が半導体基板20の両側の表面S1,S2に分散して配置されてなる、両面電極素子41〜43,51,52である半導体装置100とする。

(もっと読む)

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

拡散抵抗素子およびその製造方法

【課題】ノイズおよび抵抗バラツキが小さな拡散抵抗の製造方法を提供することを目的とする。

【解決手段】半導体基板の表面付近にp型拡散層114を形成する工程と、拡散抵抗体となるp型拡散層114の第1領域の表面上に、層間絶縁膜とは異なる絶縁膜であって当該第1領域の表面を保護するカバー膜125を形成する工程と、カバー膜125を形成する工程の後、カバー膜125の前記第1領域に接する第2領域に前記第1領域よりも高い濃度で拡散抵抗体のコンタクト部となるp型拡散層116を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】同一基板上に混載された他の素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】半導体装置は、p形半導体層12と、n形のソース領域13と、絶縁体23と、n形半導体領域20と、n形のドレイン領域14と、p形のチャネル領域12aと、ゲート絶縁膜15と、ゲート電極16と、ソース電極18と、ドレイン電極19と、電極21とを備える。前記絶縁体は、前記p形半導体層の表面から前記p形半導体層の厚み方向に延びて形成されたトレンチt1内に設けられている。前記n形半導体領域は、前記ドレイン領域と前記絶縁体との間の前記p形半導体層の表面に設けられる。前記電極は、前記n形半導体領域に接続される。

(もっと読む)

半導体装置およびその製造方法ならびに不揮発性半導体記憶装置

【課題】これまでのMOSFETと同等の集積性を維持しながら、MOSFETに比べて優れたスイッチング特性をもつ、すなわち、室温においてS値が60mV/桁より小さな値をもつ半導体素子を提供する。

【解決手段】MOSFETと、トンネル接合を有するトンネルバイポーラトランジスタを組み合わせることにより、低電圧であっても、ゲート電位変化に対してドレイン電流が急峻な変化(S値が60mV/桁よりも小さい)を示す半導体素子を構成する。

(もっと読む)

ESD保護素子、半導体装置およびプラズマディスプレイ装置

【課題】 製造コストを上昇させることなくSOI構造の高耐圧半導体集積回路装置に組み込むことができるとともに、チップ面積の増大を抑制できるESD保護素子を提供する。

【解決手段】

ESD保護素子は、埋め込み絶縁膜2上に形成され、素子分離領域17で囲まれた第1導電型半導体層3、半導体層3に形成された第1導電型第1半導体領域8、第1導電型第1半導体領域8から離間して半導体層3に形成された第2導電型第1半導体領域16、第2導電型第1半導体領域16に形成され、それより高不純物濃度の第2導電型第2半導体領域10、第2導電型第2半導体領域10に形成された高不純物濃度の第1導電型第2半導体領域9からなる構造を有している。また、第1電極12および第2電極13は高耐圧半導体回路に電気的に接続され、第2導電型第1および第2半導体領域16、10は電気的にフローティング状態となっている。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

半導体装置の製造方法

【課題】異なる直流電流増幅率(hfe)を有する複数のバイポーラトランジスタを混載した半導体装置を、簡易且つ工程数が少なく得られる半導体装置の製造方法を提供すこと。

【解決手段】第2バイポーラトランジスタ20のエミッタ領域25又はその周囲上であって、当該エミッタ領域25におけるコンタクト領域25Aの周辺上にダミー層52を形成することで、その後、層間絶縁層53の厚みを厚層化することができるため、第2バイポーラトランジスタ20のエミッタ領域25では第1バイポーラトランジスタ10のエミッタ領域15に比べコンタクト深さを浅くしてコンタクトホール54が形成される。これにより、第1バイポーラトランジスタ10と第2バイポーラトランジスタ20との直流電流増幅率(hfe)を変更できる。ダミー層52の形成は第2バイポーラトランジスタ20のベース領域26、コレクタ領域27であってもよい。

(もっと読む)

参照電圧発生回路および受信回路

【課題】 電源電圧依存性および温度依存性の低い参照電圧発生回路を提供し、もって受信感度の良好な受信回路を実現する。

【解決手段】 受信回路は、AMI符号化された一対の信号を増幅する差動増幅回路(11)と、差動増幅回路の出力と所定の参照電圧とを比較して入力信号の論理レベルを判別する受信データ判定回路(12)と、前記参照電圧を発生する参照電圧発生回路(13)とを備え、参照電圧発生回路は電源電圧を基準にした温度依存性の低い参照電圧を発生するように構成した。

(もっと読む)

静電気保護用半導体装置

【課題】 半導体集積回路をESDの過電流ノイズ及びラッチアップ試験の過電流ノイズから保護する保護回路であって、電源端子から保護素子への配線の配置の自由度を高めることができ、チップ面積の増大とはならない、保護回路を提供する。

【解決手段】 ラッチアップ試験の過電流ノイズから保護するバイポーラトランジスタ12のベース接地電流増幅率を0.5〜1.0になるような構造とすることで、I/O端子10から入ったラッチアップ試験の過電流ノイズは、バイポーラトランジスタ12を通り接地端子11へ流れるので、電源端子9からバイポーラトランジスタ12のベースへの配線を細くすることが可能となり、配線配置の自由度が高まる。

(もっと読む)

半導体装置およびプラズマディスプレイデバイス

【課題】寄生抵抗が小さく、かつ電流駆動能力が大きい高耐圧ハイブリッドトランジスタのような半導体装置の構造を提供する。

【解決手段】第1導電型の半導体層22に第1導電型のベース領域9を備える。ベース領域9には第2導電型のエミッタ領域10が設けられる。半導体層22にはベース領域9に隣接して半導体層22の表面から半導体層22の厚さより小さい所定深さにわたって第2導電型の不純物層23が設けられる。不純物層23にはベース領域9から離間して第1導電型のコレクタ領域11および第2導電型のドレイン領域14が設けられる。半導体層22の表面上には、エミッタ領域10の端部上、ベース領域9上および不純物層23上の一部にわたってゲート絶縁膜12を介してゲート電極13が設けられる。エミッタ領域10とベース領域9とに共通接続された第1電極15と、コレクタ領域11とドレイン領域14とに共通接続された第2電極16とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】エミッタ電極の膜厚が均一であり、このために素子特性のばらつきが少ない特性が良好な半導体装置を提供する。

【解決手段】Si基板1上のN−hill層11と、N−hill層11を囲む素子分離領域であるシャロートレンチアイソレーション6に開口されたオープン領域21と、を備えたHCBT100を含む半導体装置において、オープン領域21上に面方位のないアモルファスSi膜30,31を形成する。アモルファスシリコン膜30、31を、N−hill層11がアモルファスシリコン膜30、31から露出する厚みにまでエッチングして電極とする。

(もっと読む)

半導体装置とその製造方法

【課題】MOSトランジスタとバイポーラトランジスタとが混載された半導体装置とその製造方法において、半導体装置の信頼性を高めること。

【解決手段】シリコン基板20素子分離絶縁膜24を形成する工程と、シリコン基板20に低電圧p型MOSトランジスタTRLVP用のLDD領域45を形成する工程と、シリコン基板20に高電圧p型MOSトランジスタTRHVP用のLDD領域55をLDD領域45よりも深く形成するのと同時に、シリコン基板20にバイポーラトランジスタTRBIP用の第1のエミッタ領域46を形成する工程と、各領域45、46、55におけるシリコン基板20の表層に高融点金属シリサイド層70を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

パワー半導体素子

【課題】小電流領域から大電流領域までの広範な負荷電流の電流値において、従来例に比較して、電力の変換効率を向上させることが可能なパワー半導体装置を提供する。

【解決手段】本発明のパワー半導体素子は、第1ゲート電極によりスイッチングの制御が行われるパワー半導体素子であり、IGBT動作とMOSトランジスタ動作との切替を行う第2ゲートを有し、第1ゲート電極により、スイッチング動作をさせる際、負荷に流れる負荷電流の電流値に応じて、第2ゲート電極に対して制御信号を印加し、MOSトランジスタにて動作させるか、またはバイポーラトランジスタとして動作させるかのいずれかを選択する。

(もっと読む)

半導体デバイス、半導体基板に分離されたポケットを形成する方法、半導体構成、PNPトランジスタ、横型NチャネルDMOSトランジスタ、横型トレンチDMOSトランジスタ

【課題】モジュール化された、相互作用しないやり方で、単一の半導体ウェハにともに接近して実装され、十分に分離された、最適化されたトランジスタまたは他のデバイスの任意の集合の作製を可能にする。

【解決手段】

一群の半導体デバイスが、エピタキシャル層を含まない基板に形成される。一実施例では、この一群は、5VのCMOSペア、12VのCMOSペア、5VのNPN、5VのPNP、いくつかの形状の横型トレンチMOSFET、および30V横型N−チャネルDMOSを含む。これらのデバイスの各々は、横方向かつ縦方向の双方において極めて小型であり、基板の他のすべてのデバイスから十分に分離され得る。

(もっと読む)

半導体装置

【課題】製造後に電流増幅率hFE特性を変化させることができるバイポーラトランジスタを備えた半導体装置を提供する。

【解決手段】P型半導体層1に、N型拡散層からなるコレクタ3、P型拡散層からなるベース5、N電型拡散層からなるエミッタ7が形成されてバイポーラトランジスタが形成されている。そのバイポーラトランジスタはベース5上及びコレクタ3にゲート絶縁膜9を介してゲート電極11を備えている。コレクタ3にはコレクタ配線13が接続されている。ベース5にはベース配線15が接続されている。エミッタ7にはエミッタ配線17が接続されている。ゲート電極11にはゲート電極配線19が接続されている。配線13,15,17,19は互いに電気的に絶縁されている。

(もっと読む)

新構造半導体集積回路

【課題】現在、半導体集積回路で使用されているバイポーラトランジスタとMOSトランジスタは最初に発明された時よりその構造は変わっておりません。構造と原理を根本的に見直し、高速化・低消費電力化・微細化を進展させる。

【解決手段】サブミクロンスケールの微細加工技術を用い、新しい原理と構造のトランジスタによる半導体集積回路を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 エミッタ注入効率が大きく、差動増幅回路の入力トランジスタとして利用可能で、かつBi−CMOSプロセスにおいてMOSトランジスタと同一基板上に搭載することが可能なバイポーラトランジスタの構造とその製造方法を提供する。

【解決手段】 半導体基板1上に第二導電型の深いウェル層2が形成され、深いウェル層2よりは浅い所定の深さで第一導電型の埋め込み層3が形成され、バイポーラトランジスタのエミッタ領域が、第一導電型の埋め込み層3の上に、第二導電型のウェル層4、及びMOSトランジスタのソース・ドレイン領域と同時形成される高濃度の第二導電型の不純物層15の2層構造として形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】同一の半導体基板上に数種類のトランジスタを簡易なプロセスによって形成する半導体装置の製造方法の提供。

【解決手段】LDMOS領域100とオフセットドレインMOS領域200とに、同時に、第2導電型の第1ウェル30を形成する工程と、LDMOS領域100の第1ウェル30と、CMOS領域100とに、同時に、第1導電型の第2ウェル32を形成する工程と、CMOS領域300に、第2導電型の第2ウェル34を形成する工程と、オフセットドレインMOS領域200に第1導電型のオフセット層22を形成する工程とを含み、第1ウェル30は、第2ウェル32,34よりも深いウェルであり、第2ウェル32,34は、高エネルギーイオン注入法によって形成されたレトログレードウェルである、半導体装置の製造方法。

(もっと読む)

1 - 20 / 55

[ Back to top ]