Fターム[5F048CB06]の内容

MOSIC、バイポーラ・MOSIC (97,815) | 3次元MOSIC(BiMOSを含む) (767) | 縦型MOSIC、ダブルゲートMOS (373)

Fターム[5F048CB06]の下位に属するFターム

垂直チャネル (271)

縦方向に対向する二重ゲート (45)

Fターム[5F048CB06]に分類される特許

1 - 20 / 57

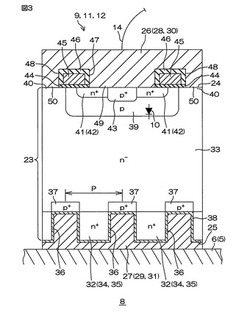

半導体装置およびその製造方法

【課題】低電流領域でのオン電圧を低減することができる、SiC−IGBTを備える半導体装置およびその製造方法を提供すること。

【解決手段】エミッタ電極26と、エミッタ電極26に接続されたエミッタ領域41と、エミッタ領域41に対してSiC半導体層23の裏面25側にエミッタ領域41に接して形成されたチャネル領域39と、チャネル領域39に対してSiC半導体層23の裏面25側にチャネル領域39に接して形成されたSiCベース層33と、SiCベース層33に対してSiC半導体層23の裏面25側にSiCベース層33に接して形成されたコレクタ領域37と、コレクタ領域37に接続されたコレクタ電極27とを含む、SiC−IGBT9に対してMOSFET11を並列に接続する。

(もっと読む)

半導体装置の製造方法

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

半導体装置

【課題】 半導体層にIGBT領域とダイオード領域が混在している半導体装置において、寄生ダイオードの動作を抑制する技術を提供する。

【解決手段】 半導体装置100は、素子範囲と、素子範囲を囲む終端範囲に区画された半導体層15を有する。素子範囲には、IGBT領域10とダイオード領域12が形成されている。半導体層15のうちのダイオード領域12の裏面部は、n型のカソード領域が形成されているカソード部分38aと、上記n型のカソード領域が形成されていない非カソード部分38bを有している。半導体装置100では、非カソード部分38bがダイオード領域12の中心側よりも端部側に相対的に多く存在する。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体メモリ装置

【課題】酸化物半導体のようなバンドギャップが大きな半導体を用いたメモリ装置の保持特性を高める。

【解決手段】ビット線の一端にバックゲートを有するトランジスタ(バックゲートトランジスタ)を直列に挿入し、そのバックゲートの電位は常に十分な負の値となるようにする。また、ビット線の最低電位はワード線の最低電位よりも高くなるようにする。電源が切れた際には、ビット線はバックゲートトランジスタによって遮断され、ビット線に蓄積された電荷が流出することが十分に抑制される。この際、セルトランジスタのゲートの電位は0Vであり、一方で、そのソースやドレイン(ビット線)の電位は、ゲートよりも十分に高いので、セルトランジスタは十分なオフ状態であり、データを保持できる。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

半導体装置

【課題】1個の柱を用いてインバータを構成することにより、高集積なCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のシリコンと、該第1のシリコンとは極性が異なる第2のシリコンと、前記第1のシリコンと前記第2のシリコンとの間に配置され、基板に対して垂直方向に延びている第1の絶縁物とからなる1本の柱と、前記第1のシリコンの上下のそれぞれに配置され、前記第1のシリコンとは極性が異なる第1の高濃度不純物を含むシリコン層と、前記第2のシリコンの上下のそれぞれに配置され、前記第2のシリコンとは極性が異なる第2の高濃度不純物を含むシリコン層と、前記第1のシリコンと前記第2のシリコンと前記第1の絶縁物とを取り囲む第2の絶縁物と、前記第2の絶縁物を取り囲む導電体とを含む半導体装置により、上記課題を解決する。

(もっと読む)

半導体装置及び半導体素子

【課題】本発明は、スイッチング損失を低減できる半導体装置及び半導体素子を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、第1ゲートを有し該第1ゲートからの信号でオンオフが制御される第1素子部と、第2ゲートを有し該第2ゲートからの信号でオンオフが制御される第2素子部と、を有する半導体素子と、該第1ゲート及び該第2ゲートに接続され、該半導体素子をターンオンするときは該第1素子部と該第2素子部を同時にターンオンし、該半導体素子をターンオフするときは該第2素子部を該第1素子部よりも遅延してターンオフするように該第1ゲートと該第2ゲートに信号を伝送する信号伝送手段と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】たとえばDC−DCコンバータ等の電源または電力変換機器のスイッチング等に使用されるパワーMOSFET等の絶縁ゲートを有するパワー系能動素子は、スイッチングの高速化に伴い、ゲート容量を極力小さくする必要がある。このためには、チャネルとならない部分のゲート電極を取り去り、スプリットゲートとする手法が有効とされている。しかし、Nチャネル型パワーMOSFETを例に取り説明すると、その反作用として、チャネルを形成するP型ボディ領域の端部に電界が集中するため、パンチスルー耐圧が低下する等の問題が発生する。

【解決手段】本願の一つの発明は、プレーナ−バーティカル型パワーMOSFET等の絶縁ゲートを有するパワー系能動素子を有する半導体装置に於いて、各アクティブセル内のスプリットゲート間にトレンチ内に延在するフィールドプレート、すなわち、トレンチフィールドプレートを設けたものである。

(もっと読む)

半導体素子およびその駆動方法

【課題】双方向で電流の流れを制御(ON/OFF制御)することができる半導体素子を提供すること。

【解決手段】チャネル層8と障壁層10が積層された半導体へテロ接合と、前記半導体へテロ接合の上方に設けられたゲート12と、前記ゲートの両側に設けられた第1および第2のソースドレイン端子14a,14bと、前記第1のソースドレイン端子と前記ゲートの間に設けられた第1のフィールプレート16aと、前記第2のソースドレイン端子と前記ゲートの間に設けられた第2のフィールドプレート16bとを有すること。

(もっと読む)

半導体装置

【課題】トレンチゲートをゲート電極で完全に埋め込むトレンチゲート型MOSFETにおいて、パフォーマンスに優れた半導体回路装置を提供する。

【解決手段】第1の導電型のウェル層4内に形成された第2の導電型のウェル層5が、ゲート電極材料9で埋設された格子状のトレンチ溝7で囲まれたトレンチゲート型MOSFETであって、トレンチ溝7の側面と第2の導電型のウェル層5との間に形成される第1の絶縁膜8は、トレンチ溝7の側面と前記第1の導電型のウェル層4との間に形成される第2の絶縁膜14よりも薄くしてある。

(もっと読む)

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

半導体装置

【課題】ダイオード内蔵スイッチング素子において、良好なダイオード損失特性を実現する。

【解決手段】半導体基板32の一面33側においてはダイオード領域20およびIGBT領域10のうちIGBT素子を除いた領域に半導体基板32の一面33を基準として所定の深さまで低ライフタイム領域49を設け、半導体基板32の他面47側においてはIGBT領域10に半導体基板32の他面47を基準として所定の深さまで低ライフタイム領域49を設ける。これにより、ダイオード素子の動作時にドリフト層30に残されたホールが低ライフタイム領域49によって再結合して消滅するため、IGBT領域10からダイオード領域20へのホールの注入を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】 接着剤を用いることなく、かつ、容易にマスク部材を着脱することが可能な技術を提供する。

【解決手段】 第1吸着口112aと第2吸着口114aを有するステージ110とマスク部材120を使用する半導体装置の製造方法であって、第1吸着口112aが塞がれるようにステージ110上に半導体ウエハ100を載置するとともに、第1吸着口112aにより半導体ウエハ100を吸着固定する工程と、吸着固定されている半導体ウエハ100の上方にマスク部122が位置し、かつ、第2吸着口114aが塞がれるようにステージ110上にマスク部材120を載置するとともに、第2吸着口114aによりマスク部材120を吸着固定する工程と、吸着固定されているマスク部材120のマスク部122を通して吸着固定されている半導体ウエハ100に荷電粒子を注入する工程を有する。

(もっと読む)

半導体装置

【課題】絶縁ゲート型電界効果トランジスタのスイッチング速度低下を防止し、省スペース化を実現する半導体装置を提供する。

【解決手段】本発明に係る半導体装置90は、絶縁ゲート型電界効果トランジスタとコンデンサが同一チップ上に形成されたものであって、表層において、n−型エピタキシャル層2を挟持するp型ボディ領域5内にそれぞれ配設されたn+型ソース領域6の当該n−型エピタキシャル層2に最近接する端部間に亘る領域上に配設された絶縁層7と、絶縁層7を介してn−型エピタキシャル層2と対向されるコンデンサ上部電極40と、絶縁層7上でコンデンサ上部電極40の両サイドに絶縁分離されるように、かつチャネル形成可能な位置に配設されたゲート電極31を備える。コンデンサC1は、コンデンサ上部電極40を上部電極とし、これと絶縁層7を介して対向配置されるn−型エピタキシャル層2を下部電極とする。

(もっと読む)

トレンチゲート型半導体装置

【課題】飽和電流までの電流を正確に検出できるトレンチゲート型半導体装置を提供する。

【解決手段】本発明のトレンチゲート型半導体装置は、主IGBT領域とセンスIGBT領域とにそれぞれチャネルを形成したアクティブセルと、チャネルを形成していないフローティングセルとを交互に配置し、主IGBT領域とセンスIGBT領域のアクティブセルの幅とフローティングセルの幅との比を所定の値に設定して主IGBT領域とセンスIGBT領域とが同様な飽和電流特性になるように制御した。

(もっと読む)

パワー・スイッチの構造および方法

【課題】低RDSonおよび低電流制限の両方を提供する一方で、ホット・スポットおよび熱暴走の効果を低減する回路を提供する。

【解決手段】本発明の一実施例において、パワー・スイッチング・デバイス(33)は、第1MOSFETデバイス(41)および第2MOSFETデバイス(42)を含む。第1ゲート電極(48,87)を含む分割ゲート構造(84)は、第1MOSFETデバイス(41)を制御する。第2ゲート電極(49,92)は、第2MOSFETデバイス(42)を制御する。電流制限デバイス(38)は、第1ゲート電極(48,97)に結合され、電流制限モード中に第1MOSFETデバイスをオンにする。比較器デバイス(36)は、第2ゲート電極(49,92)に結合され、パワー・スイッチング・デバイス(33)が電流制限モードでなくなったときに、第2MOSFETデバイス(42)をオンにする。

(もっと読む)

内燃機関点火装置用半導体装置

【課題】エネルギー耐量、負サージ耐量を確保しながら、できる限り低コストの内燃機関用点火装置用半導体装置を提供すること。

【解決手段】IGBTが前記コレクタ電極とゲート電極間にクランプダイオードを備え、IGBTのp+25とn型ベース層26の間に不純物濃度の異なる2層のn型バッファ層24、50を有するIGBTであって、前記2層のバッファ層の合計厚さが50μm以下であって、総不純物量を20×1013cm-2以下とする。

(もっと読む)

電流検出機能を有する半導体装置

【課題】センサスイッチング素子のセンサ電極とゲート電極の間のESD等の過電圧に対する対策を講じながらも、ゲート駆動損失の増加が防止された半導体装置を提供すること。

【解決手段】メインスイッチング素子領域26のメイン電極24と、センサスイッチン

グ素子領域27のセンサ電極25と、メイン電極24とセンサ電極25の間に形成されて

おり、メイン電極24とセンサ電極25の間に所定の電位差が形成されたときに両者間を

導通する保護素子30を備えていることを特徴とする半導体装置10。

(もっと読む)

半導体装置

【課題】ダイオード領域とIGBT領域の間における熱伝導を阻害することなく、境界部における逆電流を抑制することができる半導体装置を提供する。

【解決手段】ダイオード領域20とIGBT領域40を有する半導体基板を備える半導体装置10であって、ダイオードドリフト領域27とIGBTドリフト領域49の間の少なくとも一部の範囲に、n型であり、ダイオードドリフト領域27及びIGBTドリフト領域49よりもn型不純物濃度が高いバリア領域74が形成されている。

(もっと読む)

1 - 20 / 57

[ Back to top ]