Fターム[5F058BA02]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成の目的、効果 (3,596) | 素子分離 (92)

Fターム[5F058BA02]に分類される特許

41 - 60 / 92

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備える平板表示装置

【課題】酸素を含む化合物半導体を活性層とする薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、基板10上に形成されたゲート電極12と、ゲート絶縁膜13によりゲート電極12と絶縁され、ゲート電極12を覆うようにゲート絶縁膜13上に形成された、酸素を含む化合物半導体からなる活性層14と、活性層14の上部に形成された保護層15と、活性層14と接触するソース電極16a及びドレイン電極16bと、を備え、保護層15が、チタン酸化物(TiOx)またはチタン酸窒化物(TiOxNy)で形成される。

(もっと読む)

ポリシロキサン系トレンチ埋め込み用反応物

【課題】基体に形成されたトレンチ内に酸化シリコンを埋め込むために使用するのに好適な溶液のポットライフが長く、トレンチへの埋め込み性が高く、HF耐性、クラック耐性を有するトレンチ埋め込み用反応物を提供する。

【解決手段】トレンチ埋め込み用縮合反応物を、該縮合反応物が少なくともポリシロキサン化合物とシリカ粒子との縮合反応物を含み、該ポリシロキサン化合物がHSiO3/2基、MeHSiO基、及びH2SiO基から選ばれる基の少なくとも一種を40mol%以上有し、該ポリシロキサンの重量平均分子量が1000以上200000以下であり、該シリカ粒子の平均一次粒径が1nm以上100nm以下とする。

(もっと読む)

PECVDを用いた流動性誘電体による間隙の充填

【課題】アスペクト比が高くて幅が狭い凹状フィーチャーに誘電層を形成するための新規方法を提供する。

【解決手段】間隙に流動性重合膜をプラズマ強化化学気相成長(PECVD)法によって形成した後で、当該膜を誘電材料に変換するためのインサイチュ(in−situ)処理を実行することを含む。インサイチュ処理は、純粋な熱処理プロセスまたはプラズマ処理プロセス。堆積−インサイチュ処理−堆積−インサイチュ処理というプロセスを実行して、間隙に誘電層を形成する。この一連の手順は、間隙をボトムアップ式に充填するべく必要なだけ繰り返される。エクサイチュ処理後プロセスは、間隙の充填が完了した後で実行される。特定の実施形態によると、誘電率が3.0未満の膜が形成される。上記プロセスは、フロントエンドおよびバックエンドの間隙充填に利用可能である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】熱CVD法で素子分離溝に絶縁膜を埋め込む際に、アクティブエリアの変形を防止する。

【解決手段】本発明の半導体装置の製造方法は、シリコン基板1上に被加工膜を形成し、シリコン基板1及び被加工膜を加工して素子分離溝5を形成し、素子分離溝5に熱CVD法により絶縁膜6を埋め込む製造方法であって、絶縁膜6を埋め込む工程の熱CVD法の成膜条件を、素子分離溝5のうちのシリコン基板1の上面1aの高さ以下の部分を埋め込む絶縁膜6aの空孔率が5%以上となると共に、素子分離溝5のうちのシリコン基板1の上面1aの高さを越える部分を埋め込む絶縁膜6bの堆積速度が素子分離溝5のうちのシリコン基板1の上面1aの高さ以下の部分を埋め込む絶縁膜6aの堆積速度よりも小さくなる条件に設定した。

(もっと読む)

酸化膜の作成方法及び半導体装置の製造方法

【課題】低温の酸化処理により酸化膜を形成する。

【解決手段】酸化膜の作成方法は、主鎖にSi−N結合を有する高分子化合物を含む第1の膜16と主鎖にSi−O結合を有する高分子化合物を含む第2の膜15とを積層する工程と、前記第1の膜16及び前記第2の膜15を水蒸気又は水性の雰囲気中で加熱処理し、前記第1の膜16及び前記第2の膜15を酸化膜18に変化させる工程と、を具備する。

(もっと読む)

半導体装置

【課題】高温の酸化性雰囲気中でのSOD膜の改質を促進する。ライナー膜下部の素子や半導体基板が酸化されてダメージを受けることを防止する。

【解決手段】凹部と、凹部の内壁側面上に順に形成した、第1のライナー膜と、酸素原子を含有する第2のライナー膜と、凹部内に充填された絶縁領域と、を有し、第1のライナー膜は第2のライナー膜よりも耐酸化性が優れるものとした半導体装置。

(もっと読む)

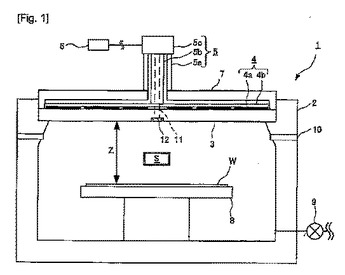

酸化珪素膜およびその形成方法、コンピュータ読み取り可能な記憶媒体並びにプラズマCVD装置

【課題】 膜中に実質的に水素を含まず、絶縁性が高く良質な酸化珪素膜をプラズマCVD法により形成する。

【解決手段】 複数の孔を有する平面アンテナにより処理容器内にマイクロ波を導入してプラズマを生成するプラズマCVD装置を用い、処理容器内の圧力を0.1Pa以上6.7Pa以下の範囲内に設定し、SiCl4ガスまたはSi2H6ガスと酸素含有ガスとを含む処理ガスを用いてプラズマCVDを行うことにより、0.5%希フッ酸溶液によるエッチングレートが、0.11nm/秒以下である緻密で絶縁性に優れ、高品質な酸化珪素膜(SiO2膜、SiON膜)を形成する。

(もっと読む)

電子デバイス材料の製造方法

【課題】電気的特性の優れた絶縁膜のプラズマ処理方法を提供する。

【解決手段】本発明に係るプラズマ処理方法の一形態は、絶縁膜が形成された基板を真空容器内に搬入する工程と、上記真空容器内に供給された処理ガスに300MHz以上2500MHz以下の周波数を有する高周波電力を供給することによりプラズマを生成し、上記プラズマにより、上記絶縁膜を改質する工程と、を含むプラズマ処理方法であって、上記処理ガスは、希ガスと酸素を含む混合ガス、または希ガスと窒素を含む混合ガスであり、上記プラズマは、上記処理ガスが希ガスと酸素を含む混合ガスの場合、上記酸素ガスの流量を1〜1000sccm、上記希ガスの流量を200〜3000sccmとして、上記処理ガスが希ガスと窒素を含むガスの場合、窒素ガスの流量を10〜500sccm、上記希ガスの流量を200〜3000sccmとして生成される。

(もっと読む)

半導体装置の製造方法及び成膜システム

【課題】フッ素添加カーボン膜(CF膜)上にハードマスク用の薄膜であるSiCO膜あるいはSiCN膜を成膜するにあたり、その薄膜とフッ素添加カーボン膜との間で大きな密着性を得ること。

【解決手段】 SiCO膜をハードマスクとして使用する場合に、CF膜をシリコンの有機化合物例えばトリメチルシランガスを活性化したプラズマ雰囲気に例えば5〜10秒程度曝し、次いでこのプラズマに窒素プラズマを加えてフッ素添加カーボン膜の上にSiCN膜を成膜し、その後例えばトリメチルシランガスと酸素ガスとを活性化したプラズマによりSiCO膜を成膜する。SiCO膜の成膜時に、酸素の活性種がCF膜中の炭素と反応することが抑えられ、従ってCF膜の脱ガス量が低減する。またSiCN膜をハードマスクとして使用する場合も、同様に最初にトリメチルシランガスのプラズマ処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】Bulk Fin構造の製造に於いて、ハードマスクの側面の後退・破損を発生させること無く、パッド酸化膜のサイドエッチ量を最小限度にとどめて、ゲート加工等の後工程を行うに際して良好な形状を有するFin構造を実現する。

【解決手段】シリコン基板1上に、所定の間隔SDを隔てて配列し且つ各々が所定の方向へ延在すると共に、所定の高さDを有する複数のシリコン柱体1Fを形成する。その際に、各シリコン柱体1Fの上面には、パッド酸化膜2及びハードマスク3が順次に形成される。その後、酸素ガス、アルゴンガス、水素ガス及びシリコンガスをベースとなる反応ガスとして用いるPVD法によって、隣り合うシリコン柱体1Fによって形成されるリセス1Rを完全に充填すると共に、リセス1Rの上方及びハードマスク3の上方にまで至る埋め込み酸化膜5を堆積する。この堆積時に、幅Wのハードマスク3の側面は削除されない。

(もっと読む)

シャロートレンチアイソレーション膜のためのアミノシラン

【課題】記憶及び論理回路を含む半導体基材、例えば、1つ又は複数の集積回路構造をその上に有するシリコンウェハにおいて用いられるシャロートレンチアイソレーションのための高アスペクト比の特徴のギャップを充填するための酸化条件下で二酸化ケイ素含有膜をスピンオン堆積させる方法を提供する。

【解決手段】高アスペクト比の特徴を有する半導体基材を用意する工程、該半導体基材を低分子量のアミノシランを含む液体配合物と接触させる工程、該半導体基材上に該液体配合物を塗布することにより膜を形成する工程、及び該膜を酸化条件下において高温で加熱する工程を含む方法が提供される。この方法のための組成物もまた記載される。

(もっと読む)

半導体装置およびその製造方法

【課題】配線抵抗を低く維持したままエレクトロマイグレーションの信頼性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】銅配線層CL1は層間絶縁膜II2の表面の配線溝IT1内に形成されている。拡散防止絶縁膜DPは、銅配線層CL1上を覆うように形成されており、かつSiCおよびSiCNの少なくともいずれかよりなっている。絶縁膜SIは、拡散防止絶縁膜DPを介して銅配線層CL1上に形成されており、かつSiNよりなっている。

(もっと読む)

光起電力電池用導体に用いるガラス組成物

本発明は、ケイ素半導体デバイスおよび光起電力電池用導電性ペーストに有用なガラス組成物に関する。厚膜導体組成物は、1つ以上の電気機能性粉末と、有機媒体に分散された1つ以上のガラスフリットとを含む。厚膜組成物はまた1つ以上の添加剤を有していてもよい。例示の添加剤としては、金属、金属酸化物または焼成中、これらの金属酸化物を生成することのできる任意の化合物を挙げることができる。 (もっと読む)

シリコン酸化膜の成膜方法、シリコン酸化膜、半導体装置および半導体装置の製造方法

プラズマ処理装置1のチャンバ2内に、シリコン化合物ガス、酸化性ガス、および希ガスを供給する。マイクロ波をチャンバ2内に供給し、マイクロ波により生成されたプラズマで、被処理基板上にシリコン酸化膜を形成する。希ガスの分圧比は、シリコン化合物ガスと酸化性ガスと希ガスを併せたトータルガス圧の10%以上の割合であって、シリコン化合物ガスと酸化性ガスの有効流量比(酸化性ガス/シリコン化合物ガス)は、3以上11以下とする。  (もっと読む)

(もっと読む)

酸化層の形成方法

本発明は、半導体基板(1)上に酸化層(9)を形成する方法を提供する。この方法は、例えば3次元構造を含む、少なくとも1つの孔(5)を含むような半導体基板(1)を得る工程と、酸性の電解質溶液中で基板を陽極酸化することにより、例えば3次元構造を含む半導体基板(1)上に酸化層(9)を形成する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 熱処理を行う際に、半導体基板の裏面側からの半導体構成原子の昇華を防止し得る半導体装置の製造方法及び半導体製造工程の管理方法を提供する。

【解決手段】 半導体基板10にゲート絶縁膜を形成する工程を有する半導体装置の製造方法であって、ゲート絶縁膜を形成する工程の前に、半導体基板の表面側及び裏面側を覆うように絶縁膜12を形成する工程と、半導体基板の表面側の絶縁膜をエッチング除去する工程と、半導体基板の裏面側に絶縁膜が存在している状態で、半導体基板を熱処理する工程とを有している。

(もっと読む)

半導体メモリ素子の素子分離膜形成方法

【課題】 本発明は、トレンチの底面に流動性の第1の絶縁膜を満たし、第2の絶縁膜を形成した後に乾式エッチング工程及び湿式エッチング工程を行ってトレンチの上部の幅を広げながら第2の絶縁膜に含まれるフッ素(F;fluorine;フローリン)の量を減少させることができる半導体メモリ素子の素子分離膜形成方法を提供することを可能にすることを目的としている。

【解決手段】 トレンチが形成された半導体基板が提供される段階と、トレンチを含む半導体基板上に第1の絶縁膜を形成する段階と、第1の絶縁膜の一部を除去する第1のエッチング工程を行ってトレンチの開口部の幅を広げる段階と、第2のエッチング工程を行って第1の絶縁膜内に含まれた不純物を除去する段階と、第1の絶縁膜を含む半導体基板上に第2の絶縁膜を形成する段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高誘電体膜を用いたキャパシタ構造を有し、平坦化及び微細分離が可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】基板40と、基板40上に配置された複数の下部電極10と、複数の下部電極10上に連続的に配置された高誘電体膜20と、高誘電体膜20上に配置された上部電極30とを備える。

(もっと読む)

半導体装置および、その製造方法

【課題】LDDサイドウォール形成時に、NMOS/PMOS境界領域の2重エッチングによる不具合を克服する。

【解決手段】NMOS/PMOS境界領域にゲートレベル配線を形成し、LDDサイドウォール形成時に2重エッチングされるゲートレベル配線の最上層に、サイドウォール絶縁膜層とエッチング選択比のとれる膜107をハードマスクとして形成しておくことで、ゲートレベル配線に接続するプラグコンタクト112形成時にゲート電極のオーバーエッチによる堆積物の付着を防止する。

(もっと読む)

トレンチ内に誘電層を形成する方法

【課題】半導体構造の形成方法、より具体的にはトレンチ内における誘電層の形成方法を提供する。

【解決手段】半導体構造を形成する方法は、基板上にシリコン酸化被膜を形成するために、シリコン前駆体と原子酸素前駆体を約150℃以下の処理温度において反応させることを含む。シリコン酸化被膜は酸素含有環境内で紫外線(UV)硬化される。

(もっと読む)

41 - 60 / 92

[ Back to top ]