Fターム[5F058BJ06]の内容

Fターム[5F058BJ06]に分類される特許

121 - 140 / 146

二酸化シリコンの膜質を高める新規な堆積プラズマ硬化サイクルプロセス

基板上のギャップを酸化シリコンで充填する方法を記載する。前記方法には、有機シリコン前駆物質と酸素前駆物質を堆積チャンバに導入するステップと、前駆物質を反応させて、基板上のギャップ内に第一酸化シリコン層を形成するステップと、該第一酸化シリコン層をエッチングして層内の炭素含量を減少させるステップと、が含まれるのがよい。前記方法には、第一層上に第二酸化シリコン層を形成するステップと;第二層をエッチングして第二層内の炭素含量を減少させるステップとが含まれるのがよい。ギャップを充填した後に酸化シリコン層をアニールする。 (もっと読む)

総合プロセスモジュレーション(IPM)HDP−CVDによるギャップ充填のための新規な解決法

【課題】 ギャップ充填性能が改善された、プロセスチャンバ内に配置された基板上に酸化シリコン膜を堆積させる方法が提供される。

【解決手段】 ハロゲン源、フルーエントガス、シリコン源、酸化ガス反応種を含むプロセスガスがプロセスチャンバに流し込まれる。少なくとも1011イオン/cm3のイオン密度を有するプラズマがプロセスガスから形成される。酸化シリコン膜が、1.0%未満のハロゲン濃度で基板の上に堆積される。酸化シリコン膜は、同時堆積成分とスパッタリング成分を有するプロセスを用いてプラズマにより酸化シリコン膜が堆積される。プロセスチャンバへのシリコン源の流量に対するプロセスチャンバへのハロゲン源の流量は、実質的に0.5〜3.0である。

(もっと読む)

膜緻密化及び改善されたギャップ充填のための薄膜の多段階アニール

誘電物質を含有するトレンチが誘電物質と基板の間の窒化シリコン層上に形成された基板をアニールする方法であって、基板を酸素含有ガスを含む第一雰囲気中約800℃以上の第一温度でアニールするステップと、基板を酸素を含まない第二雰囲気中約800℃〜約1400℃の第二温度でアニールするステップとを含む、前記方法。 (もっと読む)

半導体素子の製造方法

【課題】微細パターンの形成工程におけるCMP時に生じる不均一性を最小化し、50nm以下の微細パターンを安定的に形成可能な半導体素子の製造方法を提供すること。

【解決手段】被エッチング層(21)上に、第1ハードマスク、第1パッド層及び第2パッド層を積層してエッチングマスクパターンを形成するステップと、エッチングマスクパターンの両側壁に、第1パッド層と同じ物質からなるスペーサを形成するステップと、エッチングマスクパターン間を埋め込むまで、第1ハードマスクとは異なり、且つ、第2パッド層と同じ物質からなる第2ハードマスクを形成するステップと、第1パッド層が露出するまで、第2ハードマスクを平坦化させるステップと、第1パッド層及びスペーサを除去するステップと、残留する第1ハードマスク(22A)及び第2ハードマスク(27B)をエッチングバリアとして、被エッチング層をエッチングするステップとを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】STI構造において素子分離絶縁膜を、高密度プラズマCVD法を使って、引張り応力を蓄積するように形成する。

【解決手段】半導体装置の製造方法は、半導体基板表面に、素子分離溝を形成する工程と、前記半導体基板表面にシリコン酸化膜を、高密度プラズマCVD法により、前記シリコン酸化膜が前記素子分離溝を充填するように、また前記シリコン酸化膜中に水分が、前記シリコン酸化膜を脱水処理した場合、前記シリコン酸化膜に収縮が生じるような量で含まれるように堆積する工程と、前記シリコン酸化膜を脱水し、前記シリコン酸化膜に収縮を誘起する工程と、前記シリコン基板上に堆積したシリコン酸化膜を、前記半導体基板表面が露出するまで化学機械研磨により除去する工程とよりなる。

(もっと読む)

原子層堆積プロセス

【課題】基板上に均一な層を形成することができる原子層堆積プロセスを提供する。

【解決手段】本発明による原子層堆積プロセスは、基板上に均一な層を形成するために以下の工程を提供する。基板を反応室に搬入する。第1前駆体を反応室に導入し、当該第1前駆体は基板の表面の上で反応することによって中間生成物を形成する。第2前駆体を反応室に導入する。第2前駆体は第1付着係数を有する。第2前駆体は中間生成物の一部分と反応して第1生成物を形成する。第3前駆体を反応室に導入する。第3前駆体は大きい付着係数を有する。第3前駆体は中間生成物の残りの部分と反応して第2生成物を形成する。第2前駆体及び第2前駆体の第1生成物は、表面を部分的に被覆することによって第3前駆体の実効付着係数を小さくする。

(もっと読む)

半導体装置の製造方法

【課題】選択的に塗布膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板10上の一部に撥水性樹脂からなる第1の塗布膜60を選択的に形成し、半導体基板10の上に塗布剤を塗布して、第1の塗布膜60が選択的に形成された領域を除いた半導体基板10上に第2の塗布膜62を選択的に形成することを含む。

(もっと読む)

疎水性多孔質シリカ材料による構造物内部の埋め込み方法

【課題】 トレンチ、ホールを埋め込むための多孔質シリカ材料がエッチングなどのプロセス過程で受けるダメージを減じるようにするトレンチ内部の埋め込み方法の提供。

【解決手段】 50〜5000nmの大きさの開口部を有するトレンチ、ホールからなる構造物を設けてある半導体基板に対して、その構造物の内部に配線を形成した後、疎水性多孔質シリカ材料の前駆体を含有する所定の粘度の溶液を基板上に塗布し、加水分解し、焼成して、配線の形成された構造物内部を疎水性多孔質シリカ材料で埋め込む。

(もっと読む)

半導体製造方法及び半導体製造装置

【課題】半導体基板上に形成される被膜の剥離、ダストの発生を抑えることが可能な半導体製造方法及び半導体製造装置を提供する。

【解決手段】半導体基板に第1の被膜を形成する工程と、前記半導体基板の外周部において、第1の被膜の少なくとも一部を除去し、段差を形成する工程と、少なくとも前記段差の形成された領域に、選択的に第2の被膜を形成する工程を備える。

(もっと読む)

半導体装置の製造方法および半導体装置の製造装置

【課題】トレンチおよび半導体基板の表面に形成される絶縁膜のボイドの上の厚みを十分に確保すること。

【解決手段】半導体装置の製造方法のトレンチ形成工程は、p型半導体基板101の表面部分にトレンチ102を形成する。注入工程は、トレンチ形成工程によって形成されたトレンチ102にn型の不純物を注入する。絶縁膜形成工程は、注入工程によってn型不純物が注入されたトレンチ102内部に、粘性の絶縁塗布材料を用いて絶縁膜601を形成する。

(もっと読む)

半導体装置の製造方法

【課題】耐熱性および誘電率を向上させて、かつリーク電流の発生を抑制した窒素添加ハフニウムシリケート膜を有する半導体装置の製造方法を提供する。

【解決手段】本実施形態に係る半導体装置の製造方法は、まず、基板1上に6nm以下の膜厚の第1ハフニウムシリケート膜21を形成する。次に、第1ハフニウムシリケート膜21の第1窒化処理を行って、第1窒素添加ハフニウムシリケート(HfSiON)膜21aを形成する。次に、第1窒素添加ハフニウムシリケート膜21aの第1アニール処理を行う。次に、第1窒素添加ハフニウムシリケート膜21a上に6nm以下の膜厚の第2ハフニウムシリケート膜22を形成する。次に、第2ハフニウムシリケート膜22の第2窒化処理を行って、第2窒素添加ハフニウムシリケート膜22aを形成する。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】 埋め込み性に優れ、誘電率の小さい絶縁膜を用い、電気的特性の優れた半導体装置の製造方法及び製造装置を提供する。

【解決手段】 真空排気したチャンバ1内に酸素ガス及び塩素ガス18を導入すると共に、プラズマアンテナ27に給電することにより、ガスプラズマ14を発生させた後、主として、ケイ素製の被エッチング部材20を塩素ガスラジカルによりエッチングして前駆体15を生成させ、温度制御手段6の調整により基板3に前駆体15を吸着させてから、塩素ガスラジカルにより前記基板に吸着した前駆体15を還元すると共に酸素ガスラジカルにより酸化してSiO2膜とする反応により、アスペクト比の大きい溝にSiO2膜を埋め込む。

(もっと読む)

堆積・エッチングシーケンスを用いたギャップ充填

基板処理チャンバ内に配置された基板上に膜を堆積する方法。該基板は、隣接する隆起した面の間に形成されたギャップを有する。第1の前駆物質堆積ガスのフローが、該基板処理チャンバに提供される。第1の高密度プラズマが、該第1の堆積ガスのフローから形成されて、該ギャップが塞がれるまで、同時に起こる堆積およびスパッタリング要素を有する第1の堆積プロセスによって、該基板上および該ギャップ内に該膜の第1部分を堆積する。該膜の第1の大部分は、該ギャップを再開口するためにエッチバックされる。第2の前駆物質堆積ガスのフローが該基板処理チャンバに供給される。第2の高密度プラズマが、該第2の前駆物質堆積ガスのフローから形成されて、同時に起こる堆積およびスパッタリング要素を有する第2の堆積プロセスによって、該基板上および該再開口されたギャップ内の該膜の第2部分を堆積する。 (もっと読む)

水素シルセスキオキサンを硬化させていき、ナノスケールのトレンチ中において密にさせる方法

半導体基板におけるトレンチが:

(i)フィルム形成材料を、該半導体基板上で、該トレンチ中に分配していき;

(ii)この分配されたフィルム形成材料を、酸化剤存在下に、第1の低温において、第1の予定された期間の時間、硬化させていき;

(iii)この分配されたフィルム形成材料を、酸化剤存在下に、第2の低温において、第2の予定された期間の時間、硬化させていき;

(iv)この分配されたフィルム形成材料を、酸化剤存在下に、第3の高温において、第3の予定された期間の時間、硬化させていき;

(v)満たされた酸化物トレンチを、該半導体基板において、形成させていくこと

により、満たされる。該フィルム形成材料は、水素シルセスキオキサンである。

(もっと読む)

リン含有シラザン組成物、リン含有シリカ質膜、リン含有シリカ質充填材、リン含有シリカ質膜の製造方法及び半導体装置

本発明は、比誘電率3.5以下のリン含有シリカ質材料を提供することを目的とする。本発明によるリン含有シラザン組成物は、有機溶媒中にポリアルキルシラザン及び少なくとも1種のリン化合物を含むことを特徴とするものである。該組成物を基板上に塗布して得られた膜を、温度50〜300℃で予備焼成し、次いで温度300〜700℃の不活性雰囲気中で焼成することにより、リン含有シリカ質膜が得られる。本発明によるリン化合物は、5価のリン酸エステル又はホスファゼン化合物であることが好適である。  (もっと読む)

(もっと読む)

STI構造を有する半導体素子及びその製造方法

【課題】STI構造を有する半導体素子及びその製造方法を提供する

【解決手段】活性領域を定義する上部トレンチと、前記上部トレンチと連通するように前記上部トレンチの下部でラウンド状の断面プロファイルを有する下部トレンチが形成されている半導体基板と、前記半導体基板の上部トレンチ及び下部トレンチ内に形成されている素子分離膜と、を備え、前記素子分離膜は、前記上部トレンチ内にのみ形成され、前記上部トレンチの内壁をスペーサ形態に覆っている第1絶縁膜と、前記第1絶縁膜によって取り囲まれた状態で前記上部トレンチ内に埋め込まれている第2絶縁膜と、前記下部トレンチ内で所定形状のボイドを画定するように、前記下部トレンチの内側壁を覆っている第3絶縁膜と、を備える。

(もっと読む)

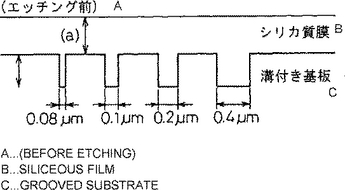

トレンチ埋め込み用組成物及びトレンチ埋め込み方法

【課題】基体に形成されたトレンチ内に酸化シリコンを埋め込むために使用するのに好適なトレンチ埋め込み用組成物及びトレンチ埋め込み方法を提供すること

【解決手段】トレンチ埋め込み用組成物は、(A)酸化シリコン粒子、(B)シリコン原子含有バインダー成分及び(C)溶媒を含有する。

トレンチ埋め込み方法は、トレンチを有する基体上に、上記のトレンチ埋め込み用組成物を塗布し、次いでこれを加熱及び/又は光照射することを特徴とする。

(もっと読む)

プラズマ処理方法および半導体装置の製造方法

【課題】絶縁膜の誘電率の変動や、絶縁膜への水分吸着を抑制することができるプラズマ処理方法および半導体装置の製造方法を提供する。

【解決手段】被処理基板10上の絶縁膜100に、少なくともCH系ガス、CO系ガスのいずれかを含むガスを用いたプラズマ処理を行う。

(もっと読む)

半導体装置の製造方法

【目的】TEOS酸化膜形成後における酸素雰囲気での熱処理による膜質改善効果の及ばない膜厚以上に厚膜や、深いトレンチ構造に酸化膜を埋め込む場合であっても、膜質を改善できる半導体装置の製造方法を提供すること。

【構成】TEOSガスを用いて化学的気相成長法によりTEOS酸化膜を半導体基板上に堆積形成する成膜工程と前記TEOSガスの排気後、酸素ガスを供給して前記TEOS酸化膜上に酸素含有層を積層形成する酸素含有層形成工程との後、前記TEOS酸化膜成膜工程と酸素含有層形成工程とを所要の酸化膜厚さになるまで複数回繰り返す工程と、加熱により前記TEOS酸化膜中に酸素を熱拡散させる工程を備える半導体装置の製造方法とする。

(もっと読む)

半導体装置の製造方法

【課題】CMP工程におけるHDP膜の研磨時間の短縮を図る。

【解決手段】半導体基板1の素子分離領域に分離溝4を形成し、分離溝4の内部を含む半導体基板1上にHDP膜6を成膜し、その後、HDP膜6をCMP法により研磨して分離溝4の外部のHDP膜6を除去することにより素子分離を形成する製造工程において、HDP膜6の成膜をスパッタエッチング/堆積比が0.12から0.22の範囲で実施することにより、HDP膜6の突起を相対的に低くし、さらに、添加剤入りセリアスラリを用いてHDP膜6の突起部を研磨した後、半導体基板1上に純水を供給して希釈された添加剤入りセリアスラリを用いて、残存する分離溝4の外部のHDP膜6を連続的に研磨する。

(もっと読む)

121 - 140 / 146

[ Back to top ]