Fターム[5F064EE56]の内容

ICの設計・製造(配線設計等) (42,086) | 配線 (13,054) | 絶縁、分離 (77)

Fターム[5F064EE56]に分類される特許

1 - 20 / 77

設計支援装置

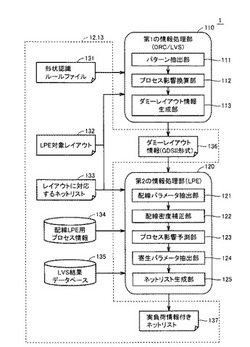

【課題】配線レイアウトのパターン形状に依存した効果をLPEに容易に取込む。

【解決手段】半導体集積回路の設計支援装置は、図形演算機能を有する第1の情報処理部110と、第2の情報処理部120とを備える。第1の情報処理部110は、レイアウト情報に含まれる各配線層のレイアウトパターンに対して図形演算を施すことによって、予め定める特定形状の配線パターンを抽出する。第2の情報処理部120は、製造プロセスに依存した配線または配線層間の絶縁層の厚みの設計値からのずれの大きさを、レイアウト情報から抽出した配線幅および配線密度の情報と、抽出された特定形状の配線パターンに関する情報とに基づいて予測する。そして、第2の情報処理部120は、予測した設計値からのずれの大きさを取り入れた配線および配線層間の絶縁層の厚みに基づいて、配線の寄生パラメータを抽出する。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】シリコン基板1上に絶縁膜2とゲート酸化膜3を設け、ゲート酸化膜2上の一部にヒューズ配線4の両端にヒューズ端子15を有するヒューズを設ける。ヒューズを構成するヒューズ配線4の上方には酸化膜5を介して窒化膜14が形成された凸領域があり、ヒューズ端子15は第1金属配線7と電気的に接続している。

(もっと読む)

プログラマブルロジックデバイス

【課題】電源電圧の供給を停止しても論理回路の結線状態を保持可能なプログラマブルロジックデバイスにおける処理速度の向上及び低消費電力化を図ることを目的の一とする。

【解決手段】論理状態を切り替え可能な複数の演算回路と、演算回路の論理状態を切り替えるコンフィグレーション状態切り替え回路と、演算回路の電源電圧の供給または停止を切り替える電源制御回路と、複数の演算回路の論理状態及び電源電圧の状態を記憶する状態記憶回路と、状態記憶回路の記憶情報に応じて、コンフィグレーション状態切り替え回路及び電源制御回路の制御を行う演算状態制御回路と、を有し、演算回路とコンフィグレーション状態切り替え回路との間に、酸化物半導体層にチャネル形成領域が形成されるトランジスタが設け、電源制御回路からの電源電圧の停止時に該トランジスタの導通状態を保持する。

(もっと読む)

半導体装置

【課題】レーザートリミングの際に半導体基板のダメージを極力抑えながら導電体を溶断することが可能な半導体装置を提供する。

【解決手段】半導体基板10上にLOCOS絶縁膜11を覆う第1の絶縁膜12が形成され、第1の絶縁膜12上には、LOCOS絶縁膜11の平坦部11F上を通って、レーザートリミングにより溶断される導電体20が形成されている。第1の絶縁膜12及び導電体20を覆って、LOCOS絶縁膜11の平坦部11Fと重畳する領域内に凸レンズ状の凸部13Cを有した第2の絶縁膜13が形成されている。レーザートリミングの際、LOCOS絶縁膜11の平坦部11Fの両側の傾斜部11Sでは、レーザー光が半導体基板10の表面に斜めに入射するように反射されるため、半導体基板10のダメージを回避できる。また、第2の絶縁膜13の凸部13Cは、レーザー光を屈折させて導電体20に集光させる。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

不揮発性プログラマブルロジックスイッチおよび半導体集積回路

【課題】回路サイズを減少させることを可能にする。

【解決手段】素子分離領域102によって分離された、隣接する第1導電型の第1半導体領域101aおよび第2導電型の第2半導体領域101cと、第1半導体領域101a上に設けられた不揮発性メモリセルトランジスタ10と、第2半導体領域101c上に設けられ、第1半導体領域101aに設けられた第1ドレイン領域10bと電気的に接続されたゲート電極20C2とを有するパストランジスタ20と、第1半導体領域101aに設けられ第1半導体領域に基板バイアスを印加する第1電極8と、第2半導体領域101cに設けられ第2半導体領域に基板バイアスを印加する第2電極9と、を備えている。

(もっと読む)

半導体装置

【課題】本発明は、工程を増やすこと無く、ヒューズカット時間を短縮することができる半導体装置を提供する。

【解決手段】半導体装置は、ヒューズ配線(10)と、加熱用配線(21、22)とを具備し、ヒューズ配線(10)と加熱配線(21、22)とに電圧を印加してヒューズ配線の溶断部を切断する。ヒューズ配線(10)は、回路素子を形成する配線層と同じ層に形成され、電気的に切断されうる溶断部を備える。加熱用配線(21、22)は、回路素子を形成する配線層と同じ層のうちのヒューズ配線(10)より上層の配線層に絶縁層を介して溶断部を複数回横断するように形成され、溶断部の配線幅より広い配線幅を有して溶断部を加熱する。

(もっと読む)

半導体装置

【課題】電源配線と接地配線とを有する半導体装置において、配線の一部における電圧ドロップや、電圧ドロップに伴うマイグレーションの発生を抑制することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面に沿うように層状に広がる電源シート状配線PPWRと、主表面に沿うように、主表面に交差する方向に関して電源シート状配線と一定の距離を隔てて層状に広がる接地シート状配線PGNDと、上記主表面上に形成され、主表面内の一の方向に延在する電源配線PWRと、主表面上に形成され、一の方向に沿う方向に延在し、電源配線PPWRと一定の距離を隔てて形成された接地配線GNDとを備える。上記電源シート状配線PPWRは、電源配線PWRと電気的に接続されており、接地シート状配線PGNDは、接地配線GNDと電気的に接続されている。

(もっと読む)

高耐圧配線、配線設計装置および方法

【課題】層間絶縁膜を厚くすることなく、放電耐圧を向上させ、デバイスの特性の安定化や性能の向上を図る。

【解決手段】高耐圧配線は、Si基板101上に形成された配線層103と、絶縁膜104と、上層配線105,106と、絶縁膜104に形成された溝107とを有する。配線層103上の絶縁膜104の厚さTは、上層配線105と106間の距離dよりも小さく、溝の幅Wは、距離dよりも小さい。絶縁膜104の厚さTは、配線層103と上層配線105,106との間に与えられる最大の電位差Vmaxよりも絶縁膜104の耐圧が大きくなるように設定され、絶縁膜104の露出量Xは、溝の幅Wと距離dとが等しいときの絶縁膜104に沿った沿面放電開始電圧をV0(V0=b×lnT+c、b,cは定数)としたとき、Vmax<aX+V0(aは定数)となるように設定される。

(もっと読む)

半導体集積回路及びその製造方法

【課題】金属層からなるガードリングで囲まれたトリミング素子形成領域のヒューズ上の保護膜の開口からヒューズ上の層間絶縁膜に浸入した水分等がガードリングに形成されたヒューズ引き出し電極用の開口を通ってデバイス形成領域に浸入することを防止する。

【解決手段】ヒューズ5aを取り囲む第1ガードリング30とその外側の第2ガードリング40に囲まれたヒューズ電極引き出し領域41を形成する。ヒューズ5aと連続し層間絶縁膜6とフィールド酸化膜4の間をヒューズ電極引き出し領域41まで延在するヒューズ電極5と、該ヒューズ電極5と接続する第1ヒューズ引き出し電極7cと、該第1ヒューズ引き出し電極7cと接続する第2ヒューズ引き出し電極9cとを形成し、該第2ヒューズ引き出し電極9cを層間絶縁膜8上に形成された第2ガードリング40を構成する第2電極の開口24を通してデバイス素子形成領域80に引き出す。

(もっと読む)

半導体装置

【課題】RDRに従い設計され、活性領域と電源配線との境界部や周辺部における不具合の発生が抑制された、小型化かつ高集積化された半導体装置を提供する。

【解決手段】少なくとも1つのスタンダードセル内における半導体基板SBの主表面に形成される第1導電型の機能素子用不純物領域Apと、電源電位が印加される第2導電型の電源電位用不純物領域Anとを備える。半導体基板SBの主表面上に形成され、かつ半導体基板SBの主表面に達する貫通孔SCTHを有する絶縁層II1、II2と、絶縁層II1、II2の貫通孔内に形成されたコンタクト用導電層PCLとを備える。上記機能素子用不純物領域Apと電源電位用不純物領域Anとをまたぐように形成されるコンタクト用導電層PCLを通じて電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の平坦性を維持しつつ、配線とインダクタとの間に生じる寄生容量を低減させた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に形成された第1の層間絶縁膜506と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた配線106と、第1の層間絶縁膜506のうち配線形成領域内に位置する部分に埋め込まれた第1のダミーパターン107と、第1の層間絶縁膜506のうちインダクタ領域内に位置する部分に埋め込まれた第2のダミーパターン108と、第1の層間絶縁膜506の上方に形成された第2の層間絶縁膜と、第2のダミーパターン108の上方であって、第2の層間絶縁膜のうちインダクタ領域内に位置する部分に埋め込まれたインダクタ111とを備える。第2のダミーパターン108として金属が形成されていない。

(もっと読む)

半導体装置

【課題】 配線に対するエレクトロマイグレーションの影響を排除する点で、従来の構造は十分とはいえない。

【解決手段】 半導体基板の上に第1の配線が配置されている。半導体基板の上であって、第1の配線とは異なる高さに第2の配線が配置されている。第1のビアが、第1の配線と第2の配線とを高さ方向に接続する。第2のビアが、高さ方向に関して第1のビアとは反対側において第1の配線に接続される。第1の配線は、第1のビアとの接続点から基板面内の第1の方向に延在し、第2のビアは、第1のビアよりも第1の方向にずれた位置に配置されており、第2のビアは、高さ方向に電流を流す電流路として作用しない。

(もっと読む)

電流ヒューズ、半導体装置及び電流ヒューズの切断方法

【課題】ヒューズ部を容易に切断する。

【解決手段】基体上に設けられるヒューズ部20と、前記ヒューズ部20の上層又は前記基体と前記ヒューズ部20の間の下層に配置され、かつ前記ヒューズ部20が通電した際に、前記ヒューズ部20の一部分と同電位となり、前記ヒューズ部20の一部分側から、前記一部分と相違する電位となる前記ヒューズ部20の他の部分の上層又は下層まで延在する導電部16と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上にザッピング素子1のヒューズ層12を形成し、ヒューズ層12を覆う第1の絶縁膜13を形成する。第1の絶縁膜13上にはヒューズ層12を覆うエッチングストッパー膜14を形成し、エッチングストッパー膜14を覆う第2の絶縁膜16を形成する。他の工程を経た後、第1のエッチング工程として、ヒューズ層12上で、第2の絶縁膜16をエッチングストッパー膜14に対して選択的にエッチングすることにより、エッチングストッパー膜14の表面を露出させる。次に、第2のエッチング工程として、ヒューズ層12上で、エッチングストッパー膜14を第1の絶縁膜13に対して選択的にエッチングすることにより、第1の絶縁膜13の表面を露出させる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性を損なうことなく更なる集積化を実現し得る半導体装置を提供する。

【解決手段】第1のトランジスタL1のゲート電極を含み、第1のコンタクト層48aを介して第2のトランジスタL2のソース/ドレイン拡散層20に電気的に接続される、直線状の第1のゲート配線16aと、第2のトランジスタL2のゲート電極を含み、第2のコンタクト層48bを介して第1のトランジスタのソース/ドレイン拡散層22に電気的に接続される、第1のゲート配線と平行な直線状の第2のゲート配線16bと、第1のゲート配線及び第2のゲート配線を覆うように形成された絶縁膜であって、第1のゲート配線と第2のトランジスタのソース/ドレイン拡散層とを露出し、長辺方向が第1のゲート配線の長手方向である第1の開口部46aが形成された絶縁膜と、第1の開口部内に埋め込まれた第1のコンタクト層とを有している。

(もっと読む)

半導体装置

【課題】占有面積を増やすことなくロジック回路領域におけるトランジスタ特性の変動が抑制される半導体装置を提供する。

【解決手段】NMOS領域の素子形成領域4と、この素子形成領域4に隣り合う他の素子形成領域4との間隔(ゲート幅方向)が一定の間隔(距離2×LA)に設定されている。また、この素子形成領域4と、この素子形成領域4に隣り合う素子形成領域8との間隔(ゲート幅方向)も一定の間隔(距離2×LA)に設定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ヒューズのカットばらつきを防ぐとともに腐食(酸化等も含む)を良好に防ぐ。

【解決手段】半導体装置100は、基板102と、基板102上に形成されたヒューズ配線116と、少なくともヒューズ配線116の側壁を保護するように形成された耐湿性絶縁膜120と、を含む。耐湿性絶縁膜120は、ヒューズ配線116の上面には形成されていないか、またはヒューズ配線116の上面における積層方向の膜厚d1がヒューズ配線116の側壁における積層方向に垂直な方向の膜厚d2よりも薄くなるように形成されている。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】開口不良や形状の精度に優れたコンタクトホールを有する半導体素子の提供。

【解決手段】基板4と、基板4上に第1配線パターン2と、基板4の第1配線パターン2を有する側の面に層間絶縁膜6,8と、層間絶縁膜6,8上に第2配線パターンと、を有し、且つ層間絶縁膜6,8に第1配線パターン2および第2配線パターンを連結するためのコンタクトホールCHを備え、基板4の単位面積あたりにおいて第1配線パターン2が存在する比率(密度)が、より高い領域と、より低い領域とを有し、前記比率がより低い領域におけるコンタクトホールCHの開口面積が、より高い領域におけるコンタクトホールCHの開口面積よりも小さい半導体素子。

(もっと読む)

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

1 - 20 / 77

[ Back to top ]