Fターム[5F082BA35]の内容

Fターム[5F082BA35]の下位に属するFターム

Fターム[5F082BA35]に分類される特許

81 - 100 / 192

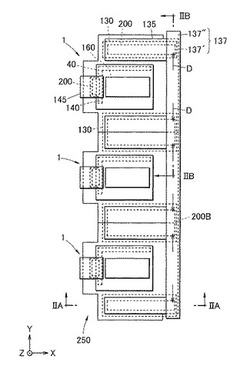

半導体装置および半導体集積回路装置

【課題】半導体集積回路装置の高集積化及び低コスト化を可能にする複数のトランジスタセルを含む半導体装置を提供することを第1の目的とし、高密度に集積化された小型の半導体集積回路装置を安価に提供する。

【解決手段】基板上に、それぞれ第1層、ベース層、及び、第2層を順に有し、前記第1層、及び、前記第2層の一方がコレクタ層であり、他方がエミッタ層であるトランジスタセルを複数含み、前記各トランジスタセルの前記第1層に接続される第1電極が、前記第1層に形成されたエッチング溝に形成された半導体装置において、前記エッチング溝は、その長手方向に沿った側面が順メサ面となっており、複数のトランジスタセル間の前記第1電極が、前記各順メサ面に交差するように設けられた、まとめ配線によって接続される半導体装置である。

(もっと読む)

トランジスタ素子

【課題】HEMTの上にHBTを成長させる際にHEMTの移動度が劣化しないトランジスタ素子を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ(HEMT)3が形成され、該HEMT3上にヘテロバイポーラトランジスタ(HBT)4が形成されたトランジスタ素子1において、上記HEMT3内にバリア層10を有する。

(もっと読む)

半導体装置

【課題】面積の増加を抑制可能なESD保護回路を有する半導体装置を提供する。

【解決手段】入力端子11及び出力端子21を有する高周波信号の処理部と、スパイラルをなして連続したp側領域であるスパイラル状p側領域17、スパイラル状p側領域17と同様形状をなして連続したn側領域であるスパイラル状n側領域19、及びスパイラル状p側領域17とスパイラル状n側領域19とが接合した同様形状のスパイラルをなして連続したpn接合を有し、スパイラルの一端部となるスパイラル状n側領域19の端部が入力端子11に接続され、スパイラルの他端部となるスパイラル状p側領域17の端部が接地端子に接続されたESD保護素子とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数が増加するのを抑制しながら、第1素子のゲート電極および第2素子の電極部のそれぞれの側面を覆うサイドウォール絶縁膜の幅を異ならせることが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域B上にゲート電極28を形成する工程と、シリコン基板11の領域Aにスペーサ絶縁膜42を、ゲート電極28の側面および領域Aを覆うように形成することにより、領域Aを覆う保護膜と、ゲート電極28の側面を覆う絶縁膜42aを形成する工程と、その後、領域A上にエミッタ電極25を形成する工程と、ゲート電極28およびエミッタ電極25を覆うようにシリコン酸化膜49を形成する工程と、スペーサ絶縁膜42およびシリコン酸化膜49をエッチングすることにより、絶縁膜42aを覆う絶縁膜30aを形成するとともに、エミッタ電極25の側面を覆うサイドウォール絶縁膜26を形成する工程とを備える。

(もっと読む)

トランジスタ素子

【課題】電流利得が高いトランジスタ素子を提供する。

【解決手段】基板2上にヘテロバイポーラトランジスタ3が形成され、該ヘテロバイポーラトランジスタ3上に高電子移動度トランジスタ4が形成されたトランジスタ素子1において、上記ヘテロバイポーラトランジスタ3のベース層8の層厚が120nm以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】コレクタ耐圧の低下を防止し、コレクタ抵抗を低減させることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半絶縁性GaAs基板101の第1領域上に形成されたHBTと、半絶縁性GaAs基板101の第2領域上に形成されたHFETとを備え、HBTは、第1領域上に順次形成された、第1導電型のエミッタ層103、エミッタ層103よりバンドギャップの小さい第2導電型のベース層104、第1導電型又はノンドープのコレクタ層105、及びコレクタ層105より高不純物濃度の第1導電型のサブコレクタ層106を有し、HFETは、エミッタ層103の一部により構成された電子供給層110と、電子供給層110の下方に形成されたチャネル層102とを有する。

(もっと読む)

半導体装置

【課題】DAT技術を利用した電力増幅器において、能動素子として高耐圧トランジスタを用いた場合に、その特性を十分に活用することができる技術を提供する。

【解決手段】3個のほぼ等価なプッシュプル増幅器を具備している。プッシュプル増幅器における1対のトランジスタ3A〜3Fのドレインは、金属配線1A〜1Hから成る電流経路により相互に接続され、電流経路の中間点が正電源Vddに接続されている。金属配線1A〜1Hのうちトランジスタのドレインからその正電源Vddに至る部分が1本の1次コイルを構成する。1次コイルが、それらと近接して配置された金属配線2から成る2次コイルと磁気的に結合することにより、1次コイルからの出力を合成し2次コイルの出力端子から出力する。1本の1次コイルに相当する金属配線の長さに対する、2次コイル全体に相当する金属配線の長さの比が、およそ3である。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の第2素子が形成される領域にエッチングによるダメージが発生するのを抑制しながら第1素子のゲート電極の側面を覆うサイドウォール絶縁膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の電界効果型トランジスタ2が形成される領域にゲート電極28を形成する工程と、ゲート電極28の表面およびシリコン基板11のバイポーラトランジスタ1が形成される領域を覆うようにスペーサ絶縁膜42を形成する工程と、スペーサ絶縁膜42を表面から所定の厚み分エッチングすることにより、シリコン基板11のバイポーラトランジスタ1が形成される領域にスペーサ絶縁膜42を所定の厚み分残した状態でゲート電極28の側面を覆うサイドウォール絶縁膜30を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】第1素子の第1電極の表面上に形成される第1絶縁膜を除去する際に、素子分離絶縁膜の端部が除去されることに起因する不都合が発生するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、バイポーラトランジスタ1が形成される領域Aに隣接するように素子分離絶縁膜16bを形成する工程と、エミッタ電極25の表面上にシリコン窒化膜47aを形成する工程と、領域Aに不純物を注入する工程と、少なくとも素子分離絶縁膜16bがスペーサ絶縁膜42により覆われた状態でシリコン窒化膜47aを除去する工程と、シリコン窒化膜47aが除去された後に領域Aおよび素子分離絶縁膜16bを覆うようにシリコン窒化膜を形成する工程とを備える。

(もっと読む)

第二のポリ層の形成後に二重ポリバイポーラトランジスタの2つのレベルをドーピングするプロセス

【課題】

単結晶半導体材料よりエミッタドーパントに対して少なくとも1桁大きい材料の層の速い横方向拡散特性を用いる減少されたマスクの組とインプラントの複雑さを有する(高周波数応用)相補的バイポーラトランジスタ構造の製造プロセスを提供する。

【解決手段】

別のベースとエミッタポリ層がドープされずに形成される。それからあるデバイスのエミッタポリと他のデバイスのベースポリのエッジとはドーパントマスクを介して露出され、同時にドープされる。エミッタドーパントはエミッタポリの表面内に直接入り、ここでそれはベース上に位置し、それと接触している。ベース接触ドーパントは外因性ベースを形成するために高い拡散係数を有する材料の層を含むベースポリのエッジ内に入り、その層を通り抜けて迅速に横方向に拡散し、それからコレクタ材料(例えばアイランド)表面内に下方に拡散する。第二のマスクは第二のデバイスのエミッタと第一のデバイスのベースポリのエッジを露出するようパターン化され、それからドープされる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の耐湿性向上を図ることができる技術を提供する。

【解決手段】半絶縁性基板であるGaAs基板40において、素子形成領域にHBT30を形成し、絶縁領域に素子分離領域47を形成する。絶縁領域に形成される素子分離領域47は、HBT30のサブコレクタ用半導体層41とコレクタ用半導体層42と同層の半導体層にヘリウムを導入することにより形成されている。外周領域において、保護膜52、55から露出するように導電層49を形成し、この導電層49を裏面電極と接続する。裏面電極にはGND電位が供給されるので、導電層49はGND電位に固定される。この導電層49は、HBT30のサブコレクタ用半導体層41とコレクタ用半導体層42と同層の半導体層により形成される。

(もっと読む)

BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタ

【課題】BICMOS統合のために選択的エピタキシャル成長を用いる、隆起した外因性自己整合型ベースを有するバイポーラ・トランジスタを提供する。

【解決手段】隆起した外因性自己整合型ベースを有する高性能バイポーラ・トランジスタが、CMOSデバイスを含むBiCMOS構造と統合される。パッド層を形成して、先在するCMOSデバイスのソースおよびドレインに対して真性ベース層の高さを隆起させることにより、かつ選択的エピタキシを介して外因性ベースを形成することにより、表面の凹凸の影響は、外因性ベースのリソグラフィによるパターン形成時に最小になる。また、バイポーラ構造の製作の間に、化学機械研磨プロセスを使用しないことにより、プロセス統合の複雑さが軽減される。内側のスペーサまたは外側のスペーサが、エミッタからベースを分離するために形成されうる。パッド層、真性ベース層、および外因性ベース層は、一致した外側の側壁表面を有するメサ構造を形成する。

(もっと読む)

差動電流モード伝送回路

【課題】高周波特性が良好で、出力段の耐圧が高い差動電流モード伝送回路を提供する。

【解決手段】Si−BJT(接合型バイポーラシリコントランジスタ)を用いて構成された第一のバッファ3と、SiGeHBT(シリコン−ゲルマニウムへテロ接合型バイポーラトランジスタ)、またはSiGeHBTとSi−BJT、またはSiGeHBT、シリコンMOSFETおよびSi−BJTを用いて構成された信号処理回路4と、SiGeHBTとSi−BJT、またはSiGeHBTとシリコンMOSFETを用いて構成された最終段の第二のバッファ5とを備え、第一のバッファ、信号処理回路および第二のバッファが、同一半導体チップに集積される。

(もっと読む)

半導体装置

【課題】半導体装置に含まれるESD保護トランジスタのESD耐性を向上できるようにする。

【解決手段】半導体装置は、ウェル領域101の上に形成されたゲート電極103と、ウェル領域101におけるゲート電極103のゲート長方向側にそれぞれ形成されたドレイン領域104及びソース領域105と、ドレイン領域104の上で且つゲート電極103のゲート幅方向に互いに間隔をおいて形成された複数のドレインコンタクト106A〜106Cと、ソース領域105の上で且つゲート電極103のゲート幅方向に互いに間隔をおいて形成された複数のソースコンタクト107A〜107Eとを有している。隣り合うドレインコンタクト同士の間隔は、隣り合うソースコンタクト同士の間隔よりも大きい。

(もっと読む)

バイポーラトランジスタ装置

【課題】LCRを外付け可能で、汎用性が高く容量、抵抗及びインダクタンスを自由に調整することができ、さらなる高周波領域での要求に耐え得るバイポーラトランジスタ装置を提供する。

【解決手段】半導体素子搭載部と、前記半導体素子搭載部の相対向する2辺に沿って配列された複数のリードとを具備したリードフレームと、バイポーラトランジスタと、前記バイポーラトランジスタに接続された回路要素とが搭載され、高周波信号入力端子を構成する入力パッドと高周波信号出力端子を構成する出力パッドとが相対向する辺上に、相対向するように配列され、前記半導体素子搭載部に搭載されると共に電気的接続のなされた半導体素子と、前記素子搭載部に搭載された前記半導体素子を覆うとともに、前記リードの先端を導出するように形成された封止体とを備え、前記半導体素子搭載部と前記リードのひとつとが一体的に形成されたことを特徴とする。

(もっと読む)

ホットエレクトロントランジスタおよびそれを含む半導体装置

【課題】期待される高周波特性を得ること、ならびに後続の回路で必要とされる駆動電流を得ることが可能なホットエレクトロントランジスタを提供する。

【解決手段】このホットエレクトロントランジスタ100は、コレクタ層3と、ベース層5と、エミッタ層7と、コレクタ層3とベース層5との間に形成されたコレクタバリア層4と、ベース層5とエミッタ層7との間に形成されたエミッタバリア層6とを備えている。そして、エミッタバリア層6とエミッタ層7との間のエネルギー障壁は実質的に存在しないとともに、コレクタバリア層4のエネルギー障壁の高さはエミッタバリア層6のエネルギー障壁の高さよりも低い。

(もっと読む)

HBTと電界効果トランジスタとの統合

2つの別個の成長過程を用いて統合BiFETを製作するための方法及びシステムを開示する。本発明を実施すると、BiFETのFET部分が第1製作環境で製作される。本発明を実施すると、BiFETのHBT部分が第2製作環境で製作される。FET部分とHBT部分の製作を2つ以上の別々の反応器内に分離することで、最適な装置性能が両方の装置で達成される。  (もっと読む)

(もっと読む)

半導体装置

【課題】バイポーラトランジスタを用いたESD保護回路の面積効率を向上する。

【解決手段】集積回路は、回路用バイポーラトランジスタ124を含む内部回路121と、内部回路121をサージから保護するための保護用バイポーラトランジスタ120とを備え、保護用バイポーラトランジスタ120におけるエミッタとベースとは短絡されている。

(もっと読む)

接合型電界効果トランジスタ及びその製造方法及び半導体装置

【課題】コレクタエピタキシャル層を薄膜化した高速バイポーラトランジスタを搭載した集積回路中に所望の高耐圧J−FETを混載可能とした半導体装置及びその製法を提供すること。

【解決手段】P型の単結晶Si基体などの第1導電型の半導体基体2上にシリコン半導体層などの第2導電型の半導体層3を積層し、この半導体層3中にAs(ヒ素)等の第2導電型の不純物によってソース領域12及びドレイン領域13を形成し、さらにこの半導体層3上に、シリコン・ゲルマニウム層によってP型の第1導電型不純物(例えば、ホウ素など)を有するゲート領域14を形成する。

(もっと読む)

半導体装置

【課題】正孔の移動を十分に抑制することが可能な半導体装置を提供する。

【解決手段】この半導体装置(npn型のバイポーラトランジスタ100)は、n型コレクタ層2と、p+拡散層4、SiGe層5およびp型シリコン膜6からなるベース層と、n型エミッタ層8と、n型コレクタ層2とn型エミッタ層8との間に形成され、電子または正孔のいずれか一方に対する電位障壁としての効果を有する電荷移動防止膜7とを備える。

(もっと読む)

81 - 100 / 192

[ Back to top ]