Fターム[5F083AD02]の内容

Fターム[5F083AD02]に分類される特許

161 - 180 / 416

電界効果トランジスタおよびそれを用いたメモリおよび半導体回路

【課題】微細化した半導体集積回路において用いられる、オフ電流の小さな電界効果トランジスタ(FET)を提供する。

【解決手段】絶縁表面に略垂直に形成された厚さが1nm以上30nm以下の薄片状の酸化物半導体と、前記酸化物半導体を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜を覆って形成されたストライプ状の幅10nm以上100nm以下のゲートを有する電界効果トランジスタ。この構成では、薄片状の酸化物半導体の三方の面をゲートが覆うこととなるため、ソース、ドレインから注入される電子を効率的に排除し、ソースとドレインの間をほぼ空乏化領域とでき、オフ電流を低減できる。

(もっと読む)

半導体装置および該半導体装置の作製方法

【課題】良好な電気特性を有する半導体装置および該半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に水素透過膜を形成し、水素透過膜上に水素捕縛膜を形成し、加熱処理を行って、酸化物半導体膜から水素を脱離させ、酸化物半導体膜の一部に接するソース電極およびドレイン電極を形成し、水素捕縛膜の露出されている部分を除去して、水素透過膜のチャネル保護膜を形成する半導体装置の作製方法である。また、該作製方法で作製された半導体装置である。

(もっと読む)

酸化物半導体膜、半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を活性層に用いるトランジスタにおいて、チャネル領域と隣接するソース領域およびドレイン領域に微小な空洞を設ける。酸化物半導体膜に形成されるソース領域およびドレイン領域に微小な空洞を設けることによって、微小な空洞に酸化物半導体膜のチャネル領域に含まれる水素を捕獲させることができる。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上より、第2の絶縁膜3が設けられていない領域上に延在して選択的に半導体層(6、7、8)が設けられ、半導体層の一部7の全周囲にゲート絶縁膜14を介し、第1の絶縁膜2上に包囲構造のゲート電極15が選択的に設けられ、ゲート電極15に自己整合し、直下に空孔を有する半導体層の一部8及び残りの半導体層の一部6にソースドレイン領域(10、11、12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域11上に電荷蓄積電極17が設けられ、電荷蓄積電極17の側面及び上部にはキャパシタ絶縁膜19を介してセルプレート電極(対向電極)20が設けられた構造のスタック型キャパシタとにより構成されたDRAM。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、少なくとも酸化物半導体膜中に希ガスイオンを注入する注入工程を行い、減圧下、窒素雰囲気下、又は希ガス雰囲気下において、希ガスイオンを注入した酸化物半導体膜に加熱工程を行って希ガスイオンを注入した酸化物半導体膜中に含まれる水素若しくは水を放出させ、酸化物半導体膜を高純度化する。

(もっと読む)

半導体記憶装置

【課題】SOI構造のDRAMの提供

【解決手段】

半導体基板1上に複数層の絶縁膜(2、3、4、5)が選択的に設けられ、絶縁膜5上より、絶縁膜5が設けられていない領域上に延在して選択的に半導体層(8、9、10)が設けられ、半導体層の一部9の全周囲にゲート絶縁膜16を介し、絶縁膜4上に包囲構造のゲート電極17が設けられ、ゲート電極に自己整合し、直下に空孔7を有する半導体層の一部10にドレイン領域(14、15)が、半導体層の一部8にソース領域(12、13)が設けられた構造のMIS電界効果トランジスタと、ソース領域12の側面に一部を接し、絶縁膜(3、5)中にトレンチが設けられ、トレンチの側面に電荷蓄積電極19が設けられ、電荷蓄積電極の側面及び上部にキャパシタ絶縁膜20を介してセルプレート電極21が設けられた構造のトレンチ型キャパシタと、により構成されたDRAM。

(もっと読む)

記憶装置及び電子機器

【課題】メモリセル毎に選択動作を行う。

【解決手段】装置は、第1のメモリセルと、第1のメモリセルと同じ行に設けられた第2のメモリセルと、を具備し、前記第1及び第2のメモリセルのそれぞれは、第1のゲート及び第2のゲートを有し、オン状態又はオフ状態になることにより、メモリセルにおける少なくともデータの書き込み及びデータの保持を制御する電界効果トランジスタを備え、前記第1のメモリセル及び前記第2のメモリセルが備える前記電界効果トランジスタの前記第1のゲートのそれぞれに電気的に接続される行選択線と、前記第1のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第1の列選択線と、前記第2のメモリセルが備える前記電界効果トランジスタの前記第2のゲートに電気的に接続される第2の列選択線と、をさらに具備する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、酸化物半導体膜に酸素ドープ処理を行い、その後、酸化物半導体膜及び酸化物半導体膜上に設けられた酸化アルミニウム膜に対して熱処理を行うことで、化学量論的組成比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を介して対向する一対の第2の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられるゲート絶縁膜と、ゲート絶縁膜上に設けられて、かつ第1の領域に重畳する第1の電極と、を有し、第1の領域は、c軸配向した結晶部を有する非単結晶の酸化物半導体領域であり、一対の第2の領域は、ドーパントを含んで、かつ複数の結晶部を有する酸化物半導体領域であることを特徴とする半導体装置である。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

半導体記憶装置

【課題】集積度が高く、データ保持時間の長い半導体記憶装置。

【解決手段】基板上の半導体膜と、半導体膜を覆う第1のゲート絶縁膜と、第1のゲート絶縁膜を介して半導体膜上に設けられた第1のゲート電極と、第1のゲート絶縁膜上にあり、半導体膜と重畳しない、第1のゲート電極と同一層かつ同一材料である第1の導電膜と、第1のゲート絶縁膜上にあり、第1のゲート電極および第1の導電膜の上面を露出し、第1のゲート電極および第1の導電膜の間に溝部を有する絶縁膜と、該絶縁膜上にあり、第1のゲート電極、第1の導電膜および溝部と接する酸化物半導体膜と、酸化物半導体膜を覆う第2のゲート絶縁膜と、第2のゲート絶縁膜を介して酸化物半導体膜および溝部上に設けられた第2のゲート電極と、第2のゲート絶縁膜および酸化物半導体膜を介して第1のゲート電極上に設けられた、第2のゲート電極と同一層かつ同一材料である第2の導電膜と、を有する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】しきい値電圧の制御が困難な酸化物半導体を活性層に用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】一対の第1の領域、一対の第2の領域及び第3の領域を有する酸化物半導体膜と、酸化物半導体膜と接して設けられる一対の電極と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介し、一対の電極の間に設けられたゲート電極と、を有し、一対の第1の領域は一対の電極と重畳し、第3の領域はゲート電極と重畳し、一対の第2の領域は一対の第1の領域及び第3の領域の間に形成され、一対の第2の領域及び第3の領域には窒素、リン、または砒素のいずれかの元素が含まれており、該元素の濃度は、第3の領域より一対の第2の領域のほうが高い構成とする。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の作製方法

【課題】高度に集積化したゲインセル方式の半導体メモリを提供する。

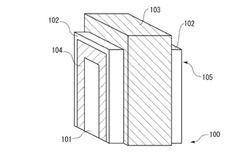

【解決手段】第1絶縁体101、読み出しビット線102b、第2絶縁体103、第3絶縁体103、第1半導体膜105、第1導電層107a乃至107d等を形成し、その上に凸状絶縁体112を形成する。そして、凸状絶縁体112を覆って、第2半導体膜114a、114bと第2ゲート絶縁膜115を形成する。その後、導電膜を形成し、これを異方性エッチングすることで、凸状絶縁体112の側面に書き込みワード線116a、116bを形成し、凸状絶縁体112の頂部に書き込みビット線125へ接続するための第3コンタクトプラグ124を形成する。このような構造でメモリセルの面積を最小で4F2とできる。

(もっと読む)

161 - 180 / 416

[ Back to top ]