Fターム[5F083AD15]の内容

Fターム[5F083AD15]の下位に属するFターム

基板ストレージノードトレンチ型 (33)

基板セルプレートトレンチ型 (104)

スタックトトレンチ型 (11)

トレンチ素子分離と併合 (13)

1cell/1island形式 (1)

Fターム[5F083AD15]に分類される特許

1 - 20 / 59

酸化ルテニウム膜の成膜方法

半導体メモリ装置およびその駆動方法

【課題】容量素子の容量を低減し、また、集積度の高い半導体メモリ装置を提供する。

【解決手段】1つのビット線BL_mに複数個のメモリブロックを接続させる。メモリブロックMB_n_mはサブビット線SBL_n_mと書き込みスイッチと複数のメモリセルを有する。サブビット線SBL_n_mと隣接するサブビット線SBL_n+1_mは2つのインバータと2つの選択スイッチよりなる増幅回路AMP_n/n+1_mに接続し、増幅回路は選択スイッチによりその回路構成を変更できる。また、増幅回路は読み出しスイッチを介してビット線BL_mに接続する。サブビット線SBL_n_mの容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n/n+1_mでエラーなく増幅でき、ビット線BL_mに出力できる。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

補助電極構造を備えた立体型DRAM

【課題】補助電極構造を備えた立体型DRAMの提供。

【解決手段】本補助電極構造を備えた立体型DRAMは、基板(10)、該基板(10)上に形成された少なくとも一つのビット線(11)、該ビット線(11)上の成長領域(111)に形成された柱状体(20)、補助電極(40)、該基板(10)に平行で且つ該ビット線(11)に垂直なワード線(60)、該柱状体(20)に接続されたコンデンサ(70)を包含し、該ビット線(11)は該基板(10)にドーパントをドープし並びに拡散を実行して形成され、該補助電極(40)は該ビット線(11)の間隔領域(112)に設置され、並びに該柱状体(20)に隣接し、該ワード線(60)は該補助電極(40)と絶縁されて設置され、並びに該ビット線(11)と組み合わされて該コンデンサ(70)に電子データを入出力する。本発明は該補助電極(40)の設置により、該ビット線(11)の抵抗を制御できるようにすることで、該ビット線(11)の導電能力を向上する。

(もっと読む)

半導体装置

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタがオン・オフするのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。また、トランジスタの微細化を進めて集積化を図っても、メモリ容量を増加させるためには、半導体装置の面積が大きくなるといった問題があった。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。また、トレンチ構造の酸化物半導体を有するトランジスタにより、半導体装置の記憶素子を構成し、該記憶素子を複数積層することで、半導体装置の回路面積を縮小することができる。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

成膜方法、成膜装置および記憶媒体

【課題】DRAMキャパシタの誘電体膜に求められる高誘電率化および低リーク電流化を両立させることができる、酸化ジルコニウム膜を含む誘電体膜の成膜方法および成膜装置を提供すること。

【解決手段】 酸化ジルコニウム膜を含む誘電体膜を成膜する成膜方法は、シクロペンタジエニル環を構造中に含むZr化合物からなるジルコニウム原料と酸化剤とを供給して被処理基板上に酸化ジルコニウム膜を成膜する工程と、シクロペンタジエニル環を構造中に含むチタン化合物からなるチタン原料と酸化剤とを供給して前記酸化ジルコニウム膜の上に酸化チタン膜を成膜する工程とを有する。

(もっと読む)

集積回路とその方法

【課題】標準/低温処理技術と適合しキャパシタンスの密度を向上させる多層構造で使用されるCMPと適合性を有するキャパシタ構造を提供する。

【解決手段】キャパシタ構造体は、集積回路の誘電体層の開口101内に形成される。下部電極層102は、開口101の側面表面の少なくとも一部の上にのびるが、誘電体層405の上部表面までにはのびていない。誘電体材料層405が、この下部電極102の上と、集積回路誘電体層203の上部表面の上に配置される。最後に上部電極層406が、この誘電体材料層405の上に形成される。上部電極層406と下部電極層102のオーバーラップは存在せず、平面化プロセスの間発生することのある短絡の問題を回避できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

キャパシタおよび半導体装置

【課題】微細化した半導体集積回路において用いられるキャパシタを提供する。

【解決手段】誘電体の一つの面に接して設けられた、インジウム、錫あるいは亜鉛の少なくとも一つと窒素とを有する仕事関数が5.0電子ボルト以上、好ましくは5.5電子ボルト以上のn型半導体による電極を有するキャパシタである。電極の仕事関数が高いため、誘電体のポテンシャル障壁が高くなり、誘電体が10nm以下と薄くても十分な絶縁性を保てる。特に、誘電体が、high−k材料である場合に顕著な効果が認められる。

(もっと読む)

気化装置及び成膜装置

【課題】液体ソースを気化して成膜処理に用いられる処理ガスを得るにあたり、気化量を安定させ、かつ処理ガス濃度を高めること。

【解決手段】液体ソースを貯留するための気化室3の天井部に面接触した状態で、毛細管現象により液体ソースが広がる繊維体からなる面状体41を設ける。また、一端側が前記面状体41に接続され、他端側が前記気化室3内の液体ソースに接触するように、前記液体ソースを毛細管現象により吸い上げて面状体41に供給する吸い上げ部42を設ける。気化室3を加熱することにより、面状体41が加熱され、液体ソースが液面から気化すると共に、面状体41の表面からも気化するので、処理ガス濃度を高めることができる。また、吸い上げ部42のみが液体ソースに接触しているので、液面の高さ位置が変動しても、面状体への液体ソースの拡散状態に影響がなく、安定した気化量を確保することができる。

(もっと読む)

半導体メモリ装置および半導体メモリ装置の駆動方法

【課題】消費電力の少ない新規の半導体メモリ装置を提供する

【解決手段】書き込みトランジスタWTr_n_mのソースと読み出しトランジスタRTr_n_mのゲートとキャパシタCS_n_mの一方の電極を接続し、書き込みトランジスタWTr_n_mのゲートとドレインを、それぞれ書き込みワード線WWL_nと書き込みビット線WBL_mに、キャパシタCS_n_mの他方の電極を読み出しワード線RWL_nに、読み出しトランジスタRTr_n_mのドレインを読み出しビット線RBL_mに接続した構造とする。ここで、読み出しビット線RBL_mの電位はフリップフロップ回路FF_mのような反転増幅回路に入力され、反転増幅回路によって反転された電位が書き込みビット線WBL_mに出力される構造とする。

(もっと読む)

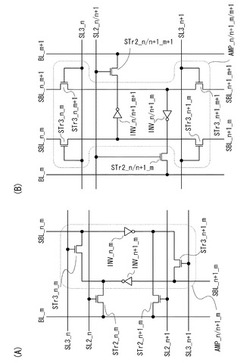

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは容量素子の容量を減らすと、データの読み出しエラーが発生しやすくなる。

【解決手段】1つのビット線MBL_mに複数個のセルを接続させる。各セルはサブビット線SBL_n_mと4乃至64個のメモリセル(CL_n_m_1、等)を有する。さらに各セルは選択トランジスタSTr1_n_mとSTr2_n_mを有し、また、選択トランジスタSTr2_n_mには相補型インバータ等の増幅回路AMP_n_mを接続する。サブビット線SBL_n_mの寄生容量は十分に小さいため、各メモリセルの容量素子の電荷による電位変動を増幅回路AMP_n_mでエラーなく増幅でき、ビット線に出力できる。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

多層ウェーハ中のトレンチ構造

【課題】バーズビーク効果を軽減することのできる、SOIウェーハ内にトレンチを製造する方法を提供すること。

【解決手段】本発明は、基板と、基板上の酸化物層と、酸化物層上の半導体層とを備える多層ウェーハ内にトレンチ構造を製造する方法に関し、本方法は、半導体層および酸化物層を貫通して基板中へ延在するトレンチを形成するステップと、トレンチの内部表面において、半導体層のいくらかの材料が、トレンチの内部表面に露出した酸化物層の部分の一部の上に少なくとも流れるように、形成されたトレンチのアニール処理を行うステップとを含む。

(もっと読む)

半導体装置、および半導体装置の制御方法

【課題】より安定した内部電圧を素子に供給可能にした半導体装置を提供する。

【解決手段】内部電圧で動作する主回路と、内部電圧を生成して主回路に配線を介して供給する内部電圧生成部と、第1および第2の電極を備え、第2の電極が接地線に接続された複数の容量素子と、複数の容量素子のそれぞれに対応して設けられ、本体に電源が投入されると、容量素子が内部電圧の補償容量として機能するか否かを判定し、容量素子が補償容量として機能すると判定すると、容量素子の第1の電極を上記配線に接続する分離部とを有する。

(もっと読む)

半導体デバイスの製造方法および半導体デバイス

【課題】下地膜の結晶性の影響を抑え、高誘電率の結晶構造としたキャパシタ絶縁膜とする。

【解決手段】基板200の上に形成された結晶質膜310の上に非晶質膜320を形成する非晶質膜形成工程と、非晶質膜320の上に結晶質膜310の結晶構造とは独立して制御される結晶構造を持つ絶縁膜330を形成する結晶性絶縁膜形成工程と、を有する。結晶性絶縁膜形成工程においては、基板200を加熱して前記絶縁膜330の少なくとも一部を正方晶系へ相転移させる相転移工程と、を有する。

(もっと読む)

電界効果型トランジスタ、半導体メモリ、表示素子、画像表示装置及びシステム

【課題】比誘電率が高くリーク電流の少ない絶縁膜を提供する。

【解決手段】基板と、前記基板上に形成されたソース電極、ドレイン電極、及びゲート電極と、前記ゲート電極に所定の電圧を印加することによりソース電極とドレイン電極との間にチャネルが形成される半導体層を有し、前記ゲート電極と前記半導体層の間にゲート絶縁層と、を備え、前記ゲート絶縁層は、アルカリ土類金属の中から選ばれた1または2種類以上の元素と、Ga、Sc、Y、及びCeを除くランタノイドの中から選ばれた1または2種類以上の元素とを含むアモルファス複合金属酸化物絶縁膜により形成されていることを特徴とする電界効果型トランジスタを提供することにより上記課題を解決する。

(もっと読む)

誘電体膜をパッシベーションする方法

塩素、臭素又はヨウ素と反応しやすい誘電体材料にフッ素を含むパッシベーション層を堆積する方法が本明細書に開示される。パッシベーション層は、反応しやすい誘電体層を保護することができ、それにより、パッシベーション層に塩素、臭素又はヨウ素を含む前駆体を用いて堆積が可能となる。 (もっと読む)

1 - 20 / 59

[ Back to top ]