Fターム[5F083BS17]の内容

半導体メモリ (164,393) | SRAM (3,190) | 駆動トランジスタ (792) | 構造 (444) | ソース/ドレイン構造 (210) | LDD(Lightly Doped Drain) (149)

Fターム[5F083BS17]に分類される特許

101 - 120 / 149

半導体装置及びその製造方法

【課題】SRAM部とロジック部とを有する半導体装置において、SRAM部用n型MISトランジスタとSRAM部用p型MISトランジスタとの素子分離間隔を拡大させることなく、SRAM部用n型MISトランジスタ及びSRAM部用p型MISトランジスタの各々のトランジスタ特性を確保する。

【解決手段】SRAM部とロジック部とを有する半導体装置であって、SRAM部での半導体基板100上における第1の素子形成領域に、第1のゲート絶縁膜104を介して形成された第1のn型ゲート電極108Bを有する第1のn型MISトランジスタと、ロジック部での半導体基板100上における第2の素子形成領域に、第2のゲート絶縁膜105を介して形成された第2のn型ゲート電極109Bを有する第2のn型MISトランジスタとを備え、第1のn型ゲート電極108Bの第1の不純物濃度は第2のn型ゲート電極109Bの第2の不純物濃度と比較して低い。

(もっと読む)

データ記憶回路用非対称性トランジスタ

ソース(30)の抵抗がドレイン(40)よりも高いトランジスタ(22)は、記憶回路(10)におけるプル・アップ素子(20)として最適である。トランジスタは、ソース抵抗を有するソース注入を備えたソース領域を有している。ソース領域はサリサイド化されない。トランジスタの電気伝導を制御するため、制御電極領域(50)がソース領域に隣接している。ドレイン領域(40)は、制御電極領域に隣接すると共に、ソース領域とは反対側に設けられている。ドレイン領域は、ドレイン抵抗を有しサリサイド化されたドレイン注入を有している。ソース領域の物理特性はドレイン領域とは異なるため、ソース抵抗はドレイン抵抗よりも高くなっている。  (もっと読む)

(もっと読む)

半導体装置

【課題】nチャネルMISFETのソースおよびドレインにニッケルまたはニッケル合金のシリサイド領域を形成する場合であっても、オフリーク電流が増加しにくい半導体装置を実現する。

【解決手段】ソースおよびドレイン上にニッケルまたはニッケル合金のシリサイド領域が形成されたnチャネルMISFETのチャネル長さ方向を、半導体基板の結晶方位<100>に平行となるよう配置する。結晶方位<100>の方向には、ニッケルまたはニッケル合金のシリサイド領域は延伸しにくいため、nチャネルMISFETのソースおよびドレインにニッケルまたはニッケル合金のシリサイド領域を形成する場合であっても、オフリーク電流が増加しにくい半導体装置が得られる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】例えば全体の製造コストを低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置200は、半導体基板110と、ポリシリコン層30と、サイドスペーサ40と、第1シリサイド層262と、第2シリサイド層263と、金属膜261とを備える。半導体基板110は、拡散層14を有する。ポリシリコン層30は、半導体基板110の上において、拡散層14の付近に形成されている。サイドスペーサ40は、半導体基板110の上において、拡散層14とポリシリコン層30との間に形成されている。第1シリサイド層262は、拡散層14の上に自己整合的に形成されている。第2シリサイド層263は、ポリシリコン層30の上に自己整合的に形成されている。金属膜261は、第1シリサイド層262と第2シリサイド層263とを接続するように連続して延びている。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルにおいて、トランジスタのデバイス特性における非対称性不良を抑制する。

【解決手段】半導体装置は、入出力がクロスカップルするように接続され、ドライバトランジスタ及びロードトランジスタよりなるインバータの対と、インバータの対の各出力に接続されたアクセストランジスタの対とを含むSRAMセルを備える。インバータの対を構成するドライブトランジスタの対及びロードトランジスタの対、並びにアクセストランジスタの対のうちの少なくと1つのトランジスタの対は、ソースからドレインへの向きが互いに同じ向きになるように配置されている。

(もっと読む)

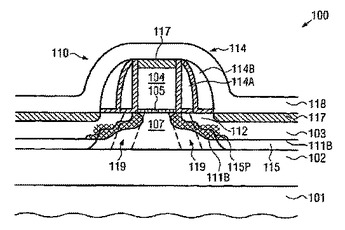

ボディポテンシャルが低減したSOIトランジスタとその製造法

炭素、フッ素などの原子種(111B)をドレイン及びソース領域(115、206)とボディ領域(107、207)とに導入することで、SOIトランジスタ(110、210M)の接合部のリークが著しく増加し、これにより、蓄積した少数電荷キャリアに対してリークパス(119、219A)が強化される。これにより、ボディポテンシャルの変動が著しく減り、その結果、最新のSOIデバイス(100)の全体のパフォーマンスが向上する。具体的な実施形態では、このメカニズムは、スタティックRAM領域(250M)などのしきい値電圧にセンシティブなデバイス領域に選択的に適用することができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】エクステンション領域がゲート電極の下側に広がることがなく且つシェアードコンタクトを形成する際に接合リーク電流が発生するおそれがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10における素子分離領域11に囲まれた部分に形成された活性領域12と、活性領域12の上に形成されたゲート絶縁膜21A及び第1のゲート電極膜22Aを有する第1のゲート構造23Aと、第1のゲート構造23Aの側面上に形成され、第1のゲート構造23Aよりも高さが低い第1のオフセットスペーサ24Aと、第1のゲート構造23Aの側面上に、第1のオフセットスペーサ24Aの側面及び上端面を覆うように形成された第1のサイドウォール25Aとを備えている。

(もっと読む)

半導体集積回路装置

【課題】SRAMのメモリセルの蓄積ノード容量を増やしてソフトエラー耐性を向上させる。

【解決手段】6個のMISFETでメモリセルを構成した完全CMOS型のSRAMにおいて、メモリセルの駆動用MISFETQd1,Qd2、転送用MISFETQt1,Qt2および負荷用MISFETQp1,Qp2のそれぞれのゲート電極を構成する第1導電層の上層に形成した高融点金属シリサイド層でCMOSインバータの相互の入出力端子間を接続する一対の局所配線L1,L2を形成し、この局所配線L1,L2の上層に形成した基準電圧線を局所配線L1,L2と重なるように配置して蓄積ノード容量素子を形成する。局所配線L1,L2の一方は、この蓄積ノード容量素子の一方の電極を構成する。

(もっと読む)

半導体装置の製造方法

【課題】SRAMやシステムLSIに搭載されるオンチップメモリ、マイクロプロセッサ、あるいは、システムLSIで用いられるMOSトランジスタのゲートトンネルリーク電流やGIDL電流を低減する半導体装置の製造方法を提供する。

【解決手段】Nチャネル型の第1と第2MISトランジスタとを有する製造方法において、第1MISトランジスタを形成する第1P型ウエル210と、第2MISトランジスタを形成する第2P型ウエル212を形成する工程と、第1と第2P型ウエル上にゲート絶縁膜221と、ゲート電極230、233、234を形成する工程と、第1P型ウエル210に燐を注入する工程と、第2P型ウエル212に砒素を注入する工程と、第1と第2P型ウエルにそれぞれ燐と砒素を注入する工程後、ゲート電極の側壁膜を形成する工程と、ゲート電極の側壁膜を形成する工程後、第1と第2P型ウエル212に砒素を注入する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】集積回路を形成するパターンの微細化により、チップ面積の縮小を図った半導体装置の製造方法を提供することを目的とする。例えば、薄膜トランジスタで形成され、ICカードまたはICタグの用途として提供されるICチップの縮小を目的とする。

【解決手段】ゲート電極を形成する工程、前記ゲート電極上に絶縁層を形成する工程、絶縁層を貫通する開口部を形成する工程を含み、ゲート電極を形成する工程と絶縁層を貫通する開口部を形成する工程の一方または双方は、位相シフトマスク若しくはホログラムマスクを用いた露光工程で行うことを要旨とする。それにより、ガラス基板等のように平坦度の低い基板に対しても微細なパターンを形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】駆動力の高い半導体装置を提供する。

【解決手段】半導体基板11の活性領域10に、ゲート絶縁膜13およびゲート電極14が形成されている。ゲート電極14の側面上には、L字状の断面形状を有するサイドウォール16が形成されている。半導体基板11のうちゲート電極14およびサイドウォール16の外側に位置する領域にはソース・ドレイン領域18が形成されている。ゲート電極14の上面上およびサイドウォールの表面上には、応力を有するストレスライナー膜19が形成されている。

(もっと読む)

半導体装置

【課題】 半導体装置の面積を増大させること無く、半導体装置のドレイン電流を向上させることができる半導体装置を提供する。

【解決手段】 半導体基板10と、半導体基板10上に形成され、ゲート絶縁膜16を介して形成されるゲート電極18と、半導体基板10に形成され、ゲート電極18の両側方に位置する領域に形成されるn型のソース/ドレイン拡散層24と、半導体基板10上のゲート電極18両側部に形成され、ゲート電極18のチャネル領域に応力を与えるtensile膜26と、ソース/ドレイン拡散層24上にtensile膜26を貫通して形成される、導電体材料が埋め込まれたコンタクト30を備える。そして、ゲート電極18とソースコンタクト34間距離が、ゲート電極18とドレインコンタクト32間距離よりも広いことを特徴としている。

(もっと読む)

半導体集積回路装置

【課題】 本発明によれば、リーク電流の発生が抑制された半導体集積回路装置及びその製造方法を提供することができる。

【解決手段】 半導体基板上に第1のゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板内に前記第1のゲート電極に対して自己整合的に形成された第1の不純物拡散領域と、前記第1の不純物領域に接続されたコンタクトと、前記半導体基板上に第2のゲート絶縁膜を介して形成された第2のゲート電極と、前記半導体基板内に前記ゲート電極に対して自己整合的に形成された第2の不純物拡散領域と、前記第2のゲート電極と前記第2の不純物拡散領域とに共通に接続されたシェアドコンタクトと、を有する半導体集積回路装置において、前記第2のゲート絶縁膜の誘電率は、前記第1のゲート絶縁膜の誘電率に比べて大きいことを特徴とする半導体集積回路装置。

(もっと読む)

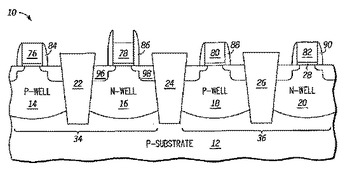

低減されたゲートドーピングを用いる半導体構造体及び同構造体を形成する方法

半導体構造体10は記憶領域34と論理領域36とを有する基板12を含む。第一のp型デバイスは記憶領域34に形成され、第二のp型デバイスは論理領域36に形成される。第一のp型デバイスの半導体ゲートの少なくとも一部は第二のp型デバイスの半導体ゲートの少なくとも一部よりもより低いp型ドーパント濃度を有する。第一及び第二のp型デバイスの半導体ゲートの各々は、ゼロではないp型ドーパント濃度を有する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタの駆動力を調整する。

【解決手段】SRAMアクセス領域SAにおけるN型のMISトランジスタの上に、圧縮応力含有絶縁膜50および引っ張り応力含有絶縁膜51を形成する。一方、SRAMドライブ領域SDにおけるN型のMISトランジスタの上に、引っ張り応力含有絶縁膜51を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ロジック領域におけるトランジスタの上を応力を有する膜で覆って能力を向上させると共に、SRAM領域において、各トランジスタの能力のバランスを保持する。また、リーク電流の発生を抑制する。

【解決手段】本発明の半導体装置では、N型ロジック領域NLにおけるトランジスタが引っ張り応力を有する膜50により覆われ、P型ロジック領域PLにおけるトランジスタが圧縮応力を有する膜55により覆われている。そして、P型SRAM領域PSにおけるトランジスタおよびN型SRAM領域NSにおけるトランジスタは、膜50、55よりも応力の小さい低応力含有絶縁膜60により覆われている。

(もっと読む)

半導体装置及びその製造方法

【課題】 ソフトエラー耐性を向上させることが可能なSRAMセルを備えた半導体装置とその製造方法を提供する。

【解決手段】 半導体基板に形成されたSRAMセルと、前記SRAMセルのn−ウエル2aとp−ウエル2bの境界を分離する第1のディープトレンチ3と、前記SRAMセルを単位ビットセル13毎に分離する第2のディープトレンチ14と、前記第1及び第2のディープトレンチにより分離された領域に、少なくとも1箇所以上の基板電位を取るコンタクト12を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ロジック領域におけるトランジスタの上を応力を有する膜で覆って能力を向上させると共に、SRAM領域において、各トランジスタの能力のバランスを保持し、リーク電流の発生を抑制する事ができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、N型ロジック領域NLにおけるトランジスタが引っ張り応力を有する膜50により覆われ、P型ロジック領域PLにおけるトランジスタが圧縮応力を有する膜55により覆われている。そして、P型SRAM領域PSにおけるトランジスタおよびN型SRAM領域NSにおけるトランジスタは、引っ張り応力を有する膜50aおよび圧縮応力を有する膜55aからなる積層膜により覆われている。

(もっと読む)

半導体装置及びその駆動方法

【課題】SRAMの動作には、書き込みと読み出しがあり、この動作を行っているときにはメモリ全体の一部だけが動作し、他の部分は値を保持しているだけである。この値を保持する期間に消費される電流を低くすることによって、低消費電力化を図った半導体装置を提供することを課題とする。

【解決手段】値を書き込む期間又は読み出す期間と比べて、保持する期間における駆動電圧を低くする半導体装置である。このような半導体装置は、ワード線が接続されたORと、ORに接続されたインバーター回路と、OR及びインバーター回路に接続されたトランジスタと、を有する電源制御回路を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 歩留まりを低下することなく且つ安価に膜厚の異なる金属化合物膜を形成可能な半導体装置の製造方法を提供する。

【解決手段】 複数のストライプ状の素子分離絶縁膜を最上部が基板10の表面より高くなるように基板10に埋め込み素子分離絶縁膜で挟まれた基板10の表面を第1の方向に測って互いに異なる幅を有する第1及び第2の素子領域として定義する工程と、第1の方向に沿って延伸するようにゲート電極151,15xを形成する工程と、第1及び第2の素子領域に第1の方向と直交する方向にゲート電極151,15xを挟んでソース領域131,13x及びドレイン領域141,14xを形成する工程と、第1の方向に平行な面において基板10表面に対して斜め方向から金属膜を堆積する工程と、熱処理により金属化合物膜171,17x,181,18xを形成する工程とを含む。

(もっと読む)

101 - 120 / 149

[ Back to top ]