Fターム[5F083BS17]の内容

半導体メモリ (164,393) | SRAM (3,190) | 駆動トランジスタ (792) | 構造 (444) | ソース/ドレイン構造 (210) | LDD(Lightly Doped Drain) (149)

Fターム[5F083BS17]に分類される特許

41 - 60 / 149

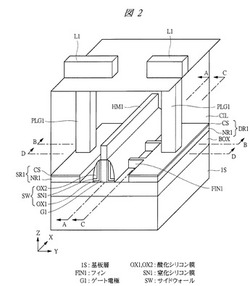

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置およびその製造方法

【課題】製造工程の増加を抑えて、通常のコンタクトとシェアードコンタクトとをそれぞれ良好なコンタクト特性を有するようにする。

【解決手段】半導体装置100は、第1の不純物拡散領域106aに接続するとともに、第1のゲート電極112aとは接続しないように形成された第1のコンタクト124と、第2のゲート電極112bおよび第2の不純物拡散領域106bに共通して接続するように形成された第2のコンタクト126とを含む。第1のコンタクト124および第2のコンタクト126は、それぞれ、層間絶縁膜122の表面から基板101に向かう途中の位置でテーパー角度が小さくなるように変化する形状を有し、第2のコンタクト126においてテーパー角度が変化する位置が、第1のコンタクト124においてテーパー角度が変化する位置よりも基板101に近い。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制できるスタティック・ランダム・アクセス・メモリを得ること。

【解決手段】スタティック・ランダム・アクセス・メモリのメモリセルにおける一対のロードトランジスタは、それぞれ、第1のSiGe膜がシリコン基板のソース領域と第1のシリサイド膜との間に存在し、第2のSiGe膜がシリコン基板のドレイン領域と第2のシリサイド膜との間に存在し、前記第1のSiGe膜ならびに前記第2のSiGe膜は、前記前記ソース領域と前記ドレイン領域の間のチャネル領域のシリコン基板の表面よりも低い位置に存在することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】容易に製造することができ、トランジスタの性能を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2及びゲート電極3が形成されている。半導体基板1の表面の、平面視でゲート電極3を挟む位置に2個の不純物拡散層4が形成されている。2個の不純物拡散層4の表面に、ゲート絶縁膜2と半導体基板1との界面より低くなった掘り込み部6が設けられている。更に、半導体基板1のゲート絶縁膜2下の領域(チャネル)に応力を付加する応力付加膜が、少なくとも掘り込み部6内に位置している。

(もっと読む)

半導体装置およびその製造方法

【課題】しきい値電圧の絶対値が互いに異なる複数のMISトランジスタが用いられる場合において、しきい値電圧の絶対値が大きい方のMISトランジスタの駆動電流の低下を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】第2のnMISトランジスタT2nのしきい値電圧は、第1のnMISトランジスタT1nのしきい値電圧よりも大きく、第2のnMISトランジスタT2nが有する第2のnMIS高誘電率膜H2nにおけるランタン原子濃度およびマグネシウム原子濃度の和は、第1のnMISトランジスタT1nが有する第1のnMIS高誘電率膜H1nにおけるランタン原子濃度およびマグネシウム原子濃度の和よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】MISFETのしきい値のばらつきを抑制する。

【解決手段】半導体基板1に素子分離領域2を形成し、MISFETのしきい値調整用のチャネルドープイオン注入を行なってから、ゲート絶縁膜5a,5bおよびゲート電極GE1,GE2を形成する。それから、イオン注入によりエクステンション領域7a,7bおよびハロー領域8a,8bを形成し、更に炭素(C)、窒素(N)またはフッ素(F)のうちの1種以上をイオン注入することにより拡散防止領域10a,10bを形成する。その後、ゲート電極GE1,GE2の側壁上にサイドウォールSWを形成してから、イオン注入により、ソース・ドレイン用のn+型半導体領域11aおよびp+型半導体領域11bを形成して、nチャネル型MISFETおよびpチャネル型MISFETが形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、しきい値電圧のばらつきが大きいトランジスタのしきい値電圧を調整してしきい値電圧のばらつきを低減することを可能にする。

【解決手段】基板11と絶縁層12とシリコン層13が積層されてなるSOI基板10の該シリコン層13の表面側にトランジスタ20を形成する工程と、SOI基板10上に、トランジスタ20を被覆する第1絶縁膜30と、トランジスタ20に電気的に接続される配線部40とを形成する工程と、配線部40を通じてトランジスタ20のしきい値電圧を測定する工程と、第1絶縁膜30表面に第2絶縁膜を介して支持基板を形成する工程と、SOI基板10の裏面側の基板11と絶縁層12の少なくとも一部を除去する工程と、測定されたしきい値電圧に基づいてトランジスタ20のしきい値電圧を調整する工程を有する。

(もっと読む)

半導体装置

【課題】微細化が進んだ半導体装置の短チャネル効果を防ぎ、特性を向上させることができる半導体装置の提供を課題とする。

【解決手段】単結晶シリコン基板上に形成された酸化膜と、酸化膜上に形成された単結晶シリコン層と、単結晶シリコン層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極を有する半導体装置であって、単結晶シリコン層はチャネル形成領域、ソース領域、ドレイン領域を有し、チャネル形成領域には、ソース領域、ドレイン領域とは逆の導電型の不純物元素が添加され、チャネル形成領域の不純物元素が添加された領域は、上面から見て主軸がソース領域からドレイン領域にかけて伸びるフィッシュボーン形状を有し、フィッシュボーン形状は単結晶シリコン層の表面から底部にかけて形成され、チャネル形成領域の不純物元素が添加された領域は、空乏層を抑止する機能を有することを特徴としている半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】SRAMにおいてNMOS及びPMOSトランジスタのバランスを確保して、PMOSトランジスタの閾値電圧を高くできる半導体装置及びその製造方法を提供する。

【解決手段】メモリ領域において、基板の第1半導体領域(12,13)の第1チャネル形成領域上に第1ゲート絶縁膜(20,21)を介して第1ゲート電極が形成され、第1半導体領域に第1ソースドレイン領域(16,17)が形成されて第1トランジスタが形成され、ロジック領域において、基板の第2半導体領域(14,15)の第2チャネル形成領域上に第2ゲート絶縁膜(22,23)を介して第2ゲート電極が形成され、第2半導体領域に第2ソースドレイン領域(18,19)が形成されて第2トランジスタが形成され、第1ゲート電極の第1ゲート絶縁膜に接する部分が金属(40,41)からなり、第2ゲート電極の第2ゲート絶縁膜に接する部分が半導体(26,27)からなる。

(もっと読む)

半導体装置とその製造方法

【課題】 トランジスタと抵抗等複数種類の半導体素子を簡略化した工程で作成する。

【解決手段】 半導体装置の製造方法は、半導体基板にアスペクト比1以上の素子分離領域を形成し、ゲート絶縁膜を形成し、シリコン層を堆積し、パターニングしてゲート電極と抵抗素子を形成し、ゲート電極の側壁サイドウォールを形成し、第1の活性領域に高濃度の燐を、第2の活性領域及び抵抗素子に高濃度のp型不純物を、イオン注入し、500℃以下の温度でサリサイドブロック層を形成し、サリサイドブロック層を覆うように金属層を堆積し、選択的に金属シリサイド層を形成する。厚いゲート絶縁膜と著しく薄いゲート絶縁膜を形成し、サイドウォール形成前、厚いゲート絶縁膜は貫通しない第1導電型のイオン注入と、厚いゲート絶縁膜も貫通する逆導電型の斜めイオン注入を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造のMONOS型不揮発性メモリセルを有する半導体装置において、信頼度を低減することなく高集積化を実現する。

【解決手段】メモリ用nMISのメモリゲート電極MGの高さを選択用nMISの選択ゲート電極CGの高さよりも20〜100nm高く形成することにより、メモリゲート電極MGの片側面(ソース領域Srm側の側面)に形成されるサイドウォールSW1の幅を、所望するメモリセルMC1のディスターブ特性を得るために必要とする大きさとする。また、周辺用第2nMIS(Q2)のゲート電極G2の高さを選択用nMISの選択ゲート電極CGの高さ以下とすることにより、ゲート電極G2の側面に形成されるサイドウォールSW3の幅を小さくして、シェアードコンタクトホールC2の内部がサイドウォールSW3により埋め込まれるのを防ぐ。

(もっと読む)

半導体装置

【課題】隣接するシェアードコンタクト間の短絡が発生するおそれの少ないSRAMセルを有する半導体装置を提供する。

【解決手段】半導体基板と、半導体基板上に形成された、トランスファトランジスタT、ドライバトランジスタDおよびロードトランジスタLをそれぞれ2つずつ含むSRAMセル10と、SRAMセル10上に形成された層間絶縁膜と、トランスファトランジスタTの第1のゲート電極12a、および,ドライバトランジスタDとロードトランジスタLに共有される第2のゲート電極12bと、第2のゲート電極12bと、ロードトランジスタLのソース・ドレイン領域11eとの両方に接続される、層間絶縁膜中に形成されたシェアードコンタクト14と、を有し、SRAMセル10内において、2つの第2のゲート電極12bがそれらのゲート長方向に重なりをもたないように配置される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜に高誘電率膜を用いたMISトランジスタのトランジスタ特性を向上する。

【解決手段】基板の主面上に形成した酸化シリコン(SiO2)膜上に、ハフニウムおよび酸素を含むベース絶縁膜を形成する。次いで、ベース絶縁膜上に、ベース絶縁膜より薄く、かつ、金属元素のみからなる金属薄膜を形成し、その金属薄膜上に、耐湿性および耐酸化性を有する保護膜を形成する。その後、保護膜を有する状態で、ベース絶縁膜に金属薄膜の金属元素をすべて拡散することによって、酸化シリコン膜上に、酸化シリコン膜より厚く、かつ、酸化シリコンより誘電率が高く、ベース絶縁膜のハフニウムおよび酸素と、金属薄膜の金属元素とを含む混合膜(高誘電率膜)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 所望のVthが異なる複数種類のMOSFETに対してVthを選択的に制御することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板40上の複数種類のMOSFET(Tr1−Trn)を形成する領域に、二酸化シリコンを含む第1ゲート絶縁膜45と、金属酸化物を含む第2ゲート絶縁膜46を形成する工程と、第1ゲート絶縁膜45及び第2ゲート絶縁膜46上にポリシリコンを含むゲート電極47を形成する工程とを有する。この方法は更に、ゲート電極47の形成後、複数種類のMOSFET(Tr1−Trn)のうち、1種類以上のMOSFET(Trn)の温度を、他の種類のMOSFET(Tr1−Tr3)の温度と異ならせるように熱処理する工程を有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】シェアードコンタクトを備えるフルCMOS型のSRAMメモリセルにおいて、安定した低電圧動作を得る。

【解決手段】半導体記憶装置は、第1の配線が、第3のドレイン活性領域と第2のゲート電極用配線を開口するように配置された一つの第1のコンタクトを介して、第3のドレイン活性領域と第2のゲート電極用配線に電気的に接続されるとともに、第2の配線が、第4のドレイン活性領域と第1のゲート電極用配線を開口するように配置された一つの第2のコンタクトを介して、第4のドレイン活性領域と第1のゲート電極用配線に電気的に接続されており、第1から第4のいずれかのドレイン活性領域と離れた部分もしくは連続した部分に活性領域を備え、活性領域と前記第1ゲート若しくは前記第2ゲート電極用配線が重なる。

(もっと読む)

半導体装置及びその製造方法

【課題】STIの圧縮応力を減少し、チャネル方向とチャネル幅方向の応力を印加することにより、駆動能力を増大したCMOS半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、NMOSFET用活性領域AR1、PMOSFET用活性領域AR2を画定する素子分離溝STと、素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜OXと、NMOSFET領域AR1に形成されたNMOSFETと、PMOSFET領域AR2に形成されたPMOSFETと、NMOSFET構造を覆い、NMOSFET用活性領域AR1の周囲における凹部上及びPMOSFET用活性領域AR2のゲート幅方向外側における凹部上に延在して形成された引張応力膜TSFと、PMOSFET構造を覆い、PMOSFET用活性領域AR2のチャネル長方向外側における凹部上に延在して形成された圧縮応力膜CSFとを有する。

(もっと読む)

半導体装置およびその製造方法、ならびにその半導体装置を用いた集積半導体装置および不揮発性半導体記憶装置

【課題】絶縁ゲート型電界効果トランジスタにおいて低電圧下で急峻なスイッチング特性を有する半導体素子を提供する。

【解決手段】大規模集積回路に用いられているプレーナ型のロジック回路用MOSFETにおいて、ドレイン拡散層電極のなかに、ダイオード素子と抵抗素子が並列配置されるように形成することで、低電圧であってもゲート電圧変化に対してドレイン電流が急峻な変化を示す高性能トランジスタが実現できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板を不必要に露出させることなく、半導体装置の信頼性を向上できる技術を提供する。

【解決手段】半導体基板1S上にゲート電極G1とゲート電極G2を形成した後、nチャネル型MISFET形成領域を酸化シリコン膜で覆う一方、pチャネル型MISFET形成領域を露出する。続いて、半導体基板1Sの全面に例えば酸化アルミニウム膜よりなる元素供給膜7を形成した後、熱処理を実施する。これにより、ゲート電極G2直下の第1絶縁膜にアルミニウムを拡散させて高濃度HfAlO膜8aと低濃度HfAlO膜8bを形成する。その後、元素供給膜として例えば酸化マグネシウム膜を使用してゲート電極G1直下の第1絶縁膜にマグネシウムを拡散させて高濃度HfMgO膜と低濃度HfMgO膜を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】リーク電流を低減することのできる、スタティック型のメモリセルを含む半導体記憶装置およびその製造方法を提供する。

【解決手段】半導体記憶装置は、複数のメモリセルと、複数のビット線と、複数のワード線と、制御用n型トランジスタTr1とを備えている。制御用n型トランジスタTr1は、複数のワード線または複数のビット線の各々の電位を制御するためのものである。複数のメモリセルの各々は、データを保持するためのメモリセル用n型トランジスタTr2を有している。メモリセル用n型トランジスタTr2のゲート電極GE2におけるn型不純物の濃度は、制御用n型トランジスタTr1のゲート電極GE1におけるn型不純物の濃度よりも低い。この結果、メモリセル用n型トランジスタ(トランジスタTr2)の閾値電圧Vthを高くすることができるので、半導体記憶装置のリーク電流を低減することができる。

(もっと読む)

2方向ハロ注入

【課題】傾斜付きイオン注入に起因するシャドーイング効果を緩和する。

【解決手段】半導体装置は、シリコン層と、シリコン層上に設けられたトランジスタ・ゲートと、1対のソース/ドレイン領域と、シリコン層内のチャネル領域と、を含む第1電界効果型トランジスタと、を具備する。シリコン層は、シリコン層のチャネル領域に隣接する部分と同じゼロでない濃度の特定のタイプのイオンがチャネル領域の一部に注入されるように、第1電界効果型トランジスタに隣接する第2電界効果型トランジスタの高さに基づいた角度でイオンをドープされている。

(もっと読む)

41 - 60 / 149

[ Back to top ]