Fターム[5F083EP17]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | トラップ蓄積型 (2,146)

Fターム[5F083EP17]の下位に属するFターム

MNOS型(MONOS型を含む) (1,550)

Fターム[5F083EP17]に分類される特許

41 - 60 / 596

不揮発性メモリー装置の製造方法

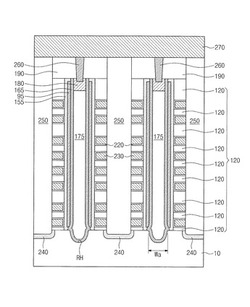

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

半導体不揮発性メモリ

【課題】 本発明は、不揮発性メモリ・セルにおける電荷貯蔵層を論理工程において形成する方法を提供する。

【解決手段】 論理工程において不揮発性メモリ・セルにおける電荷貯蔵層を形成する方法は、基板のアクティブ領域の上にセレクト・ゲートを形成するステップ、その基板のアクティブ領域に部分的に重なる長いポリシリコン・ゲートを形成するステップ、及びその長いポリシリコン・ゲートの間に電荷貯蔵層を充填するステップを含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】不揮発性半導体記憶装置の高集積化と高歩留りを実現する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、複数のメモリストリングを有する第1乃至第4のフィン型積層構造9−1,9−2,9−3,9−4と、第1及び第2のフィン型積層構造9−1,9−2の第2の方向の一端を互いに接続する第1の部分P1と、第3及び第4のフィン型積層構造9−3,9−4の第2の方向の一端を互いに接続する第2の部分P2と、第1及び第3のフィン型積層構造9−1,9−3の第2の方向の他端を互いに接続する第3の部分P3と、第2及び第4のフィン型積層構造9−2,9−4の第2の方向の他端を互いに接続する第4の部分P4とを備える。第1及び第2の部分P1,P2は、ソース領域であり、第3及び第4の部分P3,P4は、ドレイン領域である。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 ダイオードとトランジスタとを直列接続した半導体メモリにおいて、ダイオードからトランジスタにキャリアが入ることで、トランジスタの特性が劣化する課題がある。

【解決手段】 半導体記憶装置において、ダイオード(PD)中のキャリアを生成するダイオード半導体層(40p)と、トランジスタのチャネル層(8p)との間に、当該キャリアを対消滅させる構造(61pと62p等)を有する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置を構成する回路を高集積度化する。

【解決手段】一つの実施形態によれば、半導体記憶装置は、半導体基板と複数のメモリセルトランジスタを有する。前記複数のメモリセルトランジスタは、前記半導体基板に設けられた深溝にトレンチゲートが埋設され、直列接続される。メモリセルの書き込み動作及び読み出し動作のとき、トレンチゲートの周囲及び間の前記半導体基板の領域に、前記半導体基板とは逆導電型の反転層が形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】書き込みを高速化した不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置110は、ベース半導体層10aと、電極70aと、チャネル半導体層30aと、ベーストンネル絶縁膜20aと、チャネルトンネル絶縁膜40aと、電荷保持層50aと、ブロック絶縁膜60aと、を有するメモリ部MC1を備える。チャネル半導体層30aは、ベース半導体層10aと電極70aとの間に設けられ、電極70aに対向するチャネル部31aを含む。ベーストンネル絶縁膜20aは、ベース半導体層10aとチャネル半導体層30aとの間に設けられる。チャネルトンネル絶縁膜40aは、電極70aとチャネル部31aとの間に設けられる。電荷保持層50aは、電極70aとチャネルトンネル絶縁膜40aとの間に設けられ、電荷を保持する。ブロック絶縁膜60aは、電極70aと電荷保持層50aとの間に設けられる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板の結晶性の悪化を招くことなく、素子分離トレンチの幅を小さくできる半導体装置の製造方法を提供する。

【解決手段】マスク用窒化膜51およびパッド酸化膜52からなるハードマスクを用いて、シリコン基板2がエッチングされることにより、素子分離トレンチ21が形成される。素子分離トレンチ21の内面に熱酸化法によりライナー酸化膜22が形成される。続いて、半導体基板2を窒素雰囲気中に配置して、半導体基板2が熱処理される。熱処理後に、エッチングにより、ライナー酸化膜22が薄膜化される。そして、HDP−CVD法により、絶縁物23が素子分離トレンチ21内に埋め込まれる。

(もっと読む)

半導体集積回路

【課題】 不揮発記憶保持用途の電界効果トランジスタと、論理演算用途の電界効果トランジスタの製造工程を別々に設けることなく前記2用途の電界効果トランジスタを同一半導体基板上に同一構造に作製できるようにする。

【解決手段】 ゲート絶縁構造体12に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタで半導体集積回路のメモリ回路とロジック回路の両方を構成し、ゲート絶縁構造体に記憶保持材料を含むnおよびpチャネル型電界効果トランジスタのゲート-基板領域間に印加する電圧の大きさと印加タイミングを制御することによって、論理演算状態と記憶書込み状態と不揮発記憶保持状態を電気的に切り替える。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

垂直的に集積された不揮発性記憶セルサブストリングを含む不揮発性記憶装置の形成方法、及び形成された不揮発性記憶装置

【課題】 セルの電気的特性の均一性を向上させ得る3次元不揮発性記憶装置及びその形成方法を提供する。

【解決手段】 本発明の不揮発性記憶装置の形成方法は不揮発性記憶セルが高集積化された垂直的積層を形成するための段階を含む。不揮発性記憶セルでは、直列に電気的に連結される複数の垂直サブストリングを使用して記憶セルが半導体基板上に垂直に積層される。このとき、記憶セルの垂直方向の積層は劣等に作用するメモリセルストリングが発生しないように、製造工程において補正するためにダミー記憶セルを利用する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】消去動作特性を向上した一括加工型3次元積層メモリ構成の不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、積層構造体MLと、導電芯ピラーPBG、芯絶縁膜49、半導体パイプピラーSP、内側絶縁膜42、記憶層48、外側絶縁膜43、を備えた不揮発性半導体記憶装置が提供される。積層構造体は、第1方向に積層された複数の電極膜61と、複数の電極膜どうしの間に設けられた電極間絶縁膜62と、を有する。導電芯ピラーは積層構造体を第1方向に貫通する。芯絶縁膜は導電芯ピラーと電極膜との間に設けられる。半導体パイプピラーは芯絶縁膜と電極膜との間に設けられ、積層構造体を第1方向に貫通する。内側絶縁膜は半導体パイプピラーと電極膜との間に設けられる。記憶層は内側絶縁膜と電極膜との間に設けられる。外側絶縁膜は記憶層と電極膜との間に設けられる。

(もっと読む)

不揮発性半導体記憶装置

【課題】より安定した動作を実現する一括加工型3次元積層型の不揮発性半導体記憶装置を提供する。

【解決手段】実施形態によれば、メモリ部MUと、メモリ部に併設された非メモリ部PUと、を備えた不揮発性半導体記憶装置が提供される。メモリ部は、積層された複数の電極膜61と、複数の電極膜どうしの間に設けられた電極間絶縁膜62と、を含む積層構造体MLと、積層構造体と積層された選択ゲート電極SGと、積層構造体及び選択ゲート電極を貫通する半導体ピラーSPと、電極膜と半導体ピラーとの間に設けられた記憶層48と、を含む。非メモリ部は、複数の電極膜の少なくとも1つと同層の部分を含むダミー導電膜65と、選択ゲート電極と同層のダミー選択ゲート電極SGdと、ダミー導電膜に接続されたコンタクト電極と、ダミー選択ゲート電極に接続されたコンタクト電極と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】オフ電流を低減し、特性ばらつきが抑制された多結晶半導体層をチャネル領域とする半導体装置の製造方法を提供する。

【解決手段】半導体基板の上に絶縁体層を形成する工程と、絶縁体層上に狭窄部を有する非晶質または多結晶質の半導体層を形成する工程と、半導体層上に半導体層よりも熱膨張係数の大きい絶縁体層を形成する工程と、熱処理を行う工程と、絶縁体層を除去する工程と、狭窄部の側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体層中にソース・ドレイン領域を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁膜、半導体層、及びトンネル絶縁膜のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、動作安定性の向上した不揮発性記憶素子を提供する。

【解決手段】不揮発性記憶素子10は、基板30上と、ソース電極34S及びドレイン電極34Dと、半導体層36と、トンネル絶縁膜38と、電荷蓄積層40と、中間絶縁膜42と、ゲート電極44Gと、を備えており、半導体層36、トンネル絶縁膜38、及び中間絶縁膜42が、酸化ガリウムを含んでいる。

(もっと読む)

不揮発性記憶素子

【課題】本発明は、中間絶縁層、電荷蓄積層、及びトンネル絶縁層のうちの少なくとも1つが酸化ガリウムを含まない場合に比べて、情報の書込みと消去を繰り返しても閾値電圧の変動が抑制された不揮発性記憶素子を提供する。

【解決手段】基板と、ソース電極と、ドレイン電極と、チャネル層と、電荷蓄積層と、ゲート電極と、前記チャネル層及び前記電荷蓄積層の間に設けられたトンネル絶縁層と、前記電荷蓄積層及び前記ゲート電極の間に設けられた、中間絶縁層と、を備え、前記中間絶縁層、前記電荷蓄積層、及び前記トンネル絶縁層が酸化ガリウムを含み、前記チャネル層が有機半導体層である不揮発性記憶素子である。

(もっと読む)

酸化チタン粒子、その製造方法、磁気メモリ、光情報記録媒体及び電荷蓄積型メモリ

【課題】従来にない新規な物性を発現し得る酸化チタン粒子及びその製造方法と、それを用いた磁気メモリ、光情報記録媒体及び電荷蓄積型メモリを提供する。

【解決手段】逆ミセル法を利用せずに、ゾル−ゲル法によってシリカ被覆水酸化チタン化合物粒子を直接製造し、当該シリカ被覆水酸化チタン化合物粒子を焼成処理する。これにより、温度が約460K付近において非磁性半導体と常磁性金属とに相転移する従来におけるバルク体とは異なり、室温で相転移せずに、全ての温度領域において、Ti3O5粒子本体が常磁性金属の特性を常に維持することができるという従来にない新規な物性を発現し得る酸化チタン粒子1を提供できる。

(もっと読む)

半導体装置およびその製造方法

【課題】高耐圧MISFETを含む半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】高耐圧MISFETQ4のゲート絶縁膜GOX4を、酸化シリコン膜と窒化シリコン膜という異なる種類の膜から形成する。具体的に、高耐圧MISFETQ4では、ゲート絶縁膜GOX4を、酸化シリコン膜PREOX1と、この酸化シリコン膜PREOX1上に形成された酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から形成している。

(もっと読む)

酸化チタン粒子、その製造方法、磁気メモリ、光情報記録媒体及び電荷蓄積型メモリ

【課題】従来にない新規な物性を発現し得る酸化チタン粒子、光情報記録媒体及びその製造方法と、それを用いた磁気メモリ及び電荷蓄積型メモリを提供する。

【解決手段】Ti3O5粒子本体2を形成した際に、Ti3O5粒子本体2の表面を覆っていたシリカガラスが除去された形状を有し、また、温度が約460K付近において非磁性半導体と常磁性金属とに相転移する従来におけるバルク体とは異なり、室温で相転移せずに、全ての温度領域において、Ti3O5粒子本体が常磁性金属の特性を常に維持することができるという従来にない新規な物性を発現し得る酸化チタン粒子1を提供できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

41 - 60 / 596

[ Back to top ]