Fターム[5F083EP17]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | トラップ蓄積型 (2,146)

Fターム[5F083EP17]の下位に属するFターム

MNOS型(MONOS型を含む) (1,550)

Fターム[5F083EP17]に分類される特許

61 - 80 / 596

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

連続する電荷蓄積誘電体スタックを有する不揮発性メモリアレイ

【課題】連続する電荷蓄積誘電体スタックを有する不揮発性メモリアレイを提供する。

【解決手段】不揮発性メモリセルアレイの集積回路は、基板を覆う誘電体スタック層と、該誘電体スタック層下の該基板内のイオン注入領域とを有する。該誘電体スタック層は、ワード線とビット線とを介してアクセスされ不揮発性データを記憶する該誘電体スタック層の複数の箇所を含む平坦な領域に亘って連続している。

(もっと読む)

半導体装置およびその製造方法

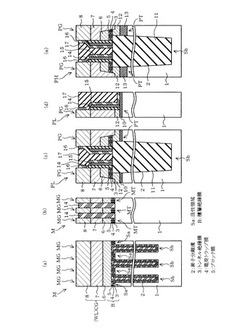

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、製造歩留まりを向上できる技術を提供する。

【解決手段】給電領域に位置するCGシャント部の選択ゲート電極CGの半導体基板1の主面からの第2高さd2が、メモリセル形成領域の選択ゲート電極CGの半導体基板1の主面からの第1高さd1よりも低くなるように、CGシャント部の選択ゲート電極CGを形成する。

(もっと読む)

半導体記憶素子、及び半導体記憶装置

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶素子、及び半導体記憶装置を提供する

【解決手段】 半導体層19と、半導体層19上に設けられたトンネル絶縁膜18と、トンネル絶縁膜18上に設けられ、膜厚が0.9nm以上2.8nm以下であり、立方晶ハフニア粒子17を含む電荷蓄積膜16と、電荷蓄積膜16上に設けられたブロック絶縁膜15と、ブロック絶縁膜15上に設けられた制御電極13とを備えることを特徴とする半導体記憶素子。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】不揮発性メモリのメモリセルは、p型ウエルPWの上部に絶縁膜3を介して形成された制御ゲート電極CGと、p型ウエルPWの上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGとp型ウエルPWとの間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されかつ内部に電荷蓄積部を有する絶縁膜5とを有している。メモリゲート電極MGは、ノンドープのシリコン膜6aと不純物を導入したシリコン膜6bとの積層膜により形成されている。シリコン膜6bの不純物濃度を高くすることでメモリゲート電極MGの抵抗を低くして不揮発性メモリの動作速度を向上させ、シリコン膜6aの不純物濃度を低くすることで、不揮発性メモリのデータ保持特性を向上させることができる。

(もっと読む)

3次元半導体装置

【課題】3次元的に配列される導電パターンの厚さを増加しその抵抗を減少できる3次元半導体装置を提供する。

【解決手段】この装置は基板上に順に積層された水平構造体と、水平構造体を垂直に横切る垂直構造体とを具備する。水平構造体の各々は基板に平行な導電ライン及び垂直構造体に隣接した導電ラインの一側壁を覆う第2パターンを含む。また垂直構造体の各々は半導体柱及び水平構造体に隣接した半導体柱の少なくとも一側壁を覆う第1パターンを含む。

基板上に順に積層された電極を含む電極構造体と、電極構造体を垂直に貫通する半導体パターンと、第1パターン及び第2パターンを具備して半導体パターンと電極構造体との間に介在するメモリー要素と、を含み、第1パターンは垂直に延長されて複数の電極を横切り、第2パターンは水平に延長されて複数の半導体パターンを横切る。

(もっと読む)

半導体記憶装置、及びその製造方法

【課題】 高効率に電荷を蓄積及び消去することができ、かつ蓄積した電荷を長時間保持することができる半導体記憶装置、及びその製造方法を提供する。

【解決手段】 半導体記憶装置10は、半導体基板11と、半導体基板11内に離間して設けられたソース領域3及びドレイン領域2と、ソース領域3とドレイン領域2との間であって半導体基板11上に設けられたトンネル絶縁膜12と、トンネル絶縁膜12上に設けられ、酸化物クラスターを含む電荷蓄積膜13と、電荷蓄積膜13上に設けられたブロック絶縁膜14と、ブロック絶縁膜14上に設けられたゲート電極15とを備える。

(もっと読む)

金属窒化膜、該金属窒化膜を用いた半導体装置、および半導体装置の製造方法

【課題】所望の実効仕事関数(例えば、高い実効仕事関数)を実現し、かつ、EOTが変化しない、またはEOTの変化を低減した金属窒化膜、金属窒化膜を用いた半導体装置、および半導体装置の製造方法を提供すること。

【解決手段】本発明の一実施形態に係る金属窒化膜は、TiとAlとNを含有し、該金属窒化膜のTiとAlとNのモル比率(N/(Ti+Al+N))が0.53以上であり、かつ、上記金属窒化物層のTiとAlとNのモル比率(Ti/(Ti+Al+N))が0.32以下であり、かつ上記金属窒化物層のTiとAlとNのモル比率(Al/(Ti+Al+N))が0.15以下である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】寄生容量を抑制した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】第1方向に沿って交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体MLを第1方向に貫通する半導体ピラーSPと、複数の電極膜WLのそれぞれと半導体ピラーSPとの間に設けられた電荷蓄積膜48と、電荷蓄積膜48と半導体ピラーSPとの間に設けられた内側絶縁膜42と、電極膜WLのそれぞれと電荷蓄積膜48との間に設けられた外側絶縁膜43と、を有するメモリ部MUと、メモリ部MUと、第1方向に対して直交する第2方向に沿って併設され、積層構造体MLの第1方向に沿った少なくとも一つの電極膜WLの位置と同じ位置に絶縁部50と、を有する非メモリ部PR10とを備えている。

(もっと読む)

選択的/差動閾値電圧機能を含む不揮発性メモリ検知システム及び方法

不揮発性メモリ装置とその消去方法、及びそれを含むメモリシステム

【課題】向上された信頼性を有する不揮発性メモリ装置及びその消去方法、そしてそれを含むメモリシステムが提供される。

【解決手段】不揮発性メモリ装置の消去方法が提供される。消去方法はメモリセルに各々連結された複数のワードラインにワードライン消去電圧を印加する段階と、接地選択トランジスタに連結された接地選択ラインに特定電圧を印加する段階と、接地選択ラインに特定電圧を印加する段階の間にメモリストリングが形成される基板に消去電圧を印加する段階と、基板の電圧変化に応答して接地選択ラインをフローティングする段階とに構成される。

(もっと読む)

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法

電気的浸透性ソース層を含む半導体デバイス及びこれの製造方法に対する様々な実施例が与えられる。一実施例では、半導体デバイスは、ゲート層、誘電体層、メモリ層、ソース層、半導体チャネル層、及びドレイン層を含む。ソース層は電気的浸透性及びパーフォレーションを有する。半導体チャネル層はソース層及びメモリ層と接触する。ソース層及び半導体チャネル層は、ゲート電圧チューナブル電荷注入バリアを形成する。  (もっと読む)

(もっと読む)

半導体メモリ

【課題】Al-rich Al2O3の電荷蓄積層において、Alの組成の関数として電荷蓄積密度を解析し、電荷蓄積密度が最大となるような半導体メモリを提供する。

【解決手段】半導体基板の上面に順次、トンネル障壁層、電荷蓄積層、ブロック障壁層、ゲート電極を積層し、電荷蓄積層の局在準位に電子を蓄積することによりトランジスタのしきい値電圧を変化させる半導体メモリにおいて、電荷蓄積層をアルミニウム過剰の酸化アルミニウム(Al-rich Al2O3)とし、そのアルミニウムの組成を所定の範囲に設定し、電荷蓄積層の電荷蓄積密度が最大値(極大値)を含む所定値以上になる構成とした。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極の不純物分布のバラツキを抑え、STIエッジ部分への電界集中をより効果的に制御でき、実効チャネル幅が狭くなることを抑制できる半導体装置およびその製造方法を提供する。

【解決手段】P型のシリコン基板10の一主面11に、トレンチ22と絶縁物24とを有する素子分離領域25と、素子分離領域25に囲まれた素子領域12であって、シリコン基板10の側面上部17が、トレンチ25に露出した素子領域12を形成し、ゲート絶縁膜40をシリコン基板10の上面14から側面上部17に延在して形成し、N+型ポリシリコン32とN+型ポリシリコン32の両側のP+型ポリシリコン34と、P+型ポリシリコン34の下側の側面上部17に沿って設けられたN+型ポリシリコン36とを有するゲート電極30を形成する。

(もっと読む)

不揮発性半導体メモリ

【課題】 従来のMONOSは、SiNに電荷を蓄積する構成であるが、電荷蓄積量が不十分であり閾値電圧変化幅を大きく取れず、またHfO2,ZrO2,TiO2中へLa系元素を導入した技術ではドーパント導入による電荷の高密度化は実現が困難である。

【解決手段】 窒化シリコン膜よりも十分に誘電率の高いZr酸化物、Hf酸化物等の窒化シリコンよりも十分に高い誘電率を有する金属酸化物を母体材料として、その中に電子の出し入れが可能なトラップレベルを発生させるために、価数が2つ上(VI価)以上の高価数物質を適量添加する構成の電荷蓄積層を有する不揮発性半導体メモリである。

(もっと読む)

不揮発性メモリ装置およびそのプログラム方法と、それを含むメモリシステム

【課題】信頼性が改善される不揮発性メモリ装置のプログラム方法を提供する。

【解決手段】不揮発性メモリ装置は基板及び基板と交互する方向に積層された複数のメモリセルを含む。不揮発性メモリ装置のプログラム方法は選択された少なくとも1つのビットラインに第1正電圧を印加する段階、非選択された少なくとも1つのビットラインに第2正電圧を印加する段階、選択されたストリング選択ラインに第3正電圧を印加する段階、非選択されたストリング選択ラインに第4正電圧を印加する段階、そしてワードライン等にプログラム動作電圧を印加する段階を含む。

(もっと読む)

3次元半導体装置の配線構造体

【課題】集積度及び信頼性を共に向上させた3次元半導体装置を提供する。

【解決手段】3次元半導体装置の配線構造が提供される。3次元半導体装置は3次元基板上に2次元的に配列された積層構造体、第1配線を含み、積層構造体の上部に配置される第1配線層及び第2配線を含み、第1配線層の上部に配置される第2配線層を含み、積層構造体各々は順次に積層された複数の下部ワードラインを含む下部構造体及び順次に積層された複数の上部ワードラインを含み、下部構造体の上部に配置される上部構造体を含み、第1配線各々は下部ワードラインの内の何れか1つに連結し、第2配線各々は上部ワードラインの内の何れか1つに連結する。

(もっと読む)

不揮発性半導体記憶装置

【課題】集積度が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、それぞれ複数の絶縁膜及び電極膜14が交互に積層された積層体と、この積層体内に埋設され、絶縁膜及び電極膜14の積層方向に延びるシリコンピラー31と、電極膜14とシリコンピラー31との間に設けられた電荷蓄積層26と、を設ける。そして、電極膜14を、それぞれが電荷蓄積層26を挟んでシリコンピラー31に対向する複数の制御ゲート電極CGa及びCGbに分割する。

(もっと読む)

半導体記憶装置

【課題】スプリットゲート型のMONOSメモリセルを有する半導体記憶装置において、SSI方式による書込み時のディスターブ耐性を向上させる。また、非選択メモリセルのディスターブ耐性が向上することにより、メモリモジュールの面積を低減させる。

【解決手段】メモリゲート電極12の側面において、電荷蓄積膜9と絶縁膜11との間に絶縁膜10を形成し、メモリゲート電極12側面の絶縁膜10および11の合計の厚さを、メモリゲート電極12下部の絶縁膜11の厚さよりも厚く形成する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】電荷保持特性の良好な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体層SMLと、半導体層に対向して設けられた第1絶縁層I1と、半導体層と第1絶縁層との間に設けられた第2絶縁層I2と、第1絶縁層と第2絶縁層との間に設けられた機能層I3と、第1絶縁層の半導体層とは反対の側に設けられ、互いに離間した第1ゲート電極G1及び第2ゲート電極G2と、を備えた不揮発性半導体記憶装置が提供される。機能層のうちの第1ゲート電極に対向する第1領域R1、及び、機能層のうちの第2ゲート電極に対向する第2領域R2の電荷蓄積能は、機能層のうちの第1領域と第2領域との間の第3領域R3とは異なる。

(もっと読む)

61 - 80 / 596

[ Back to top ]