Fターム[5F083EP17]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | トラップ蓄積型 (2,146)

Fターム[5F083EP17]の下位に属するFターム

MNOS型(MONOS型を含む) (1,550)

Fターム[5F083EP17]に分類される特許

101 - 120 / 596

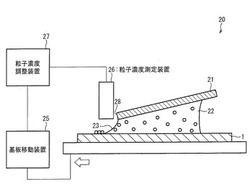

半導体記憶素子の製造方法

【課題】金属ナノ結晶からなる離散的フローティングゲートを、移流集積法により形成する半導体記憶素子の製造方法を提供する。

【解決手段】製造方法は、シリコン基板1と、シリコン基板1上に形成されたトンネル絶縁膜に対向するように配置された第2の基板21との間に、金属ナノ粒子が分散された粒子分散液22を充填する充填工程と、トンネル絶縁膜の表面に沿った方向に、第2の基板21をシリコン基板1に対して相対的に移動させることにより、トンネル絶縁膜の表面における第2の基板21から露出した領域に形成される粒子分散液22のメニスカス領域23において、粒子分散液22の溶媒を蒸発させることにより、トンネル絶縁膜上に金属ナノ粒子を離散的に配置する。

(もっと読む)

不揮発性半導体記憶装置

【課題】貫通ホールの径の変動に起因した電界の変動を補償し、良好な動作特性を有する不揮発性半導体記憶装置を提供する。

【解決手段】第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体を第1方向に貫通する半導体ピラーSPと、電極膜のそれぞれと半導体ピラーとの間に設けられた記憶層48と、記憶層と半導体ピラーとの間に設けられた内側絶縁膜42と、電極膜のそれぞれと記憶層との間に設けられた外側絶縁膜43と、を備える。第1方向に対して垂直な第2方向における外側絶縁膜の外径が大きい領域では、外径が小さい領域よりも、第2方向における外側絶縁膜の厚さが厚い。

(もっと読む)

メモリ半導体装置、その製造方法、及び動作方法

【課題】メモリ半導体装置、その製造方法及び動作方法を提供する。

【解決手段】メモリ半導体装置は、基板の上部面に垂直長軸を有し、2次元的に配列される複数の半導体パターン、及び複数の半導体パターンを横切る長軸を有しながら、複数の半導体パターン間で3次元的に配列される複数のワードラインを包含できる。

(もっと読む)

半導体メモリー装置のチャンネルをプリチャージする方法

【課題】プログラムディスターバンスが効果的に遮断されて高いデータ信頼性を有する3次元半導体メモリー装置のチャンネルをプリチャージする方法を提供する。

【解決手段】本発明による半導体メモリー装置のプログラム方法は、複数のビットラインの中でプログラムビットラインに連結される少なくとも1つのインヒビットストリングのチャンネルと、インヒビットビットラインに連結されるインヒビットストリングの中で少なくとも何れか1つのチャンネルとを共通ソースラインに供給されるプリチャージ電圧に充電する段階と、ワードライン電圧を複数のセルストリングに供給してプリチャージされたチャンネルをブースティングさせる段階と、を有する。

(もっと読む)

3次元メモリー装置、及びそのプログラム方法

【課題】集積度の増加と共にプログラムディスターバンス問題を効果的に減らすことができる3次元メモリー装置、及びそのプログラム方法が提供される。

【解決手段】本発明の3次元メモリー装置は、複数のワードライン平面が積層されたメモリーセルアレイ、選択されたワードライン平面に具備された少なくとも2以上のページのメモリーセルを同時にプログラムする書込み読出し回路、そして前記書込み読出し回路のプログラム動作を制御する制御回路を含むことができる。

(もっと読む)

ナノ構造ベースNANDフラッシュセルおよびその周辺回路の形成方法

ナノ構造に基づく電荷蓄積領域は、不揮発性メモリ装置に備えられており、選択ゲートおよび周辺回路の製造と一体に製造される。1つ以上のナノ構造コーティングは、メモリアレイ領域および周辺回路領域の基板に塗布される。選択ゲートや周辺トランジスタについての目標領域などの基板の不要な領域から、ナノ構造コーティングを除去するための様々な工程が、行われる。一例では、基盤のアクティブ領域にナノ構造を選択的に形成するために、自己組織化に基づく工程を用いて、1つ以上のナノ構造コーティングが形成される。自己組織化によって、ナノ構造コーティングのパターニングやエッチングを行うことなく、互いに電気的に分離されているナノ構造の個別のライン群を形成することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において、シリコン窒化膜の含有水素量を低減してメモリ動作の長期信頼性が確保された製造方法を提供する。

【解決手段】半導体装置の製造方法は、表面にシリコン窒化膜103が形成されたシリコン基板101aを収容した処理室内の圧力を大気圧よりも低くした状態で処理室内に酸素含有ガスと水素含有ガスとを供給して、シリコン窒化膜103の一部を酸化する工程と、シリコン窒化膜103の酸化した部分104を除去する工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】チャネル界面付近の浅いエネルギー準位に捕獲された電荷を予め除去し、データ保持特性の良好な不揮発性半導体記憶装置を提供する。

【解決手段】メモリ部MUと、制御部CTUと、を備える不揮発性半導体記憶装置において、メモリ部は、第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体MLを第1方向に貫通する半導体ピラーSPと、電極膜WLと半導体ピラーSPとの間に設けられた、内側絶縁膜42、記憶層及び外側絶縁膜と、半導体ピラーSPの一端と電気的に接続された配線と、を有す。制御部CTUは、消去動作の際に、配線を第1電位に設定しつつ、電極膜WLを第1電位よりも低い第2電位に設定する第1動作の後に、配線を第3電位に設定しつつ、電極膜WLを第3電位よりも高い第4電位に設定する第2動作を実施する。

(もっと読む)

半導体集積回路装置

【課題】不揮発性メモリにおいて、データの書き換え回数増加時における動作信頼性を向上できる技術を提供する。

【解決手段】基板1上に、ボトム酸化膜7Aと電荷蓄積層8Aとトップ酸化膜9Aからなる積層絶縁膜を介して、ゲート電極9Aが形成され、ボトム酸化膜7Aの膜厚はトップ酸化膜9Aの膜厚よりも厚く形成されている。このように構成されているメモリセルにおいて、書き込みおよび消去となる電荷蓄積層8Aへの電荷のやり取りは、ゲート電極10Aと電荷蓄積層8Aとの間で行う。

(もっと読む)

ナノ線メモリ

【課題】単純な構造のナノ点を有するメモリを利用してマルチレベルを保存することができるメモリ素子を提供する。

【解決手段】ソース210及びソース210と対応するドレイン220と、ソース210とドレイン220との間を連結するように形成されているナノチャンネル230とを含み、ナノチャンネル230は、ソース210及びドレイン220の電圧によってソース210とドレイン220との間を電気的に連結するナノ線と、ナノ線上に吸着されて形成され、電荷を補集する複数のポテンシャルを有するナノ点とを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

不揮発性半導体記憶装置とその駆動方法および電子機器

【課題】周辺回路の増大を極力抑えつつ、データディスターブを改善する不揮発性半導体記憶装置を提供する。

【解決手段】第1ボディ領域100上に不純物拡散層104,124を、第1不純物拡散層104上に第2ボディ領域106を形成する。第1不純物拡散層104はメモリトランジスタMTのドレイン領域と選択トランジスタSTのソース領域、第1不純物拡散層124は選択トランジスタSTのドレイン領域をなす。第2ボディ領域106と第1不純物拡散層104に跨るように第2ボディ領域106上にメモリトランジスタMTのゲート部G_MTをMONOS構造で形成する。第1不純物拡散層104、第1ボディ領域100、第1不純物拡散層124に跨るように選択トランジスタSTのゲート部G_STをMOS型構造で形成する。両トランジスタMT,STは、バックゲートとなるボディ領域が電気的に分離される。

(もっと読む)

不揮発性記憶装置の記憶維持

【課題】NAND型の不揮発性記憶装置において、障壁高さが低い絶縁体や誘電率の高い絶縁体や電荷をトラップする絶縁体や強誘電体を記憶素子に使用し、高速化や書込み回数の制約を改善できるが、電荷の漏洩が増えて長期の記憶維持が困難になる。また、微細化や多値化によっても記憶維持が困難になっている。読書き操作時の電荷の漏洩をある程度容認し得る装置を提供する。

【解決手段】漏洩した電荷はリフレッシュ操作で回復して、動作マージンが不足気味の記憶素子でも利用可能にする。記憶ブロック毎の読書き回数をカウンタで集計して、読書き回数が一定の値を超過した記憶ブロックをリフレッシュする。

(もっと読む)

半導体装置およびその製造方法

【課題】コントロールゲート電極とメモリゲート電極間に発生する電界強度を緩和してリーク電流を低減できる、コントロールゲート電極とメモリゲート電極が近接するスプリットゲート型不揮発性メモリを提供する。

【解決手段】半導体基板1S上にゲート絶縁膜GOXが形成され、このゲート絶縁膜GOX上にコントロールゲート電極CGが形成されている。そして、コントロールゲート電極CGの右側の側壁には、積層絶縁膜を介してメモリゲート電極MGが形成されている。このとき、コントロールゲート電極CGの上端部にバーズビークBVが形成されている。この結果、コントロールゲート電極CGの上端部と、メモリゲート電極MGの上端部が、バーズビークBV分だけ離れるので電界強度の緩和を図ることができ、コントロールゲート電極CGとメモリゲート電極MG間を流れるリーク電流を低減できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】メモリセルを高集積度化することができるチャージトラップ型フラッシュ構造の不揮発性半導体記憶装置を提供する。

【解決手段】半導体記憶装置50は、接地線SUBLとしての半導体基板層1aの第1主面(表面)上に、素子分離層2、ソース電極3a、ソース電極3b、ドレイン電極4a、及びドレイン電極4bを柱状にエッチング開口した開口部5が互いに離間して複数設けられる。開口部5には、半導体基板層1b、積層膜6、及びゲート電極7が埋設され、開口部5の内側には半導体基板層1bが半導体基板層1aと接するように設けられる。半導体基板層1bの内側には、トンネル酸化膜、電荷蓄積膜、電流遮断膜から構成される積層膜6が設けられる。積層膜6の内側にはゲート電極7が埋設される。半導体基板層1bにはソース層8とドレイン層9が垂直方向に複数設けられ、チャネルが垂直方向に設けられるメモリトランジスタが積層形成される。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】メモリセルにMONOS構造が用いられる場合においても、メモリセル領域にバーズビークが形成されるのを防止しつつ、選択トランジスタのゲート絶縁膜の電界を緩和する。

【解決手段】メモリセルアレイ1にマトリクス状に配置されたメモリセルMCのチャージトラップ膜として、シリコン窒化膜を用いた上で、メモリセルMCとともにNANDセルMSに含まれる選択トランジスタSG1、SG2のゲート絶縁膜として、シリコン酸窒化膜を用いる。

(もっと読む)

薄膜トランジスタを利用して不揮発性メモリとする方法およびその装置

【課題】薄膜トランジスタ(TFT)のベースを利用して電荷を保存し、不揮発性メモリとする方法を提供する。

【解決手段】薄膜トランジスタ10を利用し、そのうち薄膜トランジスタ10は中間がベース21、両端がそれぞれドレイン電極22、ソース電極23である半導体層20を備え、絶縁表面31を備えた基板30上に設置され、ゲート電極絶縁層41が前記半導体層20上に設置され、ゲート電極40がゲート電極絶縁層41上に設置され、電子がゲート電極40の電場作用下で、熱電子界放射により電子正孔対を形成し、電子正孔対がゲート電極40の垂直電場により分離され、複数のキャリア(nチャネルでいうと正孔)が薄膜トランジスタ10のベース21に注入され、薄膜トランジスタ10の閾値電圧の変化を引き起こし、書き込み動作が完了する。

(もっと読む)

半導体装置の製造方法

【課題】不揮発性メモリを備える半導体装置において、不揮発性メモリを構成するメモリセルの加工精度を向上することができる技術を提供する。

【解決手段】ポリシリコン膜PF1とダミーゲート電極DMY1を覆うようにポリシリコン膜PF2を形成する。このとき、ポリシリコン膜PF2は、段差DIFおよびギャップ溝GAPの形状を反映して形成される。特に、ギャップ溝GAPを覆うポリシリコン膜PF2には凹部CONが形成される。続いて、ポリシリコン膜PF2上に反射防止膜BARCを形成する。このとき、流動性の高い反射防止膜BARCは、段差DIFの高い領域から低い領域に流出するが、凹部CONに充分な反射防止膜BARCが蓄積されているので、流出する反射防止膜BARCを補充するように凹部CONから反射防止膜BARCが供給される。

(もっと読む)

半導体装置の製造方法

【課題】ウエハの設置状態にかかわらず、ドレイン領域およびソース領域をゲート電極に対して対称に形成することにより、単一セルにおける電流の対称性を確保する。

【解決手段】

半導体基板上にゲート酸化膜を形成する。ゲート酸化膜上にゲート電極を形成する。半導体基板の表面のゲート電極を挟む位置にドレイン領域およびソース領域を形成する。ドレイン領域およびソース領域を形成する工程は、半導体基板をイオン注入装置の搭載ステージ上に載置して、ゲート電極をマスクとして半導体基板の表面に不純物イオンを注入する第1のイオン注入工程と、搭載ステージの載置面内において、半導体基板を搭載ステージに対して180°回転させた向きに搭載ステージ上に再載置して、ゲート電極をマスクとして半導体基板の表面に不純物イオンを注入する第2のイオン注入工程と、を含む。

(もっと読む)

結晶半導体の製造方法およびそれを用いた半導体素子の製造方法

【課題】低温で結晶半導体を形成可能な結晶半導体の製造方法を提供する。

【解決手段】80〜240nmの膜厚を有するa−Ge膜2が基板1上に形成される(工程(b)参照)。そして、約10nmの膜厚を有するSiO2膜3がa−Ge膜2上に形成される(工程(c)参照)。その後、約90nmの膜厚を有するPt薄膜4がスパッタリングまたは蒸着によってSiO2膜3上に形成される(工程(d)参照)。そして、Pt薄膜4は、水素リモートプラズマによって処理される(工程(e)参照)。

(もっと読む)

101 - 120 / 596

[ Back to top ]