Fターム[5F083EP17]の内容

半導体メモリ (164,393) | EPROM、EEPROMの構造 (21,423) | 電荷蓄積機構 (5,261) | トラップ蓄積型 (2,146)

Fターム[5F083EP17]の下位に属するFターム

MNOS型(MONOS型を含む) (1,550)

Fターム[5F083EP17]に分類される特許

21 - 40 / 596

半導体装置及びその製造方法

【課題】アモルファス半導体膜の結晶化を低温で短時間に行うことができ、大粒径の結晶粒を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態による半導体装置の製造方法では、基板上にアモルファス半導体膜を形成する。さらに、前記方法では、前記基板上にマイクロ波を照射することにより、前記アモルファス半導体膜をアニールして、前記アモルファス半導体膜から多結晶半導体膜を形成する。さらに、前記方法では、前記多結晶半導体膜をチャネルとするトランジスタを形成する。

(もっと読む)

3次元不揮発性メモリ素子及びその製造方法

【課題】エンハンスドモード(Enhanced Mode)で駆動される3次元不揮発性メモリ素子及びその製造方法を提供する。

【解決手段】第1パイプゲート、前記第1パイプゲート上に形成された第2パイプゲートおよび前記第1パイプゲートと前記第2パイプゲートとの間に介在され、第1層間絶縁膜を含むパイプゲートと、前記パイプゲート上に交互に積層された複数のワードラインおよび複数の第2層間絶縁膜と、前記パイプゲート内に埋め込まれたパイプチャンネルと、前記パイプチャンネルに連結されながら前記複数のワードラインおよび前記複数の第2層間絶縁膜を貫通する複数のメモリセルチャンネルと、を含むことを特徴とする3次元不揮発性メモリ素子。

(もっと読む)

ナノ結晶を有する半導体デバイスを形成する方法

【課題】

ナノ結晶を有する半導体デバイスを形成する方法を提供する。

【解決手段】

ナノ結晶を有する半導体デバイス10を形成する方法は、基板12を設けるステップと、基板の表面の上方に第1絶縁層14を形成するステップと、第1絶縁層上に第1の複数のナノ結晶26(21、22)を形成するステップと、第1の複数のナノ結晶上に第2絶縁層28を形成するステップと、第2絶縁層に第1材料を注入するステップと、第1材料をアニールして第2絶縁層内に第2の複数のナノ結晶34(36、37)を形成するステップとを含む。この方法は、より高いナノ結晶密度を有する不揮発性メモリの電荷格納層を提供するために使用され得る。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

トンネル障壁の上に電界分布層を有する電荷捕獲装置

【課題】チャネル幅寸法に沿った電荷捕獲構造の電荷密度が一様でない場合でもチャネル幅寸法に沿ってしきい値電圧を一様に維持したフラッシュメモリセルおよびフラッシュメモリセルの製造方法を提供する。

【解決手段】ソース領域及びドレイン領域を有する表面を有し、前記ソース領域及び前記ドレイン領域がチャネル領域によって分離された半導体基板と、前記チャネル領域の上の前記基板の表面上に配置された3nmを超える実質的なゲート絶縁膜厚を有するトンネル障壁絶縁体構造105、前記トンネル障壁絶縁体構造及び前記チャネル領域の上に配置された導電層101、前記導電層及び前記チャネル領域の上に配置された電子捕獲構造106、並びに前記電子捕獲構造及び前記チャネル領域の上に配置された上側絶縁体構造107を有する、前記チャネル上の多層スタックと、前記上側絶縁体構造及び前記チャネル領域の上に配置された上側導電層108とを具える。

(もっと読む)

有機分子メモリ

【課題】電荷保持特性に優れた有機分子メモリを提供する。

【解決手段】実施の形態の有機分子メモリは第1の導電層と、第2の導電層と、第1の導電層と第2の導電層との間に設けられ、電荷蓄積型分子鎖または抵抗変化型分子鎖を含み、電荷蓄積型分子鎖または前記抵抗変化型分子鎖が縮合多環系の基を備える有機分子層と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の構成材料の特性劣化を抑制しつつ、基板とゲート絶縁膜との界面の界面準位密度を効率的に低減することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、基板100上に、ゲート絶縁膜102とゲート電極103とを含むトランジスタを形成する。さらに、基板100上に1層の配線層110を形成する処理と、1層の配線層110を配線パターンに加工する処理を1回以上行うことにより、基板100上に、1層以上の配線層113,115を含む配線構造を形成する。さらに、基板100上に、1層以上の配線層113,115のうちの少なくとも1層の配線層110が配線パターンに加工された後に、基板100上にマイクロ波を照射して基板100のアニールを行う。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

フラッシュEEPROM(FLASHEEPROMMEMORY)の消去方法

【課題】電荷の蓄積を制御することによりメモリセルを消去するフラッシュEEPROMの消去方法を提供する。

【解決手段】フラッシュメモリの消去方法は、F/Nトンネリング期間において、ウェル電極と第二半導体領域に対し正極性の第一電圧バイアスを印加し、且つコントロールゲート電極に対し負極性の第二電圧バイアスを印加するステップと、F/Nトンネリング期間のあとのトラップ減少期間において、ウェル電極と第二半導体領域に対し正極性の第三電圧バイアスを印加し、且つコントロールゲート電極に対し第一ゼロ電圧バイアスを印加するステップと、トラップ減少期間のあとのトラップアシストトンネリング期間において、コントロールゲート電極に対し負極性の第四電圧バイアスを印加し、且つウェル電極と第二半導体領域に対し第二ゼロ電圧バイアスを印加するステップと、を有する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】複数のメモリセルを3次元状に配置し、かつ、メモリセルにMONOS型トランジスタを使用するNAND型不揮発性メモリにおいて、データ保持特性の劣化を抑制することができる技術を提供する。

【解決手段】ギャップ絶縁層GIL1の右端部側に凹部CUが形成されている。このとき、この凹部CUの形状を反映するように、凹部CUの内部に上部電位障壁層EB2と電荷蓄積層ECが形成されており、この凹部CUの形状を反映した電荷蓄積層ECの内側に形成される下部電位障壁層EB1によって、凹部CUが完全に埋め込まれている。このため、凹部CUを埋め込んだ下部電位障壁層EB1の表面は平坦になっており、この平坦になっている下部電位障壁層EB1の内側に柱状半導体部PSが形成される。

(もっと読む)

太陽電池

【課題】高温ポストアニールのステップを必要とせず、従来の低温ポリシリコン薄膜トラ

ンジスタと集積可能な、高効率の太陽電池を提供する。

【解決手段】基板と、前記基板上に形成された第1導電層と、前記第1導電層上に形成されたNドープまたはPドープの第1半導体層と、前記第1半導体層上に形成され、複数のレーザー誘起凝集シリコンナノドットを有するシリコンリッチ誘電体層と、前記シリコンリッチ誘電体層上に形成されたNドープまたはPドープの第2半導体層と、前記第2半導体層上に形成された第2導電層と、を含み、前記基板、前記第1導電層、および前記第1半導体層と、前記第2半導体層および前記第2導電層と、のいずれかは、透明材料からなることを特徴とする太陽電池。

(もっと読む)

帯電体並びにそれを用いた電界効果トランジスタ及びメモリ素子

【課題】 フローティングゲートメモリやMNOSメモリのような極薄膜の絶縁層を必要とせず、印刷、塗布でメモリ素子が製造可能となる簡便で、注入電荷量の制御が容易な帯電体、並びにこの帯電体をゲート絶縁膜に用いてFETを作製することにより、閾値電圧制御が可能で、長時間制御された閾値電圧状態を保持可能なFET及びメモリ素子を提供する。

【解決手段】 電荷注入が生じる電界強度(以降、電荷注入耐圧)および絶縁耐圧がそれぞれECI,HおよびEBHである絶縁体(以下,高電荷注入耐圧材料)と、その電荷注入耐圧ECI,LがECI,L < ECl,Hの関係にある絶縁体(以下、低電荷注入耐圧材料)の二種類の絶縁体を積層した絶縁物で、高電荷注入耐圧材料と低電荷注入耐圧材料のそれぞれに接し離れた2枚の電極にECI,L < |E| < EBH の電界強度で電圧を印加して低電荷注入耐圧材料側から電荷を絶縁体内に注入して帯電させる帯電体。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】特性を向上させる不揮発性メモリを有する半導体装置を提供する。

【解決手段】半導体装置を、制御ゲート電極CGと、制御ゲート電極CGと隣合うように配置されたメモリゲート電極MGと、絶縁膜3と、その内部に電荷蓄積部を有する絶縁膜5と、を有するよう構成する。このうち、メモリゲート電極MGは、絶縁膜5上に位置する第1シリコン領域6aと、第1シリコン領域6aの上方に位置する第2シリコン領域6bと、を有するシリコン膜よりなり、第2シリコン領域6bは、p型不純物を含有し、第1シリコン領域6aのp型不純物の濃度は、第2シリコン領域6bのp型不純物の濃度よりも低く構成する。

(もっと読む)

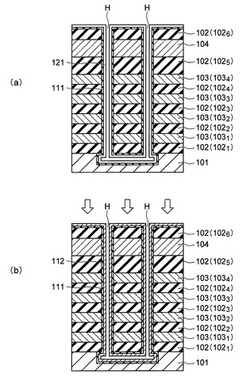

3次元半導体素子及びその製造方法

【課題】工程不良を無くして収率を向上させることができる3次元半導体素子及びその製造方法が提供される。

【解決手段】3次元(3D)半導体メモリー素子は、基板に隣接する下段から上段まで伸張して、複数個のメモリーセルと連結された垂直チャンネルと、前記複数個のメモリーセルを有し、前記基板上に配置された階段形構造のゲートスタック形態にアレイされたセルアレイと、を含む。前記ゲートスタックは、前記下段に隣接する下部非メモリートランジスターに連結された下部選択ラインを含む下部膜と、前記上段に隣接する上部非メモリートランジスターに各々連結され、互いに連結されて単一の導電性ピースになって上部選択ラインをなす導電ラインを有する複数個の上部膜と、各々ワードラインを有し、セルトランジスターと連結され、前記下部選択ラインと前記上部選択ラインの間に配置される複数個の中間膜と、を含む。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】集積度を向上させた不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1積層構造体と、第1半導体層と、第1有機膜と、第1半導体側絶縁膜と、第1電極側絶縁膜と、を備えた不揮発性半導体記憶装置が提供される。前記第1積層構造体は、第1方向に沿って積層された複数の第1電極膜と、前記複数の第1電極膜どうしの間に設けられた第1電極間絶縁膜と、を有する。前記第1半導体層は、前記複数の第1電極膜の側面に対向する。前記第1有機膜は、前記複数の第1電極膜の前記側面と前記第1半導体層との間に設けられ有機化合物を含む。前記第1半導体側絶縁膜は、前記第1有機膜と前記第1半導体層との間に設けられる。前記第1電極側絶縁膜は、前記第1有機膜と前記複数の第1電極膜の前記側面との間に設けられる。

(もっと読む)

3次元半導体記憶素子

【課題】優れた信頼性を有し、高集積化のために最適化された3次元半導体記憶素子が提供される。

【解決手段】本発明の素子によれば、積層構造体が基板上に配置されて第1の方向に延長される。積層構造体は交互に反復的に積層されたゲートパターン及び絶縁パターンを含む。垂直形活性パターンが積層構造体を貫通する。積層構造体は第1の部分及び第2の部分を含み、積層構造体の第2の部分は第1の方向と垂直である第2の方向に第1の部分より小さい幅を有する。積層構造体の第2の部分の横にストラッピングコンタクトプラグが配置されて、共通ソース領域と接触される。

(もっと読む)

半導体素子およびその製造方法

【課題】二酸化シリコンとシリコンとの良好な界面特性を有し、絶縁基板上に作製された半導体素子を提供する。

【解決手段】半導体素子10は、多結晶シリコン膜4と、絶縁膜5,9と、金属量子ドット8とを備える。多結晶シリコン膜4は、絶縁基板1上に配置され、アモルファスシリコン膜を熱プラズマジェットによってアニールして作製される。絶縁膜5は、SiO2からなり、多結晶シリコン膜4に接して多結晶シリコン膜4上に形成される。金属量子ドット8は、Ptからなり、Pt薄膜を熱プラズマジェットによってアニールして絶縁膜5上に形成される。絶縁膜9は、SiO2からなり、金属量子ドット8を覆うように絶縁膜5上に形成される。

(もっと読む)

21 - 40 / 596

[ Back to top ]