Fターム[5F083ER03]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236) | トンネル注入 (539)

Fターム[5F083ER03]に分類される特許

121 - 140 / 539

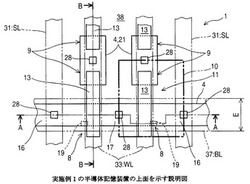

半導体記憶装置およびその制御方法

【課題】SOI構造の半導体記憶装置に電気的に書換え可能な不揮発性メモリを形成する手段を提供する。

【解決手段】第1の拡散層16、第2の拡散層17、前記第1および第2の拡散層間に配置された第3の拡散層、および第4の拡散層21と、前記第1および第2の拡散層とそれぞれ一部がオーバーラップし、前記第3の拡散層上から前記第4の拡散層にかけて延在するフローティングゲート電極13と、前記第1の拡散層および前記第3の拡散層に、共通の第1の電位を与える第1の制御線31と、前記第2の拡散層に、第2の電位を与える第2の制御線37と、前記第4の拡散層に、第3の電位を与える第3の制御線33と、を備え、前記フローティングゲート電極が前記第4の拡散層とオーバーラップした面積が、前記第2の拡散層とオーバーラップした面積よりも大きく、前記第1および第3の拡散層とオーバーラップした合計の面積よりも小さい。

(もっと読む)

Pチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法

【課題】書き換え電圧を低くできるようにしたPチャネル型不揮発性メモリ及び半導体装置、Pチャネル型不揮発性メモリの製造方法を提供する。

【解決手段】シリコン基板1に設けられたN型ウェル領域2と、N型ウェル領域2内で互いに離れた状態で設けられた第1のP型拡散領域(ソース)及び第2のP型拡散領域(ドレイン)と、第2のP型拡散領域上に設けられたトンネル絶縁膜14bと、N型ウェル領域2のうちの第1のP型拡散領域と第2のP型拡散領域とに挟まれた領域(即ち、チャネルとなる領域)上に設けられたゲート絶縁膜14aと、ゲート絶縁膜14a上からトンネル絶縁膜14b上にかけて連続して設けられた浮遊ゲート電極15と、を備え、第2のP型拡散領域はトンネル絶縁膜14bの直下の全領域に配置されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】動作の信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置にメモリセルアレイ及び制御回路を設け、メモリセルアレイには、それぞれ複数の絶縁膜及び電極膜が交互に積層された積層体を設け、この積層体に積層方向に延びる貫通ホールを形成し、その内部にシリコンピラーを埋設し、電極膜とシリコンピラーとの間に電荷蓄積膜を設ける。これにより、電極膜とシリコンピラーとの交差部分毎にメモリセルが形成される。そして、制御回路は、フォーマット時に、全てのメモリセルに値「0」を書き込み、全てのメモリセルに対して値「0」を消去する動作を行い、積層体の最上段に形成されたメモリセルに記憶された値を読み出し、値「0」が読み出されたメモリセルについては、消去動作が不良であったと判定し、以後不使用とする。

(もっと読む)

不揮発性半導体記憶装置

【課題】安定した消去状態が実現できる一括加工型3次元積層構成の不揮発性半導体記憶装置を提供する。

【解決手段】メモリ部MUと制御部CTUとを備える。メモリ部は、交互に積層された電極膜WLと電極間絶縁膜14とを有する積層構造体ML、積層構造体を貫通する半導体ピラーSP、電極膜WLと半導体ピラーと間の記憶層48、記憶層と半導体ピラーとの間の内側絶縁膜42、電極膜と記憶層との間の外側絶縁膜43、半導体ピラーに接続された第1配線W1、を有す。制御部は、消去動作の際に、第1期間に、第1配線を第1電位に、電極膜を第1電位よりも低い第2電位に設定する。その後、第2期間に、第1配線を第3電位に、電極膜を第3電位よりも低い第4電位に設定する。第2期間は第1期間よりも短い、及び、第3電圧と第4電圧との差は第1電位と第2電位との差よりも小さい、の少なくともいずれかである。

(もっと読む)

不揮発性半導体記憶装置

【課題】リーク電流を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリストリングMSは、直列接続されたメモリトランジスタMTr1〜MTr8を含む。制御回路AR2は、メモリトランジスタMTr1〜8からデータを読み出す。メモリストリングMSは、メモリトランジスタMTr1〜8のボディとして機能するU字状半導体層34と、U字状半導体層34を取り囲むように形成され、電荷を蓄積することによりデータを保持する電荷蓄積層33bと、電荷蓄積層33bを介してU字状半導体層34を取り囲むワード線導電層31a〜31dとを備える。制御回路AR2は、読み出し動作の際、非選択メモリストリングMSの中の少なくとも一つのメモリトランジスタMTr1〜MTr8のゲートに読み出しパス電圧Vreadを印加し、別のメモリトランジスタMTrのゲートには接地電位Vssを印加する。

(もっと読む)

不揮発性半導体記憶装置

【課題】集積度が高まった場合においても、読み出し電流の低下を抑制する3次元構造の半導体記憶装置を提供する。

【解決手段】メモリストリングMSの各々は、2本の柱状部CLmn、及びそれらの下端を連結する連結部JPmnを有するボディ半導体層SCmnを有する。ビット線BL、ソース線SLは、カラム方向を長手方向として交互に形成され、連結部JPmnは、カラム方向を長手方向として形成される。メモリストリングMSは、基板上においてジグザグ状に形成され、1本の柱状部CLmnに沿って形成される4個のメモリトランジスタMTrに接続されるワード線WLを共有する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルアレイ領域と周辺回路領域との間に生じる層間絶縁膜の段差を解消し、歩留まりの向上を図ることができる半導体装置を提供すること。

【解決手段】半導体基板1上で素子分離用絶縁膜2a、2bによって素子分離された複数の第1の素子10が形成された第1の領域4と、半導体基板1上で第1の領域4に隣接して配されるとともに、素子分離用絶縁膜2b、2cによって素子分離された複数の第2の素子20が形成され、第2の素子20の高さが第1の素子10の高さよりも低い第2の領域5と、第2の領域5にある素子分離用絶縁膜2b、2cの少なくとも一部の領域上に配設されたダミー絶縁膜6c、6dと、第1の領域4及び第2の領域5にわたって形成された層間絶縁膜7と、を備える。

(もっと読む)

固体撮像素子及び撮像装置

【課題】ドレイン領域等の不純物拡散領域からフローティングゲートに電荷が注入されてしまうことを防止でき、S/Nを向上できる固体撮像素子及び撮像装置を提供する。

【解決手段】半導体基板に配列された複数の画素部が配列され、画素部が、半導体基板に形成された光電変換部と半導体基板の上方に設けられた電荷蓄積領域と、電荷蓄積領域に電荷を蓄積させて、該電荷に応じた信号を読み出すトランジスタ構造とを備え、トランジスタ構造がソース領域及びドレイン領域を含み、ソース領域及びドレイン領域と光電変換部との間の半導体基板に、ソース領域及びドレイン領域と光電変換部との間で移動する電荷に対して電位勾配のポテンシャル障壁となる障壁層を備える。

(もっと読む)

半導体記憶素子の製造方法

【課題】金属ナノ結晶からなる離散的フローティングゲートを、移流集積法により形成する半導体記憶素子の製造方法を提供する。

【解決手段】製造方法は、シリコン基板1と、シリコン基板1上に形成されたトンネル絶縁膜に対向するように配置された第2の基板21との間に、金属ナノ粒子が分散された粒子分散液22を充填する充填工程と、トンネル絶縁膜の表面に沿った方向に、第2の基板21をシリコン基板1に対して相対的に移動させることにより、トンネル絶縁膜の表面における第2の基板21から露出した領域に形成される粒子分散液22のメニスカス領域23において、粒子分散液22の溶媒を蒸発させることにより、トンネル絶縁膜上に金属ナノ粒子を離散的に配置する。

(もっと読む)

メモリ半導体装置、その製造方法、及び動作方法

【課題】メモリ半導体装置、その製造方法及び動作方法を提供する。

【解決手段】メモリ半導体装置は、基板の上部面に垂直長軸を有し、2次元的に配列される複数の半導体パターン、及び複数の半導体パターンを横切る長軸を有しながら、複数の半導体パターン間で3次元的に配列される複数のワードラインを包含できる。

(もっと読む)

半導体メモリー装置のチャンネルをプリチャージする方法

【課題】プログラムディスターバンスが効果的に遮断されて高いデータ信頼性を有する3次元半導体メモリー装置のチャンネルをプリチャージする方法を提供する。

【解決手段】本発明による半導体メモリー装置のプログラム方法は、複数のビットラインの中でプログラムビットラインに連結される少なくとも1つのインヒビットストリングのチャンネルと、インヒビットビットラインに連結されるインヒビットストリングの中で少なくとも何れか1つのチャンネルとを共通ソースラインに供給されるプリチャージ電圧に充電する段階と、ワードライン電圧を複数のセルストリングに供給してプリチャージされたチャンネルをブースティングさせる段階と、を有する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高カップリング比を維持しつつ、浮遊ゲートの頂部のリーク電流を低減する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】トランジスタTRは、半導体層10に設けられた、ソース領域10sと、ドレイン領域10dと、ソース領域10sとドレイン領域10dとの間のチャネル領域10cと、チャネル領域10cの上に設けられたゲート絶縁膜30と、ゲート絶縁膜30の上に設けられ、側部40bと頂部40aとを有する電荷保持層(浮遊ゲート40)と、側部40b及び頂部40aを覆う電極間絶縁膜50と、電極間絶縁膜50の上に設けられた制御ゲート60と、を有する。制御ゲート60は、側部40bに対向する側部導電層60bと、頂部40aに対向し、仕事関数が、電荷保持層よりも高く、側部導電層60bよりも高い頂部導電層60aと、を有する。

(もっと読む)

チャージトラップ型メモリ装置における書き込み方法、消去方法及びチャージトラップ型メモリ装置

【課題】書き換え耐久性の高いチャージトラップ型メモリ装置を提供する。

【解決手段】シリコン基板上に、トンネル酸化膜、チャージトラップ膜、ブロッキング絶縁膜、ゲート電極が順次積層形成されており、前記ゲート電極に一方の極の電圧を印加することにより、前記シリコン基板より供給された電荷を、前記チャージトラップ膜にトラップし、情報の書き込みを行い、前記ゲート電極に他方の極の電圧を印加することにより、前記チャージトラップ膜にトラップされている電荷を引抜き、情報の消去を行うチャージトラップ型メモリ装置であって、前記トンネル酸化膜の膜厚は、3nm以下であることを特徴とするチャージトラップ型メモリ装置を提供することにより上記課題を解決する。

(もっと読む)

半導体装置、表示装置および電子機器

【課題】液晶パネルの表示品質を向上させることができると共に、高速動作することができる半導体装置を提供する。

【解決手段】D/Aコンバータの基準電圧発生回路71は、絶縁性基板と、この絶縁基板上に形成された不揮発性メモリ素子131,132,133,…およびTFT素子141,142,143,…,151,152,153,…を有する。D/Aコンバータのアナログバッファ回路は、基準電圧発生回路71から出力された基準電圧V0,V1,V2,V3,…を受ける。不揮発性メモリ素子131,132,133,…の素子特性の変更して、アナログバッファ回路のオフセット電圧を調整することが可能になっている。

(もっと読む)

不揮発性半導体記憶装置

【課題】チャネル界面付近の浅いエネルギー準位に捕獲された電荷を予め除去し、データ保持特性の良好な不揮発性半導体記憶装置を提供する。

【解決手段】メモリ部MUと、制御部CTUと、を備える不揮発性半導体記憶装置において、メモリ部は、第1方向に交互に積層された複数の電極膜WLと複数の電極間絶縁膜14とを有する積層構造体MLと、積層構造体MLを第1方向に貫通する半導体ピラーSPと、電極膜WLと半導体ピラーSPとの間に設けられた、内側絶縁膜42、記憶層及び外側絶縁膜と、半導体ピラーSPの一端と電気的に接続された配線と、を有す。制御部CTUは、消去動作の際に、配線を第1電位に設定しつつ、電極膜WLを第1電位よりも低い第2電位に設定する第1動作の後に、配線を第3電位に設定しつつ、電極膜WLを第3電位よりも高い第4電位に設定する第2動作を実施する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリホールの直径が均一な不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】シリコン基板10上にバックゲート電極13を形成し、バックゲート電極13の上面に凹部23を形成し、凹部23内に犠牲材を埋め込んだ後、絶縁膜14及び電極膜15を交互に積層して積層体11を形成する。次に、積層体11の中央部21にメモリホール24を形成し、その後、酸化処理を施す。これにより、メモリホール24の内面を起点として、電極膜15における絶縁膜14に接する部分が酸化され、その結果、中央部21において電極膜15が薄くなり、絶縁膜14が厚くなる。次に、積層体11の端部22において、電極膜15毎にステップ30を形成し、端部22を埋め込むように層間絶縁膜40を形成し、層間絶縁膜40中にステップ30に到達するようにプラグホール41を形成する。

(もっと読む)

新たな高速高密度NANDベース2T−NORフラッシュメモリ設計

【課題】高速高密度NANDベース2T-NORフラッシュメモリ設計の提供。

【解決手段】ツートランジスタNOR フラッシュメモリセルはNANDベース製造プロセスで製造された対称なソース及びドレイン構造を有する。該フラッシュセルはダブルポリNMOSフローティングゲートトランジスタで構成されたストレージトランジスタ、ダブルポリNMOSフローティングゲートトランジスタで構成されたアクセストランジスタ、短絡ポリ1及びポリ2を備えたポリNMOSトランジスタ或いはシングルポリ ポリ1又はポリ2NMOSトランジスタを包含する。該フラッシュセルはファウラー・ノードハイムチャネルトンネルスキームを使用しプログラム及び消去される。NANDベースフラッシュメモリデバイスは、ワードラインに垂直である平行なビットラインとソースラインと共に配置される。書き込みロウデコーダ及び読み出しロウデコーダがフラッシュメモリデバイスが、ページ、ブロック、セクタ又はチップ単位でのベリファイ、プログラム及び読み出し動作を伴うプリプログラムにおいてフラッシュメモリアレイに適宜電圧を供給するために設計される。

(もっと読む)

不揮発性半導体記憶装置及びディプレッション型MOSトランジスタ

【課題】トランジスタの耐圧を向上し、動作信頼性を向上出来る不揮発性半導体記憶装置及びディプレッション型MOSトランジスタを提供すること。

【解決手段】ゲート電極26と、第1不純物濃度を有するチャネル領域22と、第1不純物濃度よりも大きな第2不純物濃度を有するソース・ドレイン拡散領域21と、チャネル領域22とソース・ドレイン拡散領域21とが重複する領域に形成され、第2不純物濃度よりも大きな第3不純物濃度を有する重複領域24と、第2不純物濃度よりも大きな第4不純物濃度を有するコンタクト領域23と、ソース・ドレイン拡散領域21の一部領域内に形成され、第2不純物濃度よりも大きく且つ第4不純物濃度よりも小さい第5不純物濃度を有する不純物拡散領域27とを備え、不純物拡散領域27は、コンタクト領域23に接し且つ重複領域24に離隔するようにして形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】浮遊ゲート電極膜と制御ゲート電極膜との間に設ける電極間絶縁膜の絶縁特性をより一層改善することができる半導体装置およびその製造方法を提供する。

【解決手段】素子分離絶縁膜4の上面、浮遊ゲート電極膜6の側面及び浮遊ゲート電極膜6の上面に、シリコン窒化膜と同等以上の誘電率を有する高誘電率膜を含む複数層構造で構成された電極間絶縁膜7を形成し、この電極間絶縁膜7上に制御ゲート電極膜9を形成した半導体装置であって、浮遊ゲート電極膜6の上面と電極間絶縁膜7との間にシリコン酸化膜8を形成し、浮遊ゲート電極膜6の側面に電極間絶縁膜7の高誘電率膜を直接接触させるように構成した。

(もっと読む)

121 - 140 / 539

[ Back to top ]