Fターム[5F083ER07]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236) | CGから注入 (32)

Fターム[5F083ER07]に分類される特許

1 - 20 / 32

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

不揮発性半導体記憶装置

【課題】微細化された不揮発性半導体記憶装置で、隣接セル間の寄生容量によるセル間干渉とトランジスタ特性の劣化を従来に比して抑制する。

【解決手段】チャネル半導体上にゲート誘電体膜21、フローティングゲート電極22、トンネル誘電体膜23および制御ゲート電極24が順に積層され、フローティングゲート電極22と制御ゲート電極24は、トンネル誘電体膜23側に曲率を有する尖端部25,26を有する。また、トンネル誘電体膜23のキャパシタンスがゲート誘電体膜21のキャパシタンスと同等以下となるようにトンネル誘電体膜23とゲート誘電体膜21の厚さが調整される。さらに、制御ゲート電極24の尖端部26からフローティングゲート電極22に電子を注入する処理と、フローティングゲート電極22の尖端部26から制御ゲート電極24に電子を抜き取る処理とを、チャネル半導体と制御ゲート電極24との間に印加される電圧によって制御する。

(もっと読む)

不揮発性フラッシュメモリ

【課題】低消費電力、低減されたリーク問題、および単純なプロセスを伴った新規なフラッシュメモリ、新規なプログラミング方法、およびそのセンシングスキームを提供する。

【解決手段】ワード線218、第1のビット線204、および第2のビット線206を備えた不揮発性メモリセル200を動作させる方法は、メモリセル200をプログラミングする工程を有し、そのプログラミングする工程が、高い正電圧のバイアスを第1のビット線に印加し、接地バイアスを第2のビット線に印加し、高い負電圧のバイアスをワード線に印加することを備え、正帯電ホールが誘電体層212を介してトラッピング層214に突き抜けるようにする。

(もっと読む)

半導体装置

【課題】不揮発性メモリを構成するメモリセルのサイズを縮小できる技術を提供する。

【解決手段】本発明では、ソース線S1がメモリセルMC1AとメモリセルMC8Aで共通となっている。これにより、メモリセルMC1AやメモリセルMC8Aごとに電気的に独立したソース線を設ける必要がなく、メモリセルのサイズを縮小化することができる。具体的に、共通するソース線S1は、ビット線D1やビット線D8と並行するように配置されているのではなく、選択ゲート線CGL1やメモリゲート線MGL1と並行するように延在している。これにより、メモリセルMC1A〜メモリセルMC8A間の間隔を狭めることができるので、メモリセルアレイ全体の占有面積を縮小化することができる。このソース線S1は、メモリセルMC1B〜メモリセルMC8Bとも共通化されている。

(もっと読む)

半導体記憶装置およびその制御方法

【課題】SOI構造の半導体記憶装置に電気的に書換え可能な不揮発性メモリを形成する手段を提供する。

【解決手段】第1の拡散層16、第2の拡散層17、前記第1および第2の拡散層間に配置された第3の拡散層、および第4の拡散層21と、前記第1および第2の拡散層とそれぞれ一部がオーバーラップし、前記第3の拡散層上から前記第4の拡散層にかけて延在するフローティングゲート電極13と、前記第1の拡散層および前記第3の拡散層に、共通の第1の電位を与える第1の制御線31と、前記第2の拡散層に、第2の電位を与える第2の制御線37と、前記第4の拡散層に、第3の電位を与える第3の制御線33と、を備え、前記フローティングゲート電極が前記第4の拡散層とオーバーラップした面積が、前記第2の拡散層とオーバーラップした面積よりも大きく、前記第1および第3の拡散層とオーバーラップした合計の面積よりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極から電荷蓄積層に電荷を注入する不揮発性メモリにおいて、従来のゲート構造に比べて電荷の注入効率、電荷保持特性および信頼性を共に向上させる。

【解決手段】電荷蓄積層を構成する窒化シリコン膜に電子および正孔を注入し、トータルの電荷量を変えることによって書き込み・消去を行う不揮発性メモリにおいて、ゲート電極からの電荷注入を高効率で行うために、メモリセルのゲート電極を、ノンドープのポリシリコン層54とメタル材料電極層59の2層膜で構成する。

(もっと読む)

半導体集積回路装置

【課題】不揮発性メモリにおいて、データの書き換え回数増加時における動作信頼性を向上できる技術を提供する。

【解決手段】基板1上に、ボトム酸化膜7Aと電荷蓄積層8Aとトップ酸化膜9Aからなる積層絶縁膜を介して、ゲート電極9Aが形成され、ボトム酸化膜7Aの膜厚はトップ酸化膜9Aの膜厚よりも厚く形成されている。このように構成されているメモリセルにおいて、書き込みおよび消去となる電荷蓄積層8Aへの電荷のやり取りは、ゲート電極10Aと電荷蓄積層8Aとの間で行う。

(もっと読む)

不揮発性半導体メモリ及びデータプログラム/消去方法

【課題】電荷トラップ型の不揮発性半導体メモリにおいて、消費電流を低減すること。

【解決手段】不揮発性半導体メモリは、半導体基板1、第1ゲート電極WG、第2ゲート電極CG、電荷トラップ膜22、及びトンネル絶縁膜23を備える。第1ゲート電極WGは、半導体基板1の表面上に第1ゲート絶縁膜10を介して形成される。第2ゲート電極CGは、半導体基板1の表面上に第2ゲート絶縁膜20を介して形成され、第1ゲート電極WGと絶縁膜20を介して隣接する。電荷トラップ膜22は、半導体基板1と第1ゲート電極WGと第2ゲート電極CGとに囲まれたトラップ領域RT中に少なくとも形成される。トンネル絶縁膜23は、電荷トラップ膜22と第2ゲート電極CGとの間に形成される。プログラムあるいは消去において、FNトンネル方式により、第2ゲート電極CGから電荷トラップ膜22へトンネル絶縁膜23を通して電子が注入される

(もっと読む)

半導体記憶装置およびその製造方法

【課題】SOI構造の半導体記憶装置のフローティングゲート電極に短時間で電荷を注入する手段を提供する。

【解決手段】半導体記憶装置が、支持基板と、支持基板上に形成された埋込み酸化膜と、埋込み酸化膜上に形成されたSOI層とで形成された半導体基板と、半導体基板に設定されたトランジスタ形成領域およびキャパシタ形成領域のSOI層の間を絶縁分離する素子分離層と、トランジスタ形成領域のSOI層に形成されたソース層とドレイン層、およびこれらの間のチャネル領域を有するMOSFETと、キャパシタ形成領域のSOI層に形成された、ソース層と同じ型の不純物を拡散させたキャパシタ電極を有するMOSキャパシタと、MOSキャパシタのキャパシタ電極の周縁部に形成された、埋込み酸化膜に向かって拡大する傾斜した凹面を有する突起部と、MOSFETのチャネル領域上から、キャパシタ電極のMOSFET側の端部の突起部上に延在し、チャネル領域およびキャパシタ電極にゲート絶縁膜を挟んで対向するフローティングゲート電極とを備える。

(もっと読む)

不揮発性半導体記憶装置およびその動作方法

【課題】メモリセルに記憶された情報が破壊されるディスターブの発生が抑制された不揮発性半導体記憶装置およびその動作方法を提供する。

【解決手段】不揮発性半導体記憶装置は、シリコン基板1aと、第1および第2ソース/ドレイン領域SDLa,SDRaと、電荷トラップ層CTと、ゲート電極層GEとを備えている。電荷トラップ層CTは第1および第2ソース/ドレイン領域SDLa,SDRaに挟まれるシリコン基板1aの主表面上に設けられている。ゲート電極層GEは、電荷トラップ層CT上にp型半導体により形成され、かつ書込動作を行なうために電荷トラップ層CTに正孔を注入することができるように構成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】SOI構造の半導体記憶装置のフローティングゲート電極に短時間で電荷を注入する手段を提供する。

【解決手段】絶縁膜3上に形成された半導体層4とで形成された半導体基板と、半導体基板に設定されたトランジスタ形成領域の半導体層に形成されたソース層18とドレイン層19、およびこれらの間のチャネル領域を有するMOSFETと、半導体基板に設定されたキャパシタ形成領域の半導体層に形成された、ソース層と同じ型の不純物を拡散させたキャパシタ電極23を有するMOSキャパシタと、を備えた半導体記憶装置であって、MOSキャパシタのキャパシタ電極23を多角形に形成して、その周囲に絶縁膜に向かって拡大する斜面を設け、MOSFETのチャネル領域上から、キャパシタ電極23のMOSFET側の端部の角部上に延在し、チャネル領域およびキャパシタ電極にゲート絶縁膜を挟んで対向するフローティングゲート電極16を設ける。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜中に電荷蓄積部を含む不揮発性メモリセルを有する半導体装置において、不揮発性メモリ領域の面積を縮小する。

【解決手段】メモリゲート電極11Aに、局所的に電界が集中するコーナー部11cnを設け、メモリゲート電極11A中の電荷をFNトンネル動作によりゲート絶縁膜2a中の電荷蓄積部に注入する消去方式を用いる。FNトンネルにより消去時の消費電流を低減できるため、メモリモジュールの電源回路面積を低減できる。また、書込みディスターブ耐性を向上できるために、より簡易なメモリアレイ構成を採用してメモリアレイ面積を低減できる。両者の効果を併せてメモリモジュールの面積を大幅に低減し製造コストを低減できる。また、書込み消去の注入電荷中心が一致するため書換え耐性が向上する。

(もっと読む)

メモリデバイス

【課題】書込、読み出し、消去時間を改善した、トンネル障壁構造を有するメモリデバイスを提供する。

【解決手段】メモリデバイスは、制御電極9からトンネル障壁構造2を通り抜けて電荷を書き込むメモリノード1を有する。この蓄積された電荷はソース/ドレイン経路4の伝導性に影響を与え、この経路の伝導性をモニターすることによりデータが読み出せる。電荷障壁構造は多重トンネル障壁構造により構成される。この障壁構造は、メモリノードを形成するシリコンの多結晶層1を被覆する、厚さ3nmのポリシリコン層16と厚さ1nmのSi3N4層15を交互に積層したものからなる。ショットキ障壁構造、および電気絶縁マトリクス内に分散された、メモリノードとして機能する伝導性のナノスケール伝導島30,36,44を含む他の障壁構造2も開示されている。

(もっと読む)

有機電界効果トランジスタ

【課題】有機FETの応用の一つとして、外部からの刺激、例えば、外部からの光に応答する光メモリのようなメモリ機能を有する、外部刺激応答性素子の基本的な原理・構成を提供すること。

【解決手段】有機半導体層、ソース電極、ドレイン電極及びゲート電極を有し、該ソース電極と該ドレイン電極の間のチャネル領域が該有機半導体層からなり、該有機半導体層と該ゲート電極がゲート絶縁層によって隔てられている有機電界効果トランジスタにおいて、前記ゲート電極が、前記ゲート絶縁層側から順番に配置された、フローティングゲート電極、光照射等の外部刺激に応答して導電性となる性質を有する第2絶縁層、コントロールゲート電極から構成されていることを特徴とする有機電界効果トランジスタである。

(もっと読む)

半導体記憶装置

【課題】トンネル絶縁膜の膜質の劣化を防止し、且つメモリセルアレイ及び周辺回路の動作速度の低下を防止する不揮発性半導体記憶装置を提供する。

【解決手段】複数個のメモリセルトランジスタ及びそのメモリセルトランジスタを選択する選択トランジスタを配置したメモリセルアレイと、メモリセルアレイを制御する周辺回路とを備える半導体記憶装置であって、メモリセルトランジスタは、ゲート絶縁膜12と、ゲート絶縁膜12上の浮遊ゲート電極13と、浮遊ゲート電極13上に配置され、半導体記憶装置のデータ書込み及びデータ消去動作における電界印加時の通過電荷量がゲート絶縁膜12より多い電極間絶縁膜14と、電極間絶縁膜14上の制御ゲート電極15とを備える。

(もっと読む)

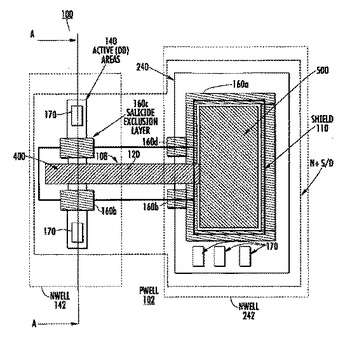

フローティングゲートトンネリング素子構造体のシールド

フローティングゲートトンネリング素子をシールドする方法とその構造体。標準的なCMOSプロセスを用いて、電界酸化物に囲まれた基板内に形成された第1および第2のドープウェル領域により定義される2つの活性領域内のゲート酸化物上にフローティングゲートを配置する工程と、前記フローティングゲートを囲むようにフローティングゲートシールド層を形成する工程を含む方法。前記フローティングゲートは、前記第1のドープウェル領域内の活性領域上の第1のフローティングゲート部および前記第2のドープウェル領域内の活性領域上の第2のフローティングゲート部を含む。前記第1のドープウェル領域と前記第1のフローティングゲート部との間にファウラーノルドハイムトンネリングのための適当な電圧カップリングが発生しうるよう、前記第1のフローティングゲート部は第2のフローティングゲート部より実質的に小さくなっている。トンネリングの方向は、前記ドープウェル領域の1つに高電圧を印加することにより決定される。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置に設けられた不揮発性メモリ回路部の面積を小さくする。

【解決手段】フラッシュメモリの形成領域の半導体基板1Sのn型の埋込ウエルDNW内にp型のウエルHPW1〜HPW3を互いに分離した状態で設け、そのウエルHPW1〜HPW3にそれぞれ容量部C、データ書き込み・消去用の電荷注入放出部CWEおよびデータ読み出し用のMIS・FETQRを配置した。容量部Cは、データ書き込み・消去用の電荷注入放出部CWEとデータ読み出し用のMIS・FETQRとの間に配置した。データ書き込み・消去用の電荷注入放出部CWEでは、チャネル全面のFNトンネル電流によりデータの書き込みおよび消去を行う。

(もっと読む)

不揮発性メモリ素子の動作方法

【課題】メモリ素子の信頼性が浅いトレンチ隔離構造によって生じるバードビーク効果によって影響されず、動作速度が非常に速い、メモリ素子の動作方法を提供すること。

【解決手段】不揮発性メモリ素子の動作方法を提供する。素子は、半導体基板、スタック層、および基板の表面下に配置し、チャネル領域によって分離されたソース領域とドレイン領域を備えたメモリセルを有する。スタック層は、チャネル領域上に配置した絶縁層、絶縁層上に配置した電荷蓄積層、電荷蓄積層上の多層トンネリング誘電体構造、および多層トンネリング誘電体構造上に配置したゲートを有する。ゲートに負のバイアスを供給し、−FNトンネリングによって、多層トンネリング誘電体構造を介して電荷蓄積層に電子を注入し、素子の閾値電圧を増大させる。ゲートに正のバイアスを供給し、+FNトンネリングによって、多層トンネリング誘電体構造を介して電荷蓄積層に正孔を注入し、素子の閾値電圧を減少させる。

(もっと読む)

半導体記憶装置

【課題】近接セル間干渉の影響を低減した半導体記憶装置を提供する。

【解決手段】シリコン基板4上に第一の絶縁膜5aを介して面方向に所定間隔で形成された浮遊ゲート6a層と、当該浮遊ゲート6a層上に第二の絶縁膜9を介して形成された制御ゲート10a層とを備えることとし、シリコン基板4上の浮遊ゲート6a層間に第三の絶縁膜5bを介して選択エピ層12が形成されるようにする。このような構成とすることにより、浮遊ゲート6a層間の静電容量を低減させ、隣接セル間干渉の影響を低減することが可能となる。

(もっと読む)

1 - 20 / 32

[ Back to top ]