Fターム[5F083FR02]の内容

半導体メモリ (164,393) | 強誘電体メモリ (1,733) | キャパシタを有するもの(破壊読出型) (1,245) | 1Tr/1C型 (791)

Fターム[5F083FR02]に分類される特許

21 - 40 / 791

半導体装置の製造方法

【課題】基板に電圧を印加して基板にダメージを及ぼすことなく、当該基板における、大型基板において特に顕在化する複雑な態様の反りの発生部位及び発生状態を容易且つ正確に特定する。そして、大型基板でも確実なチャッキングに供することを可能とする。

【解決手段】センサ部2は、搭載面1aの中央部分に設けられた第1のセンサ群11と、第1のセンサ群11を囲む第2のセンサ群12と、第2のセンサ群12を囲む第3のセンサ群13とを有する。第1のセンサ群11は、基板面の中央部分に対応して設けられた1つの静電容量センサ10aから、第2のセンサ群12は、第1のセンサ群11を同心状に囲む複数の静電容量センサ10aから、第3のセンサ群13は、第2のセンサ群12を同心状に囲み、搭載面1aの周縁の近くに設けられた複数の静電容量センサ10aを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】所望の特性を維持しつつ強誘電体膜のより一層の薄膜化が可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された強誘電体キャパシタ62は、下部電極48と、強誘電体特性を備えた誘電体膜(強誘電体膜)50と、上部電極60とを有する。上部電極50は、Ir等の導電材料を添加して導電性を付与した強誘電体材料により形成された導電体酸化物膜52を備え、この導電体酸化物膜52が誘電体膜50に接している。これにより、誘電体膜50と上部電極膜60との間に常誘電体層が発生することが抑制され、所望の特性を維持しつつ誘電体膜50のより一層の薄膜化が可能になる。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜を薄膜化して低電圧の動作を可能にしつつ、飽和反転電荷量を増大ささせる。

【解決手段】半導体装置は、下部電極41と、強誘電体膜36と、上部電極35とから形成されるキャパシタ42を有する。強誘電体膜36は、PZTから形成され、膜厚方向の中央部分のTiの含有量が他の領域の比べて多くなっている。Tiの分布は、膜厚方向の中央から上下の電極35,41に向けて減少するような分布である。さらに、Srなどのドーパント元素の含有量が、下部電極41との界面で最も多く、上部電極35に向けて減少する分布を有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体記憶装置に係り、特に、高集積化されたDRAMを、少ない工程数で、且つ微細なセル面積で実現できる半導体記憶装置及びその製造方法を提供する。

【解決手段】 半導体基板10に形成されたメモリセルトランジスタと、メモリセルトランジスタのゲート電極20の上面及び側面を覆う絶縁膜42と、ソース拡散層24上に開口したスルーホール40と、ドレイン拡散層26上に開口したスルーホール38とが形成された層間絶縁膜36と、スルーホール40内壁及び底部に形成され、ソース拡散24層に接続されたキャパシタ蓄積電極46と、キャパシタ蓄積電極46を覆うキャパシタ誘電体膜48と、キャパシタ誘電体膜48を覆うキャパシタ対向電極54とを有するキャパシタと、スルーホール38の内壁及び底部に形成され、ドレイン拡散層と接続されたコンタクト用導電膜44とにより構成する。

(もっと読む)

スパッタターゲット

【課題】バリア膜としての特性や品質に優れるTi−Al−N膜を再現性よく形成することを可能にしたスパッタターゲットを提供する。

【解決手段】Alを1〜30原子%の範囲で含有するTi−Al合金により構成されたスパッタターゲットであって、前記Ti−Al合金中のAlは、Ti中に固溶した状態、およびTiと金属間化合物を形成した状態の少なくとも一方の状態で存在しており、かつ前記Ti−Al合金の平均結晶粒径が500μm以下であると共に、ターゲット全体としての結晶粒径のバラツキが30%以内、前記Ti−Al合金の平均酸素含有量が1070ppmw以下であることを特徴とするスパッタターゲット。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】容量絶縁膜である強誘電体のアニール工程を経ても、PchMOS型トランジスタのVth変動を抑制することができる半導体記憶装置およびその製造方法を提供すること。

【解決手段】半導体基板1上に形成され、P型不純物が導入されたゲート電極を有するPchMOS型トランジスタ4と、前記PchMOS型トランジスタ4の上方を覆うように、前記半導体基板1上に形成された第1の水素バリア膜8と、前記第1の水素バリア膜8上に形成され、容量絶縁膜として強誘電体を用いた強誘電体キャパシタ7と、前記強誘電体キャパシタ7の上方および側方を覆い、前記強誘電体キャパシタ7の周縁部において前記第1の水素バリア膜8と接続する第2の水素バリア膜14とを備え、前記第1の水素バリア膜8は、シリコン元素、水素元素、およびシリコン元素よりも水素元素を脱離しにくい第3の元素を含む。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

強誘電体キャパシタの製造方法及び強誘電体キャパシタ

【課題】 強誘電体膜の上に、SrRuO3膜を形成し、その上に酸化イリジウム等の電極を従来の方法で形成した強誘電体キャパシタでは、目標とする大きさのQswを得ることが困難である。

【解決手段】 基板の上に、下部電極膜を形成する。下部電極膜の上に、強誘電体膜を形成する。強誘電体膜の上に、ペロブスカイト構造を持つ導電性酸化物からなるアモルファスの中間膜を形成する。中間膜の上に、Pt、Pd、Rh、Ir、Ru、Osからなる群より選択された少なくとも1つの金属の酸化物からなる第1の上部電極膜を形成する。第1の上部電極膜を形成した後、酸化性ガスを含む中で第1の熱処理を行うことにより、中間膜を結晶化させる。第1の熱処理の後、第1の上部電極膜の上に、第1の上部電極膜を形成するときの成長温度よりも低温で、Pt、Pd、Rh、Ir、Ru、Osからなる群より選択された少なくとも1つの金属の酸化物からなる第2の上部電極膜を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、キャパシタ誘電体膜の劣化を防止すること。

【解決手段】半導体基板の上方に絶縁膜27を形成する工程と、絶縁膜27の上に、下部電極31a、強誘電体材料を含むキャパシタ誘電体膜32a、及び上部電極33aを備えたキャパシタQを形成する工程と、キャパシタQの側面と上面に、スパッタ法で第2の保護絶縁膜43を形成する工程と、第2の保護絶縁膜43の上に、原子層堆積法により第3の保護絶縁膜44を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタにおける強誘電体層の結晶配向度を向上する半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、下部電極層41上にバッファ層44を形成する工程と、バッファ層44に対して、100体積%の濃度よりも低い酸素濃度の雰囲気下で且つ第1の温度で第1の熱処理を行った後、第1の温度よりも高い第2の温度で第2の熱処理を行う工程と、バッファ層44上に誘電体層42を形成する工程と、誘電体層42上に上部電極層43を形成する工程と、誘電体層42を熱処理して結晶化する工程と、を備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 上部電極の膜減りが生じ難いプレーナ型強誘電体キャパシタの製造方法を提供する。

【解決手段】 半導体基板の上に、下部電極層、強誘電体層、上部電極層を形成する。上部電極層の上に、第1の方向に並ぶハードマスクパターンを形成する。ハードマスクパターンをエッチングマスクとして、上部電極層及び強誘電体層をエッチングすることにより、上部電極及びキャパシタ誘電体膜を形成する。第1の方向に並んだハードマスクパターン及び下部電極層の一部を、連続したレジストパターンで覆う。レジストパターン及びキャパシタ誘電体膜をエッチングマスクとして、下部電極層をエッチングすることにより、下部電極を形成する。下部電極の、第1の方向に延在する両側の縁が、ハードマスクパターンの間の領域において、内側に向かって窪むように、レジストパターン及びハードマスクパターンの形状及び寸法が設定されている。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ特性の劣化を抑制し、かつ耐疲労特性を制御可能とする。

【解決手段】半導体基板10の上方に下部電極16を形成する工程と、下部電極16上に第1誘電体膜18を形成する工程と、酸化性ガスを含む雰囲気中で605℃以上の温度において熱処理することにより、第1誘電体膜18を結晶化する工程と、第1誘電体膜18上に第2誘電体膜20を形成する工程と、第2誘電体膜20を形成した後に熱処理を行なわず上部電極の少なくとも一部の層22を形成する工程と、酸化性ガスを含む雰囲気で熱処理することにより、第2誘電体膜20を結晶化する工程と、第2誘電体膜20および第1誘電体膜18をエッチングする工程と、エッチングする工程の後、側面が露出した状態において酸化性ガスを含む雰囲気中で550℃以上の温度で熱処理する工程と、を含み、第2誘電体膜20の膜厚は第1誘電体膜18の膜厚の30%以上である半導体装置の製造方法。

(もっと読む)

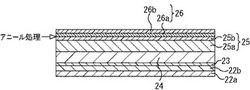

半導体装置及びその製造方法

【課題】薄膜化しても強誘電体膜の特性を十分に引き出すことができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の上方に、下部電極膜を形成した後、この下部電極膜上に、強誘電体膜10を形成する。次に、強誘電体膜10上に、上部電極膜11を形成する。但し、上部電極膜11を形成する際には、強誘電体膜10上に、成膜の時点で結晶化した微結晶を含むIrOx膜11bを形成した後に、柱状晶を含むIrOx膜11cを形成する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体膜の表面をレジストに曝すことなく、特性が異なる複数のキャパシタを有する半導体装置を製造する。

【解決手段】半導体装置の製造方法は、基板上方に絶縁膜を形成する工程、絶縁膜上方に下部電極層を形成する工程、下部電極層上に強誘電体膜を形成する工程、強誘電体膜上に第1上部電極層を形成する工程、第1上部電極層上に、第1領域を覆う第1レジストを形成する工程、第1レジストをマスクとしてエッチングを行うことにより、第2領域の第1上部電極層を除去するとともに、第2領域の強誘電体膜を削る工程、第1領域の第1上部電極層上及び第1領域以外の強誘電体膜上に、第2上部電極層を形成する工程、第1領域及び第2領域に第2レジストを形成する工程、第2レジストをマスクとして第1上部電極層、第2上部電極層、強誘電体膜及び下部電極層をエッチングし、第1のキャパシタ及び第2のキャパシタを形成する工程、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタ及び常誘電体キャパシタの両方を有する半導体装置を比較的少ない工程で製造できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板110にトランジスタ等を形成した後、メモリセル形成領域及びロジック回路形成領域にそれぞれ強誘電体膜127を電極126a,128aで挟んだ構造の強誘電体キャパシタを形成する。その後、強誘電体キャパシタを覆う層間絶縁膜131を形成し、更にその上にアルミナからなる保護膜132を形成する。そして、ロジック回路形成領域の保護膜132を除去する。これにより、半導体装置の製造工程が完了するまでの間にロジック回路形成領域の強誘電体膜127に水素及び水分が侵入して強誘電体特性が劣化し、強誘電体キャパシタが常誘電体キャパシタとなる。一方、メモリセル形成領域の強誘電体キャパシタは、保護膜132により強誘電体特性が保持される。

(もっと読む)

半導体装置及びその製造方法

【課題】下部電極がビット線の上に跨って形成されている場合においても、強誘電体膜の分極量が低下せず、安定した強誘電体キャパシタ特性を確保した半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板100の上に形成されたトランジスタ200と、基板100の上に形成されトランジスタ200を覆う第1の層間絶縁膜102と、第1の層間絶縁膜102に埋め込まれたビット線111と、第1の層間絶縁膜102の上に形成され、ビット線111を覆う絶縁性の第1の下部水素バリア膜131と、第1の下部水素バリア膜131の上に形成された強誘電体キャパシタ250とを備えている。強誘電体キャパシタ250は、下部電極251を有し、下部電極251は、ビット線111と重なり合う位置に形成され且つ上面が平坦である。

(もっと読む)

半導体装置の製造方法

【課題】後工程のダメージがなく、優れた特性を有する強誘電体キャパシタを提供する。

【解決手段】実施形態に係わる半導体装置の製造方法は、半導体基板の上方に、誘電体膜を下部電極と上部電極とで挟んでなるキャパシタ(200,300,400)を形成する第1の工程と、O3とTEOSを原料としたCVD法により、キャパシタ(200,300,400)を覆う酸化膜(122,125,128)を形成する第2の工程と、ALD法により、酸化膜(122,125,128)上に保護膜としてのAl2O3(123,126,129)膜を形成する第3の工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの分極特性を向上させつつ、MgO膜の還元を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、スイッチングトランジスタ301と、第1及び第2の拡散層1211,1212と、層間絶縁膜131と、MgO膜141と、MgO膜上に形成された下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201と、上部電極213上に形成された第1のプラグ171と、第1の拡散層上に形成された第2のプラグ172と、第2の拡散層上に形成され、下部電極211と第2の拡散層とを電気的に導通させている第3のプラグ173とを備え、第3のプラグ173は、側面及び底面を形成するバリアメタル層181と、バリアメタル層181上に形成されたプラグ材層182とを含み、バリアメタル層181は、MgO膜141とプラグ材層182との間に介在している。

(もっと読む)

21 - 40 / 791

[ Back to top ]